ROM所存數據穩定,斷電后所存數據也不會改變;其結構較簡單,讀出較方便,因而常用于存儲各種固定程序和數據。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601886 -

ROM

+關注

關注

4文章

562瀏覽量

85676 -

IP核

+關注

關注

4文章

326瀏覽量

49430

發布評論請先 登錄

相關推薦

FPGA IP核的相關問題

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源

發表于 01-10 17:19

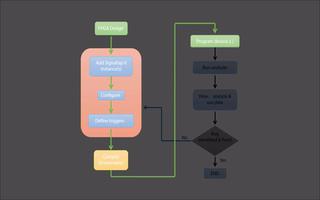

【鋯石A4 FPGA試用體驗】IP核之ROM(二)創建ROM IP核

前面建好了mif文件,下面就要創建ROM IP核了。首先,我們新建一個工程。菜單欄:Tools --> MegaWizardPlug-InManager ,點擊“Next”選擇ROM的

發表于 09-25 09:38

【鋯石科技】很好的FPGA入門培訓視頻-《HELLO FPGA》課程(免費下載)

02集: Verilog的關鍵問題解惑軟件工具篇:第01集: Quartus軟件使用講解第02集: ModelSim

發表于 03-15 15:30

FPGA零基礎學習:IP CORE 之 ROM設計

,學習FPGA設計方法及設計思想的同時,實操結合各類操作軟件,會讓你在技術學習道路上無比的順暢,告別技術學習小BUG卡破腦殼,告別目前忽悠性的培訓誘導,真正的去學習去實戰應用。話不多說,上貨。 IP

發表于 03-13 15:46

IP CORE 之 ROM 設計- ISE 操作工具

不多說,上貨。IP CORE 之 ROM 設計- ISE 操作工具本篇實現基于叁芯智能科技的SANXIN -B02 FPGA開發板,如有入手

發表于 04-07 20:09

FPGA之軟件工具篇:PLL IP核的使用講解

該篇不僅講解了如何使用Quartus II軟件、ModelSim和SignalTap II軟件,還講解了PLL、

FPGA之軟核演練篇:內置IP核之Interval Timer的應用實戰講解

軟核演練篇包含了哪些內容:該篇以什么是軟核、什么是Qsys、如何構建一個Qsys系統為切入點,在該基礎上進一步介紹了Nios II處理器的體系結構、Qsys豐富多彩的內置

FPGA之軟核演練篇:內置IP核之Interval Timer的理論原理講解

軟核演練篇包含了哪些內容:該篇以什么是軟核、什么是Qsys、如何構建一個Qsys系統為切入點,在該基礎上進一步介紹了Nios II處理器的體系結構、Qsys豐富多彩的內置

FPGA之軟核演練篇:內置IP核之System ID的講解

軟核演練篇包含了哪些內容:該篇以什么是軟核、什么是Qsys、如何構建一個Qsys系統為切入點,在該基礎上進一步介紹了Nios II處理器的體系結構、Qsys豐富多彩的內置

FPGA之軟件工具篇:ROM IP核的使用講解

FPGA之軟件工具篇:ROM IP核的使用講解

評論