聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

處理器

+關(guān)注

關(guān)注

68文章

19165瀏覽量

229130 -

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601858 -

邏輯

+關(guān)注

關(guān)注

2文章

832瀏覽量

29449

發(fā)布評論請先 登錄

相關(guān)推薦

浮點處理器相對于定點處理器有何不同

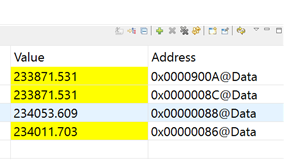

對程序做出改動。浮點處理器相對于定點處理器有如下好處: 編程更簡單 性能更優(yōu),比如除法,開方,F(xiàn)FT和IIR濾波等算法運算效率更高。 程序魯棒性更強。 一、IEEE754格式的浮點數(shù)

FPGA實現(xiàn)高速FFT處理器的設(shè)計

FPGA實現(xiàn)高速FFT處理器的設(shè)計介紹了采用Xilinx公司的Virtex - II系列FPGA設(shè)計高速FFT處理器的實現(xiàn)方法及技巧。充分利用Virtex - II芯片的硬件資源,減少

發(fā)表于 08-12 11:49

【FPGA干貨分享六】基于FPGA協(xié)處理器的算法加速的實現(xiàn)

。沒有通用的協(xié)處理器庫,即使是存在這樣的庫,將依然難以簡單地將協(xié)處理器與一個CPU(例如Pentium 4)連接。Xilinx Virtex-4 FX FPGA擁有一個或兩個Power

發(fā)表于 02-02 14:18

基于FPGA分布式算法的低通FIR濾波器該怎么設(shè)計?

傳統(tǒng)數(shù)字濾波器硬件的實現(xiàn)主要采用專用集成電路(ASIC)和數(shù)字信號處理器(DSP)來實現(xiàn)。FPGA內(nèi)部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結(jié)構(gòu),這種

發(fā)表于 08-29 06:43

基于并行分布式算法的濾波器怎么實現(xiàn)?

傳統(tǒng)數(shù)字濾波器硬件的實現(xiàn)主要采用專用集成電路(ASIC)和數(shù)字信號處理器(DSP)來實現(xiàn)。FPGA內(nèi)部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結(jié)構(gòu),這種

發(fā)表于 10-22 07:14

3GPP R4相對于R99的優(yōu)勢

3GPP R4相對于R99的優(yōu)勢

相對于傳統(tǒng)電路交換網(wǎng)絡(luò),軟交換網(wǎng)絡(luò)可以實現(xiàn)更簡單的目標網(wǎng)絡(luò)結(jié)構(gòu),主要是從節(jié)約運營成本、易于維護和保

發(fā)表于 06-13 22:27

?1139次閱讀

微處理器系統(tǒng)中連接簡單的被動串行配置方法和被動并行異步配置方法

成本。微處理器根據(jù)不同的程序應(yīng)用,采用不同的配置數(shù)據(jù)對FPGA進行配置,使FPGA實現(xiàn)與該應(yīng)用有關(guān)的特定功能。詳細介紹了微處理器系統(tǒng)中連接簡單

發(fā)表于 11-06 11:10

?1次下載

基于FPGA處理器的C編譯指令

Vviado-HLS基于Xilinx FPGA對C的解析,綜合原理。Vivado-HLS FPGA并行與處理器架構(gòu) 與處理器架構(gòu)相比,

發(fā)表于 11-18 12:23

?2669次閱讀

FPGA相對于CPU和GPU而言有著比較明顯的優(yōu)勢

FPGA相對于CPU和GPU,在進行感知處理等簡單重復(fù)的任務(wù)的時候的優(yōu)勢很明顯,按照現(xiàn)在的趨勢發(fā)展下去,FPGA或許會在未來取代機器人開發(fā)中

發(fā)表于 12-20 14:39

?2546次閱讀

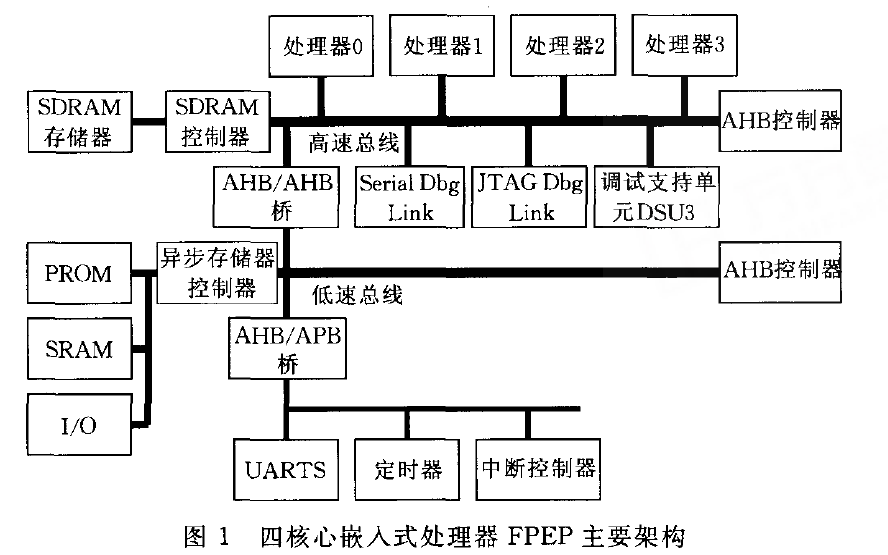

如何使用FPGA實現(xiàn)嵌入式多核處理器及SUSAN算法并行化

出了四核心嵌入式并行處理器FPEP的結(jié)構(gòu)設(shè)計并建立了FPGA驗證平臺.為了對多核處理器平臺性能進行評測,提出了基于OpenMP的3種可行的圖像處理

發(fā)表于 02-03 16:26

?8次下載

獨立BAW振蕩器相對于石英晶體振蕩器的優(yōu)勢

電子發(fā)燒友網(wǎng)站提供《獨立BAW振蕩器相對于石英晶體振蕩器的優(yōu)勢.pdf》資料免費下載

發(fā)表于 08-27 11:14

?0次下載

獨立BAW振蕩器-相對于石英振蕩器的優(yōu)勢

電子發(fā)燒友網(wǎng)站提供《獨立BAW振蕩器-相對于石英振蕩器的優(yōu)勢.pdf》資料免費下載

發(fā)表于 09-09 14:41

?0次下載

FPGA簡單入門和邏輯塊與相對于處理器的并行操作

FPGA簡單入門和邏輯塊與相對于處理器的并行操作

評論