SDRAM在計(jì)算機(jī)中被廣泛使用,從起初的SDRAM到之后一代的DDR(或稱(chēng)DDR1),然后是DDR2和DDR3進(jìn)入大眾市場(chǎng),2015年開(kāi)始DDR4進(jìn)入消費(fèi)市場(chǎng)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

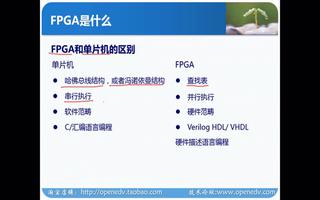

FPGA

+關(guān)注

關(guān)注

1626文章

21670瀏覽量

601875 -

SDRAM

+關(guān)注

關(guān)注

7文章

422瀏覽量

55160 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7424瀏覽量

87719

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【正點(diǎn)原子FPGA連載】第十二章 動(dòng)態(tài)數(shù)碼管顯示實(shí)驗(yàn)

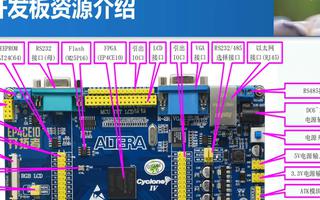

`1)實(shí)驗(yàn)平臺(tái):正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板2)平臺(tái)購(gòu)買(mǎi)地址:https://item.taobao.com/item.htm?id=579

發(fā)表于 06-15 22:54

正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板資料連載第三十三章SDRAM讀寫(xiě)測(cè)試

1)實(shí)驗(yàn)平臺(tái):正點(diǎn)原子開(kāi)拓者FPGA 開(kāi)發(fā)板2)摘自《開(kāi)拓者

發(fā)表于 08-17 15:25

正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板資料連載第三十四章 錄音機(jī)實(shí)驗(yàn)

1)實(shí)驗(yàn)平臺(tái):正點(diǎn)原子開(kāi)拓者FPGA 開(kāi)發(fā)板2)摘自《開(kāi)拓者

發(fā)表于 08-17 15:27

正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板資料連載第四十章 SD卡圖片顯示實(shí)驗(yàn)

1)實(shí)驗(yàn)平臺(tái):正點(diǎn)原子開(kāi)拓者FPGA 開(kāi)發(fā)板2)摘自《開(kāi)拓者

發(fā)表于 08-19 17:41

正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板資料連載第四十一章 SD卡圖片顯示實(shí)驗(yàn)

1)實(shí)驗(yàn)平臺(tái):正點(diǎn)原子開(kāi)拓者FPGA 開(kāi)發(fā)板2)摘自《開(kāi)拓者

發(fā)表于 08-24 11:21

正點(diǎn)開(kāi)拓者FPGA開(kāi)發(fā)板使用問(wèn)題

求問(wèn)各位大佬,剛剛?cè)腴T(mén)正點(diǎn)開(kāi)拓者FPGA開(kāi)發(fā)板,用板載pcf8591采集信號(hào)發(fā)生器單一頻率正弦波,再用ip核做fft,結(jié)果和matlab上fft不一樣,請(qǐng)問(wèn)是怎么回事呢?

發(fā)表于 01-04 09:34

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:PIO IRQ

該課程是正點(diǎn)原子團(tuán)隊(duì)編寫(xiě),詳細(xì)講解了quartus中的qsys。也可以從我頭像點(diǎn)進(jìn)去看FPGA verilog相關(guān)的視頻。

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:Hello World

該課程是正點(diǎn)原子團(tuán)隊(duì)編寫(xiě),詳細(xì)講解了quartus中的qsys。也可以從我頭像點(diǎn)進(jìn)去看FPGA verilog相關(guān)的視頻。

正點(diǎn)原子開(kāi)拓者FPGA:SDRAM讀寫(xiě)測(cè)試實(shí)驗(yàn)(3)

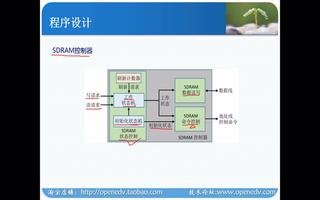

SDRAM有一個(gè)同步接口,在響應(yīng)控制輸入前會(huì)等待一個(gè)時(shí)鐘信號(hào),這樣就能和計(jì)算機(jī)的系統(tǒng)總線同步。時(shí)鐘被用來(lái)驅(qū)動(dòng)一個(gè)有限狀態(tài)機(jī),對(duì)進(jìn)入的指令進(jìn)行管線(Pipeline)操作。這使得SDRAM與沒(méi)有同步接口的異步DRAM(asynchronous DRAM)相比,可以有一個(gè)更復(fù)

正點(diǎn)原子開(kāi)拓者FPGA:SDRAM讀寫(xiě)測(cè)試實(shí)驗(yàn)(2)

SDRAM從發(fā)展到現(xiàn)在已經(jīng)經(jīng)歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDR

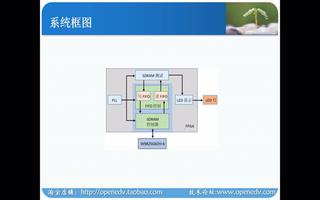

正點(diǎn)原子開(kāi)拓者FPGA:SDRAM讀寫(xiě)測(cè)試實(shí)驗(yàn)

正點(diǎn)原子開(kāi)拓者FPGA:SDRAM讀寫(xiě)測(cè)試實(shí)驗(yàn)

評(píng)論