3G提高了通信速度,4G改變了我們的生活,5G時代則因為技術的革命性,整個社會形態與商業形態都被深刻影響,對于芯片封裝測試領域同樣也帶來了許多新的技術革新......

11月上旬,2018中國集成電路產業促進大會的5G通信芯片主題論壇上,Qorvo亞太區客戶質量工程總監周寅便用示例詳細介紹了傳統的芯片封裝測試工藝流程與5G芯片封裝技術演進路線。

Qorvo亞太區客戶質量工程總監周寅發表演講

Qorvo是全球少數能夠整合所有射頻全方位解決方案的公司,主要業務領域包括移動終端、基站芯片和航空航天等。工欲善其事,必先利其器,兩年前新投入運營的德州工廠是Qorvo全球范圍內最大的組裝、封裝和測試運營中心,補充了Qorvo現有的北京制造業務, 并與Qorvo北京工廠組成Qorvo中國制造中心,共同合力支撐全球的生產運營。

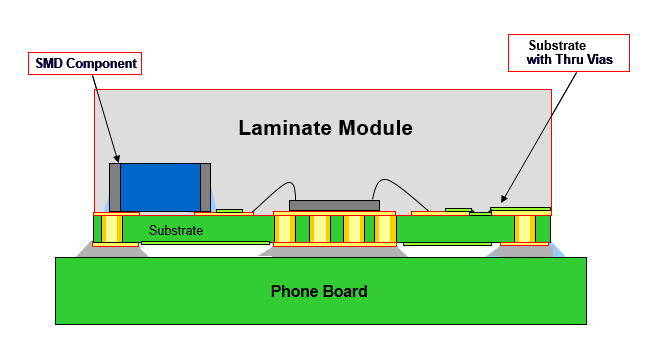

這一種很典型的十幾年前一種基于基板(Substrate)的層壓封裝結構模型(Laminate Module Package),它大致上可分為幾個步驟:首先在基板表面貼裝SMT的被動元件,也就是我們平時常用到的電容、電感等。第二步貼主動元件,就是中間部分的晶圓,它實現芯片的大部分電路功能。這兩步做完之后,需要連接電路,以前一般用金線、銅線、鋁線進行連接,以實現芯片的電路功能。做完這三步后,芯片的功能便基本實現了,接下來還要用一些材料,比如陶瓷或聚脂,對芯片塑封以確保可靠性。這就是封裝最基本、最簡單的一套流程。

1晶圓研磨和切割工藝

2倒裝芯片貼裝工藝

在芯片里貼被動元件與在電路板上貼元件類似,刷上焊錫膏,把被動元件焊接到基板上面,實現它的連接功能,唯一的區別只是它用到的SMD元件會更小。今后的趨勢是分立元件會更多地集成在芯片里,外圍不會有太多元件。

作為功率放大的器件,需要高功率的、高帶寬的材料,比如砷化鎵、氮化鎵,也需要一些低頻的功率器件,共同做在晶圓上。每一片晶圓,可能包含許多直徑大概0.1到0.5毫米的小晶片,我們稱之為die。對晶圓的專用機器會使用環氧樹脂將晶圓粘接到目標表面,令目標與晶圓進行導電導熱的連接。環氧樹脂材料對die和die之間的距離有一定限制,隨著晶圓越做越小,也可能用到一些其它新材料,例如導電薄膜,從而使芯片的集成度提高。

3引線鍵合工藝

焊線(Wire Bond)將芯片上的電路連接起來。現在焊線的方式會用到一個mil(千分之一英寸,約0.0254mm)的金線,隨著成本控制和其它一些生產考量,也會用到合金、鋁線或其它一些焊線材料。不同的die之間互相用這種線進行連接。

雖然采用焊線的芯片,基板設計靈活度較高,但焊線制約了封裝的尺寸。隨著頻段越來越寬、頻譜越來越復雜,焊線技術已不太適用消費電子產品,尤其是可穿戴設備。現在常用銅柱凸點倒裝的方式實現芯片內的連接。

最終我們利用環氧樹脂、二氧化硅或其它材料對芯片進行塑封,以實現產品的可靠性,比如防潮、防震這些功能。塑封完成后會在芯片上面激光打碼,留下一些基本信息,通過這些信息就可以追溯芯片的生產記錄。打碼后會將整版芯片切割成單個芯片包裝。

5切割工藝

6檢驗

包括磁阻檢測、整板測試、干式烘焙測試、晶圓探測等。

//射頻芯片封裝模式的不斷演進//

縱觀芯片封裝模式的演進,5-10年前器件的封裝更多的是用Wire Bond間隔的模式,通過晶片貼到類似于傳統意義的PCB的基板上,達到厚度更薄密度更高。又或者是Wire Bond間隔的多個晶片及表面貼裝元件的混裝方式,能夠把wafer的其它一些功能,比如控制模塊、電源管理模塊、filter,包括開關,全部封裝在里邊。

5年前的封裝模式現在很多主流的手機和基站產品仍在使用,更多用的是倒貼的方式。接下來的封裝,集成度會越來越高。系統級封裝(System In a Package)可將多種功能芯片,包括處理器、存儲器等功能芯片集成在一個封裝內,從而實現一個基本完整的功能。

此外,5G推動芯片向更高集成度、更小尺寸和更高的性能發展,新的封裝技術要求設計和制造能力的不斷提升。周寅最后指出,QorvoRF Fusion 射頻前端模塊,實現了功能集成上的突破,可將中頻/高頻模塊整合到一起。通過采用 Qorvo 獨有的內核功能組合,可提升性能,降低功耗和解決方案整體的尺寸大小,同時提供更高的載波聚合容量,滿足5G時代智能手機制造商日益增長的全球覆蓋需求。

-

芯片

+關注

關注

453文章

50407瀏覽量

421849 -

晶圓

+關注

關注

52文章

4842瀏覽量

127803 -

5G

+關注

關注

1353文章

48368瀏覽量

563391

原文標題:行業 | 讀懂了傳統芯片封裝測試工藝,5G時代又有哪些新的技術革新挑戰?

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

5G推動芯片性能發展 封裝技術和制造能力不斷提升

5G推動芯片性能發展 封裝技術和制造能力不斷提升

評論