在功率電子中,根據特定應用,已經成功地采用了幾種脈沖寬度調制(PWM)方案。大多數傳統PWM方案(本質上是確定性的)生成預定的諧波含量。這可能會在實際應用中產生許多問題,如噪聲、無線電干擾和機械振動。在需要減輕對環境和其他設備的干擾的應用中,例如工業電機驅動器、牽引驅動器、電動汽車,傳統的PWM方案因自身原因不能高效地運行,需要添加如電磁干擾(EMI)濾波器等附加設備。有一種方法可以應對這些問題,就是增加傳統PWM方案的開關頻率,即> 18kHz。不過,這會導致開關損耗顯著增加。在這種應用中,已經發現隨機脈沖寬度調制(RPWM)可以有效地減輕這些問題,且不用顯著增加開關頻率。

在RPWM中,每個開關脈沖的寬度隨機變化。這導致諧波簇在很大范圍內擴散,從而減小了單獨濾波器的尺寸,或完全避免在某些應用中使用濾波器。RPWM技術已成功用于許多功率電子應用中,例如 在需要檢查噪聲的工業電機控制驅動器中。

通常,使用DSP和FPGA實現用于復雜商用系統的高頻PWM和RPWM信號。不過,這些器件更通用、功能更強大、且更靈活,自然也就比較貴。使用低成本的Dialog CMIC可以滿足RPWM生成所需的相似精度和高頻時序要求。許多合適的RPWM方案,尤其是開環應用,可以用Dialog CMIC來實現。因此,嵌入式DSP、MCU或FPGA的顯式編程或編碼可以由GreenPAK? designer中提供的簡單接口所取代。此外,整個控制電路的尺寸也會顯著減小。

有幾種方法可以為三相逆變器應用生成RPWM。此應用筆記中,我們介紹了一種合適的RPWM技術,它可以使用現成的GreenPAK CMIC資源來實現。RPWM技術使用雙矩陣CMIC SLG46620實現。還提供了適當的理論建議和實驗結果,包括輸出電壓波形及其諧波含量,可以證明所建議的策略是合理的。

建議的RPWM方案

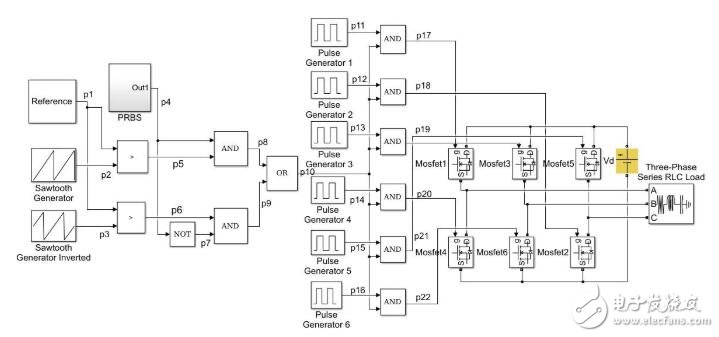

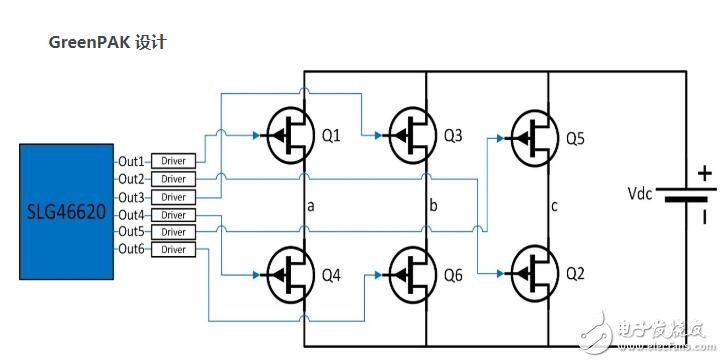

驅動三相逆變器的RPWM方案的框圖如圖1所示。

圖1:建議方案的框圖

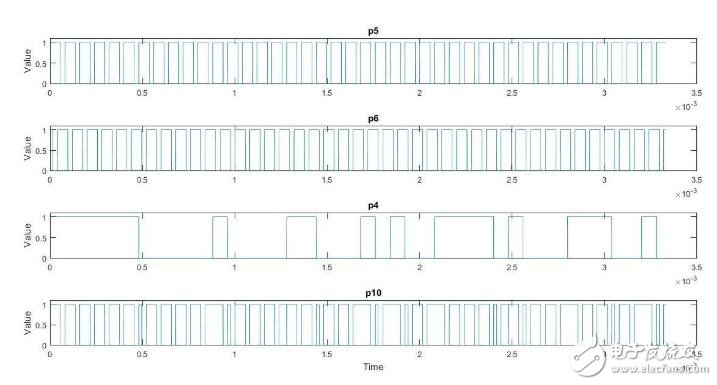

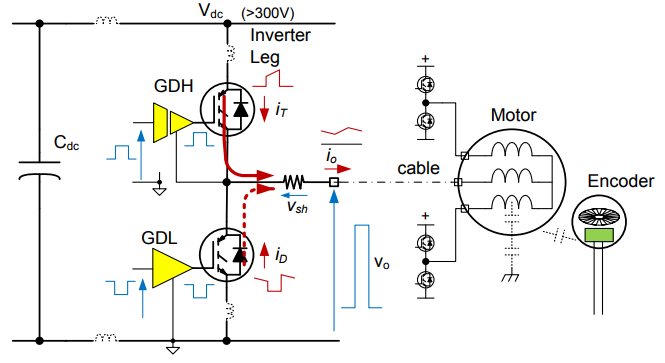

兩個鋸齒信號,標記為p2和p3(值范圍:0-1),相位相差180°C,與恒定值p1(值范圍:0-1)進行比較,得出標記為p5和p6的不同類型的脈沖。p5和p6脈沖的波形如圖2和圖3所示。采用圖4所示波形的二進制偽隨機數發生器(標記為p4),使用上面框圖中所示的邏輯運算符從信號p5和p6中隨機選擇一個脈沖。這會生成一系列脈沖p10,如圖5所示。信號p10通過AND門,同樣的還有脈沖發生器1到6所生成的10ms長脈沖,標記為p11、p12、p13、p14、p15和p16。請注意,對于完整的180?C導通模式,脈沖發生器的輸出脈沖相對于彼此有60?C的相位差。最后,在AND操作之后,信號p17、p18、p19、p20、p21和p22成為三相逆變器的功率級中采用的功率開關的柵極驅動信號。

根據施加的柵極信號接通和斷開開關(通常是MOSFET或IGBT),以獲得逆變器輸出端的三相平衡電壓波形。

圖2:RPWM方案中幾個階段的模擬信號波形

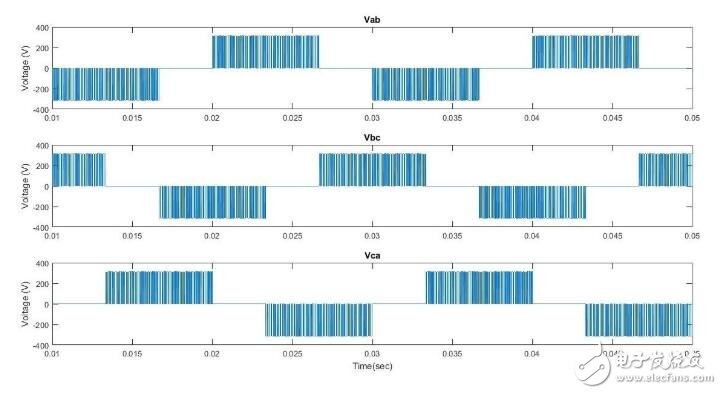

在Matlab/Simulink環境中對50 Hz(基波)RPWM三相逆變器系統進行仿真,相間輸出波形如圖3所示。輸出電壓波形有效地由隨機信號p10調制,并實現120 ?C 的相移。

圖3:模擬的輸出相間電壓波形

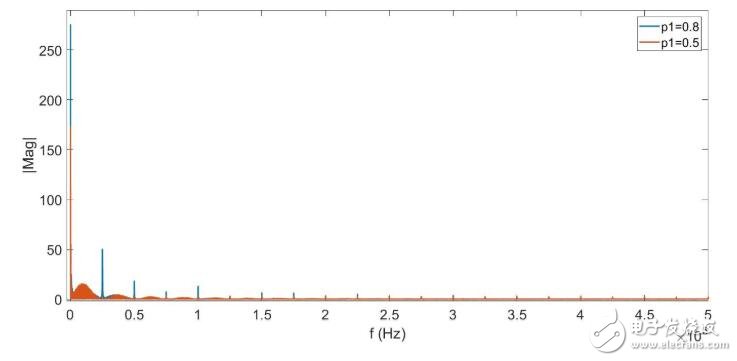

參考值的選擇

參考信號p1提供了一種根據主觀聲響應控制特定應用的逆變器輸出的頻譜內容的方法。從1到0.5的參考值變化使頻譜內容變平,從而減輕了開關頻率倍數處的尖峰。不過,這也降低了信號基波分量的幅度。圖4顯示了對于Vdc = 312V和載波頻率= 12.5kHz,輸出相間電壓的頻譜內容如何在參考值從p1 = 0.8減小到p1 = 0.5時發生變化。

圖4:頻譜隨參考值的變化而變化

不推薦將參考值進一步降低到0.5以下,因為開關頻率的倍數尖峰開始增多,而且基波分量也會降低。

GreenPAK設計

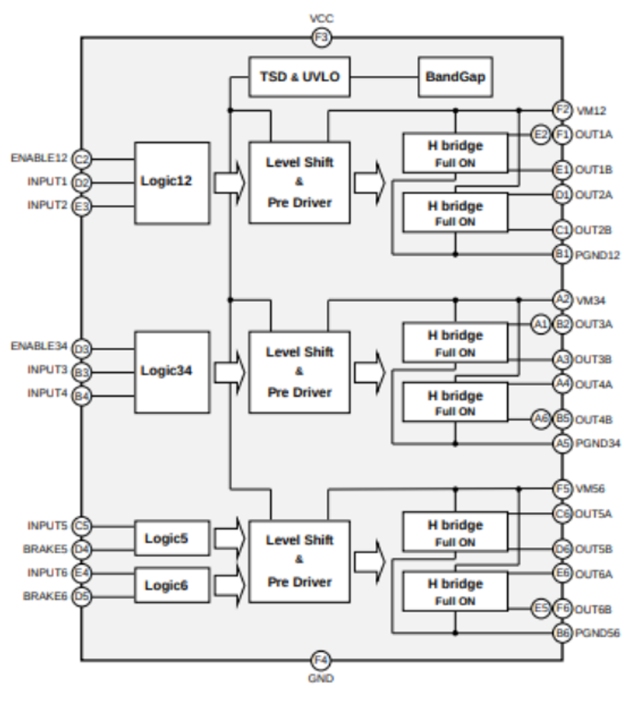

圖5:SLG46620在RPWM方案中的角色

圖5顯示了Dialog CMIC SLG46620如何在整個方案中發揮功能。CMIC的基本操作是生成隨機PWM調制信號,該信號施加在逆變器功率級中使用的開關裝置的柵極端子處。

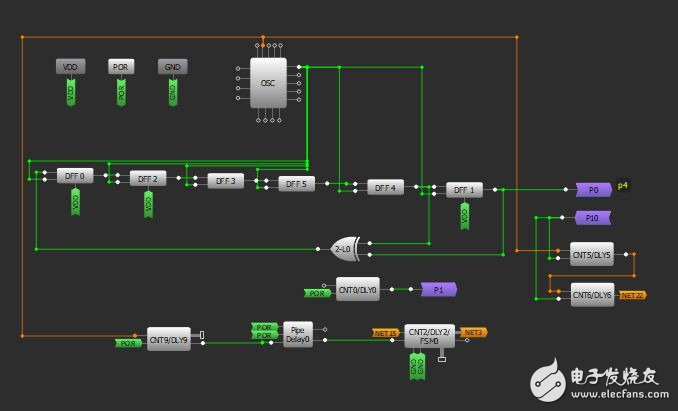

圖6:設計矩陣0

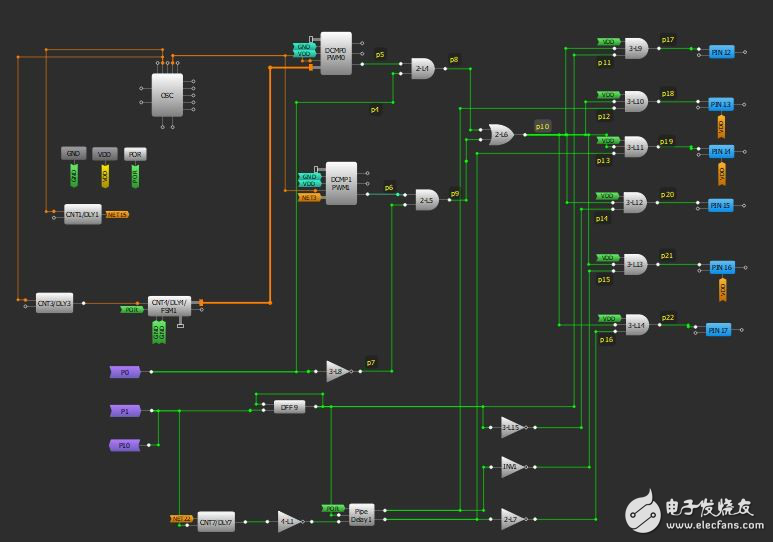

圖7:設計矩陣1

逆變器輸出電壓的基頻選擇為50 Hz。選擇SLG46220是因為它提供了足夠的資源來執行預期的設計。矩陣0和1設計分別如圖6和圖7所示。在矩陣0中,通過以級聯(concatenated)方式連接DFF,并在反饋環路中使用異或門生成偽隨機信號(PBRS)P0,如圖6所示。DFF由來自振蕩器模塊OUT0的12.5kHz時鐘信號驅動。

對于鋸齒載波信號的生成,建議使用FSM塊。在UP = 0的設定模式下配置的FSM0和FSM1分別由計數器CNT1/DLY1和CNT3/DLY3饋送,生成頻率為1.6875MHz的脈沖。兩個FSM中的計數器值設置為134(輸出周期80 us),以實現所需的12.5 kHz分立鋸齒信號。為了在兩個鋸齒信號之間實現180 °C相移,在FSM1使用由CNT9/DLY9饋送的管道延遲40μs后,啟用FSM0。

兩個鋸齒波載波信號通過FSM0和FSM1的Q字節輸出端口饋入DCMP0和DCMP1,與恒定參考信號(在寄存器DCMP0和DCMP1內配置)進行比較,如圖7所示。由于計數器運行達到值134,參考值相對于134給出,例如67等于0.5(67/134)的值。兩個DCMP(p5和p6)的輸出進一步與來自LFSR(p4)的輸出信號及其反相值(p7)一起傳遞到兩個AND門。向或門饋入這些AND門的輸出,以隨機獲得DCMP的兩個輸出之一。或門的輸出(p10)還進一步用于調制逆變器的驅動信號。

計數器CNT0 / DLY0被配置為生成周期為10ms的脈沖,以便生成50Hz頻率(基波)的輸出電壓。這些脈沖被饋送到以反相模式配置的DFF,輸出反饋到輸入,以生成50Hz方波脈沖序列。為確保標記為p11至p16的輸出脈沖相位相差60 °C,建議使用管道延遲模塊。將計數器CNT5/DLY5、CNT6/DLY6和CNT7/DLY7級聯以提供周期為3.33ms的脈沖。這些脈沖通過非門饋入管道延遲,因為管道延遲通過計算輸入上升沿的數量產生延遲,而計數器通過復位輸入復位為0,生成重復的下降沿,周期為3.33 ms。輸出0和1的管道延遲分別為輸入脈沖提供3.33 ms和6.66 ms的時間延遲。三個信號,即管道延遲的輸入和兩個延遲輸出,被進一步反相,以提供彼此相移60°的共6個脈沖(p11-p16)。這些50 Hz、60?C相移脈沖與隨機脈沖序列(p10)一起進一步被傳遞到AND門,為3相逆變器提供最終驅動信號。

實驗結果

我們開發了圖8中描繪的硬件原型,以實驗驗證所提出的RPWM方案。為確保同一支路中的兩個開關不會同時打開,我們在硬件中生成了一個死區。

圖8:原型硬件

圖9:放大的相間輸出電壓波形

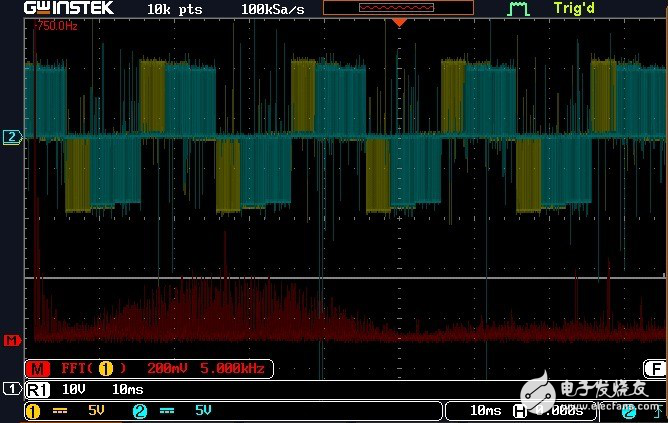

圖10:參考值為0.8的Vab、Vac和FFT

圖11:參考值為0.5的Vab、Vac和FFT

圖9顯示了輸出相間電壓的放大波形。很明顯,波形是根據需要隨機調制的。

在圖10中,顯示了輸出相間電壓信號Vab(黃色)和Vac(藍色)。此外,還顯示了參考值≈0.8(107/134)的Vab(紅色)的FFT圖。盡管頻譜中的擴展是明顯的,但是如理論所示,觀察到兩倍于開關頻率的尖峰,即25kHz。

圖11顯示了參考值= 0.5(67/134)時的輸出相間電壓信號Vab(黃色)和Vac(藍色)以及Vab(紅色)的FFT圖。可以看到頻譜變得更平坦,而且實現了顯著的擴散。

總結

可以使用不同的技術生成用于三相逆變器的RPWM信號,通常在工業應用中使用較貴的DSP和FPGA來實現期望的結果。在本應用筆記中,我們介紹了使用低成本Dialog SLG46620 CMIC實現針對三相逆變器應用的RPWM生成技術。通過恰當的模擬和實驗結果,已經確定所提出的技術是有效的,SLG46620 IC提供了足夠的資源來實現預期的結果。

-

電機控制

+關注

關注

3526文章

1857瀏覽量

268378 -

HRPWM

+關注

關注

0文章

3瀏覽量

3185

發布評論請先 登錄

相關推薦

RPWM技術在噪聲的工業電機控制驅動器中應用方案

RPWM技術在噪聲的工業電機控制驅動器中應用方案

評論