布爾代數(shù)如何使用布爾代數(shù)定律減少數(shù)字門數(shù)的例子

布爾代數(shù)和布爾代數(shù)定律可用于識別數(shù)字邏輯設(shè)計(jì)中不必要的邏輯門減少功耗和成本所需的門數(shù)。

我們在本節(jié)中已經(jīng)看到,數(shù)字邏輯功能可以定義并顯示為布爾代數(shù)表達(dá)式或邏輯門真值表。所以這里有一些例子說明我們?nèi)绾问褂貌紶柎鷶?shù)來簡化更大的數(shù)字邏輯電路。

布爾代數(shù)示例No1

構(gòu)造一個真值表以下電路中 C , D 和 Q 點(diǎn)的邏輯功能,并確定可用于替換整個電路的單個邏輯門。

首先觀察告訴我們該電路由2輸入 NAND 門,2輸入 EX-OR 門,最后輸出端為2輸入 EX-NOR 門。由于標(biāo)記 A 和 B 的電路只有2個輸入,因此輸入只能有4種可能的組合(2 2 )和它們是: 0-0 , 0-1 , 1-0 ,最后 1-1 。以表格形式繪制每個門的邏輯函數(shù)將為下面的整個邏輯電路提供以下真值表。

從上面的真值表中,列 C 表示由 NAND 門生成的輸出函數(shù),而列 D 表示輸出函數(shù)來自 Ex-OR 門。這兩個輸出表達(dá)式都將成為輸出端 Ex-NOR 門的輸入條件。

從真值表中可以看出的輸出當(dāng) A 或 B 中的任何一個輸入處于邏輯 1 時(shí),存在Q 。滿足此條件的唯一真值表是 OR 門。因此,整個上述電路只能用一個2輸入OR 門代替。

布爾代數(shù)示例No2

找到以下系統(tǒng)的布爾代數(shù)表達(dá)式。

系統(tǒng)由組成AND 門, NOR 門,最后是 OR 門。 AND 門的表達(dá)式為 A.B , NOR 門的表達(dá)式為 A + B 。這兩個表達(dá)式也是 OR 門的單獨(dú)輸入,定義為 A + B 。因此,最終輸出表達(dá)式如下:

系統(tǒng)的輸出為 Q =(AB) +( A + B ),但符號 A + B 與De Morgan的符號 A 。 B 相同,然后替換 A 。 B 到輸出表達(dá)式給出了 Q =(AB)+( A 。 B )的最終輸出符號,這是 Exclusive-NOR 門的布爾表示法,如上一節(jié)所示。

| 輸入 | 輸出 | |||

| A | B | C | D | Q |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 輸入 | 中間體 | 輸出 | ||

| B | A | AB | A + B | Q |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 1 |

然后,上面的整個電路可以只用一個 Exclusive-NOR 門代替,實(shí)際上 Exclusive-NOR 門由這些單獨(dú)的門組成函數(shù)。

布爾代數(shù)示例No3

查找以下系統(tǒng)的布爾代數(shù)表達(dá)式。

這個系統(tǒng)可能看起來比其他兩個系統(tǒng)要復(fù)雜得多,但邏輯電路只包含簡單的 AND , OR 和 NOT 連接在一起的門。

與前面的布爾示例一樣,我們可以通過依次寫下每個邏輯門功能的布爾符號來簡化電路為了給出 Q 輸出的最終表達(dá)式。

當(dāng)ALL門輸入在邏輯電平“1”處為高電平時(shí),3輸入 AND 門的輸出僅為邏輯“1”( ABC )。當(dāng)一個或兩個輸入 B 或 C 處于邏輯電平“0”時(shí),低 OR 門的輸出僅為“1”。當(dāng)輸入 A 為“1”且輸入 B 或時(shí),2輸入 AND 門的輸出為“1” C 為“0”。當(dāng)輸入 ABC 等于“1”或 A 等于“1”并且兩個輸入時(shí), Q 的輸出僅為“1” B 或 C 等于“0”, A.( B + C )。

使用“de Morgan定理”輸入 B 并輸入 C 取消,以便在 Q 處產(chǎn)生輸出,它們可以是邏輯“1”或邏輯“0”。然后,這只是輸入 A 作為在 Q 輸出所需的唯一輸入,如下表所示。

| 輸入 | 中間體 | 輸出 | ||||||

| C | B | A | ABC | B | C | B + C | A。( B + C ) | Q |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

然后我們可以看到上面的整個邏輯電路只能被標(biāo)記為“ A ”的單個輸入所取代,從而將六個獨(dú)立邏輯門的電路減少到只有一根電線,(或緩沖器) 。使用布爾代數(shù)的這種類型的電路分析可以非常強(qiáng)大并且可以快速識別數(shù)字邏輯設(shè)計(jì)中的任何不必要的邏輯門,從而減少所需的門數(shù),電路的功耗以及成本

-

布爾代數(shù)

+關(guān)注

關(guān)注

0文章

10瀏覽量

7860 -

數(shù)字邏輯

+關(guān)注

關(guān)注

0文章

73瀏覽量

16635

發(fā)布評論請先 登錄

相關(guān)推薦

邏輯代數(shù)基礎(chǔ)

為什么三個布爾按鈕不能正常停止和運(yùn)行呢

正反轉(zhuǎn)布爾,自動控制布爾,控制量這三個控件是從哪里來

怎么設(shè)置一個布爾的數(shù)組常量的布爾個數(shù)?

labview中如何實(shí)現(xiàn)三個事件互鎖?

三個小數(shù)求和,判斷等于1?為什么有的值行,有的值不行

求助:我想編寫一個三個布爾輸入控件,我想輸入000的時(shí)候,輸出1。

三個布爾開關(guān)相互獨(dú)立

關(guān)于代數(shù)攻擊中代數(shù)免疫的若干性質(zhì)分析

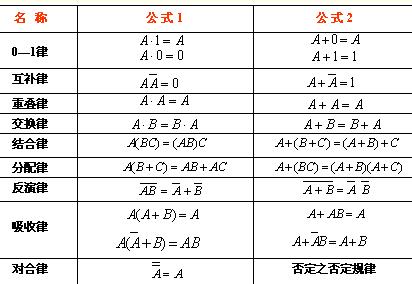

邏輯代數(shù)的基本定律和規(guī)則

布爾代數(shù),布爾代數(shù)是什么意思

布爾代數(shù)定律的描述

三個布爾代數(shù)示例說明

三個布爾代數(shù)示例說明

評論