在PCB印制電路板設計生產等過程中,傳輸線的信號損耗是板材應用性能的重要參數。信號損耗測試是印制電路板的信號完整性的重要表征手段之一。簡單分享一下我所了解的目前業界使用的幾種PCB傳輸線信號損耗測量方法的原理和相關應用,并分析了其優勢和限制。

印制電路板(PCB)信號完整性是近年來熱議的一個話題,國內已有很多的研究報道對PCB信號完整性的影響因素進行分析[1]-[4],但對信號損耗的測試技術的現狀介紹較為少見。

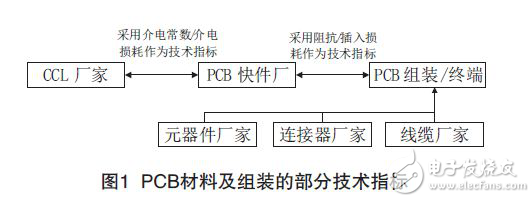

PCB傳輸線信號損耗來源為材料的導體損耗和介質損耗,同時也受到銅箔電阻、銅箔粗糙度、輻射損耗、阻抗不匹配、串擾等因素影響。在供應鏈上,覆銅板(CCL)廠家與PCB快件廠的驗收指標采用介電常數和介質損耗;而PCB快件廠與終端之間的指標通常采用阻抗和插入損耗,如圖1所示。

針對高速PCB設計和使用,如何快速、有效地測量PCB傳輸線信號損耗,對于PCB設計參數的設定和仿真調試和生產過程的控制具有重要意義。

2 PCB插入損耗測試技術的現狀

目前業界使用的PCB信號損耗測試方法從使用的儀器進行分類,可分為兩大類:基于時域或基于頻域。時域測試儀器為時域反射計(Time DomainReflectometry,簡稱TDR)或時域傳輸計(TimeDomain Transmission,簡稱TDT);頻域測試儀器為矢量網絡分析儀(Vector Network Analyzer,簡稱VNA)。在IPC-TM650試驗規范中,推薦了5種試驗方法用于PCB信號損耗的測試:頻域法、有效帶寬法、根脈沖能量法、短脈沖傳播法、單端TDR差分插入損耗法。

2.1 頻域法

頻域法(Frequency Domain Method)主要使用矢量網絡分析儀測量傳輸線的S參數,直接讀取插入損耗值,然后在特定頻率范圍內(如1 GHz ~ 5 GHz)用平均插入損耗的擬合斜率來衡量板材合格/不合格。

頻域法測量準確度的差異主要來自校準方式。根據校準方式的不同,可細分為SLOT(Short-Line-Open-Thru)、Multi-Line TRL(Thru-Reflect-Line)和Ecal(Electronic calibration)電子校準等方式。

SLOT通常被認為是標準的校準方法[5],校準模型共有12項誤差參數,SLOT方式的校準精度是由校準件所確定的,高精度的校準件由測量設備廠家提供,但校準件價格昂貴,而且一般只適用于同軸環境,校準耗時且隨著測量端數增加而幾何級增長。

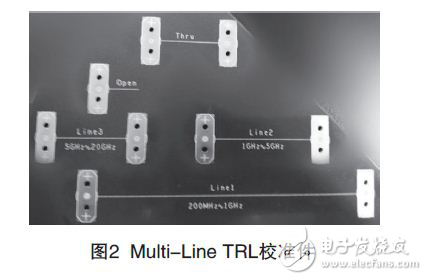

Multi-Line TRL方式主要用于非同軸的校準測量[6],根據用戶所使用的傳輸線的材料以及測試頻率來設計和制作TRL校準件,如圖2所示。盡管Multi-Line TRL相比SLOT設計和制造更為簡易,但是Multi-Line TRL方式校準耗時同樣隨著測量端數的增加而成幾何級增長。

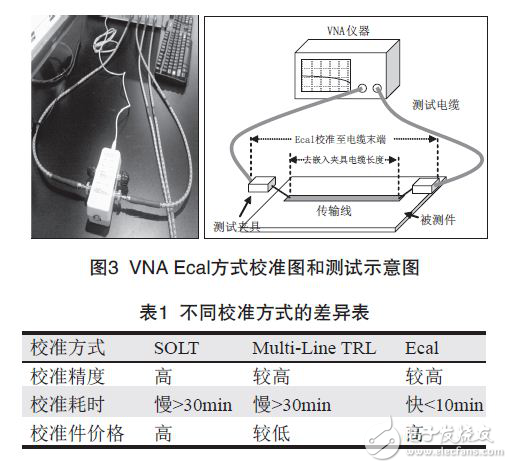

為了解決校準耗時的問題,測量設備廠家推出了Ecal電子校準方式[7],Ecal是一種傳遞標準,校準精度主要由原始校準件所確定,同時測試電纜的穩定性、測試夾具裝置的重復性和測試頻率的內插算法也對測試精度有影響。一般先用電子校準件將參考面校準至測試電纜末端,然后用去嵌入的方式,補償夾具的電纜長度。如圖3所示。

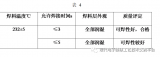

以獲得差分傳輸線的插入損耗為例,3種校準方式比較如表1所示。

根脈沖能量法

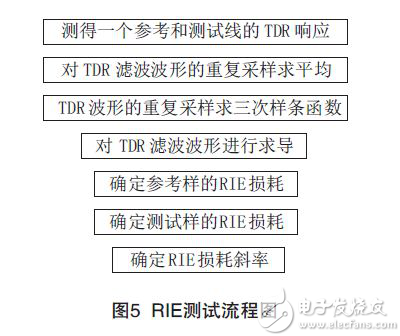

2.2根脈沖能量法(Root ImPulse Energy,簡稱RIE)通常使用TDR儀器分別獲得參考損耗線與測試傳輸線的TDR波形,然后對TDR波形進行信號處理。RIE測試流程如圖5所示:

2.3 有效帶寬法

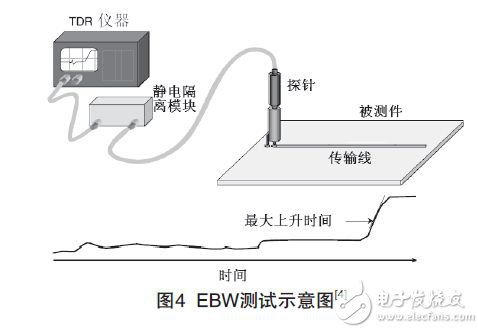

有效帶寬法(Effective Bandwidth,簡稱EBW)從嚴格意義來說是一個定性的傳輸線損耗α的測量,無法提供定量的插入損耗值,但是提供一個稱之為EBW的參數。有效帶寬法是通過TDR將特定上升時間的階躍信號發射到傳輸線上,測量TDR儀器和被測件連接后的上升時間的最大斜率,確定為損耗因子,單位MV/s.更確切地說,它確定的是一個相對的總損耗因子,可以用來識別損耗在面與面或層與層之間傳輸線的變化[8].由于最大斜率可以直接從儀器測得,有效帶寬法常用于印制電路板的批量生產測試。EBW測試示意圖如圖4所示

2.4 短脈沖傳播法

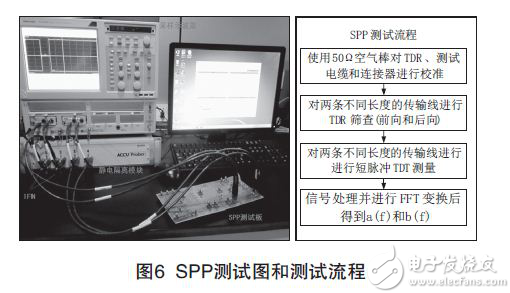

短脈沖傳播法(Short Pulse Propagation,簡稱SPP)測試原理為利用測量兩條不同長度的傳輸線,如30 mm和100 mm,通過測量這兩個傳輸線線長之間的差異來提取參數衰減系數 和相位常數 ,如圖6所示。使用這種方法可以將連接器、線纜、探針和示波器精度的影響降到最小。若使用高性能的TDR儀器和IFN(Impulse Forming Network),測試頻率可高達40 GHz.

2.5 單端TDR差分插入損耗法

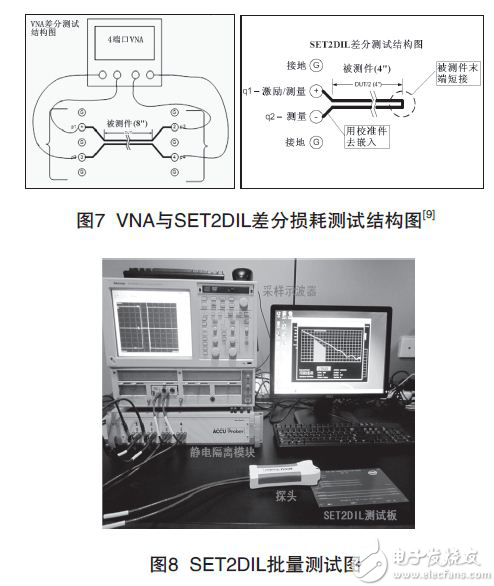

單端TDR差分插入損耗法(Single-Ended TDRto Differential Insertion Loss,簡稱SET2DIL)有別于采用4端口VNA的差分插損測試,該方法使用兩端口TDR儀器,將TDR階躍響應發射到差分傳輸線上,差分傳輸線末端短接,如圖7所示。SET2DIL法測量典型的測量頻率范圍為2 GHz ~ 12 GHz,測量準確度主要受測試電纜的時延不一致和被測件阻抗不匹配的影響。SET2DIL法優勢在于無需使用昂貴的4端口VNA及其校準件,被測件的傳輸線的長度僅為VNA方法的一半,校準件結構簡單,校準耗時也大幅度降低,非常適合用于PCB制造的批量測試,如圖8所示。

3 測試設備及測試結果

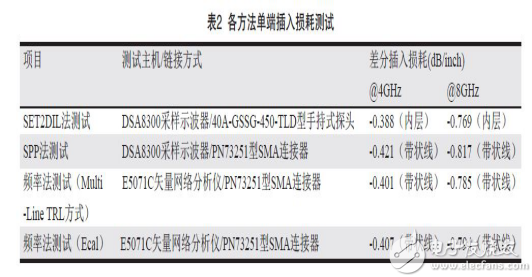

采用介電常數3.8、介質損耗0.008、RTF銅箔的CCL分別制作SET2DIL測試板、SPP測試板和Multi-Line TRL測試板;測試設備為DSA8300采樣示波器和E5071C矢量網絡分析儀;各方法差分插入損耗測試結果如表2所示。

這是印制電路板(PCB)目前業界使用的幾種PCB傳輸線信號損耗測量方法。由于采用的測試方法不同,測得插入損耗值也不一樣,測試結果不能直接做橫向對比,因此應根據各種技術方法的優勢和限制,并且結合自身的需求選擇合適的信號損耗測試技術來進行測試。

-

pcb

+關注

關注

4317文章

23006瀏覽量

396311 -

印制電路板圖

+關注

關注

0文章

3瀏覽量

2619

發布評論請先 登錄

相關推薦

滬電股份43億投建AI芯片配套高端印制電路板項目

如何提高PCB電路板抗干擾的能力

PCB 電路板材質全解析

X-ray射線無損檢測設備檢測印制電路板

怎樣測試PCB印制電路板信號損耗

怎樣測試PCB印制電路板信號損耗

評論