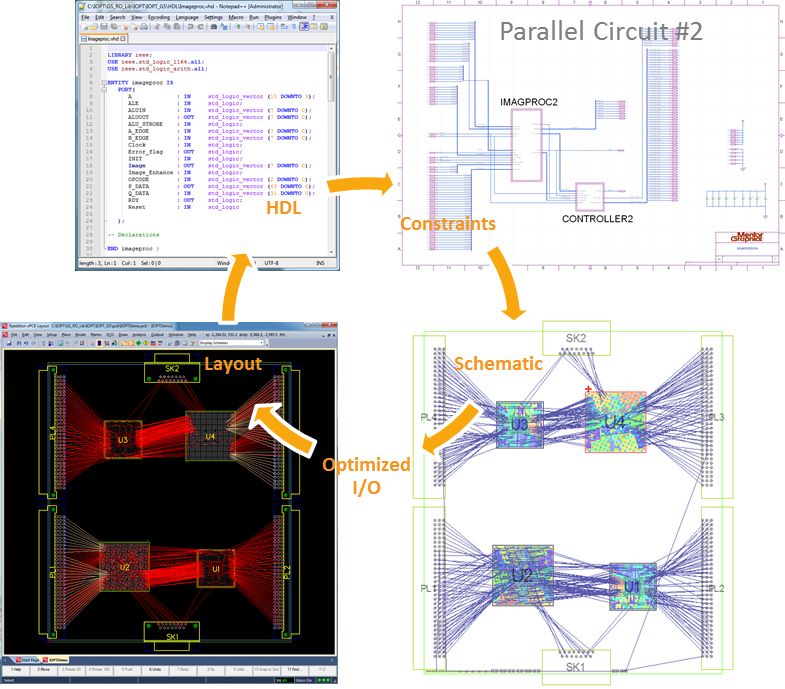

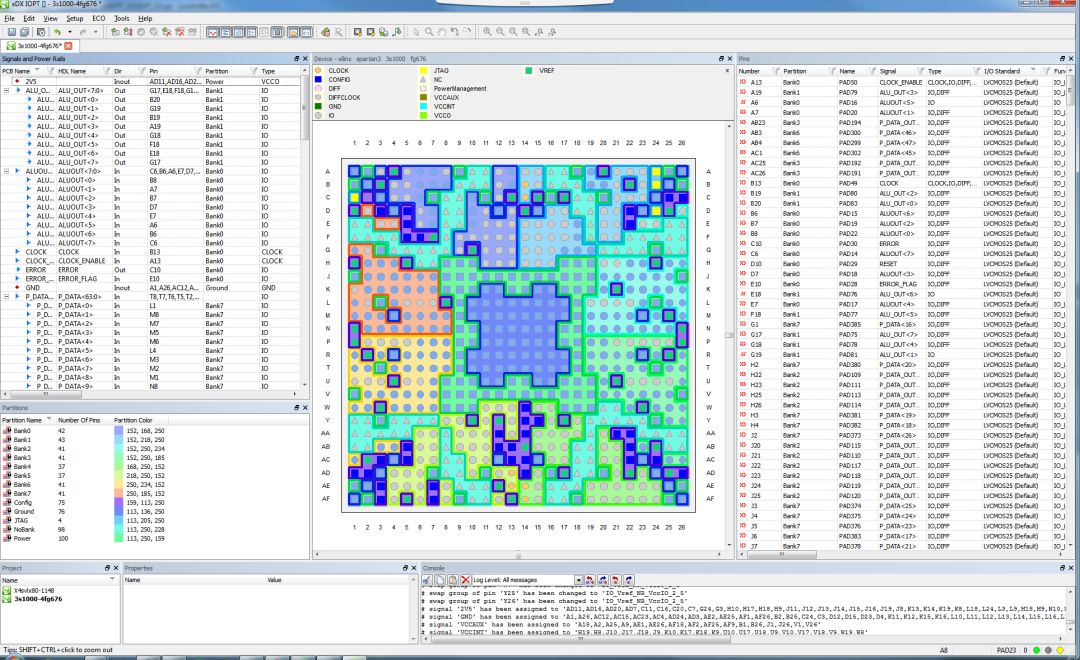

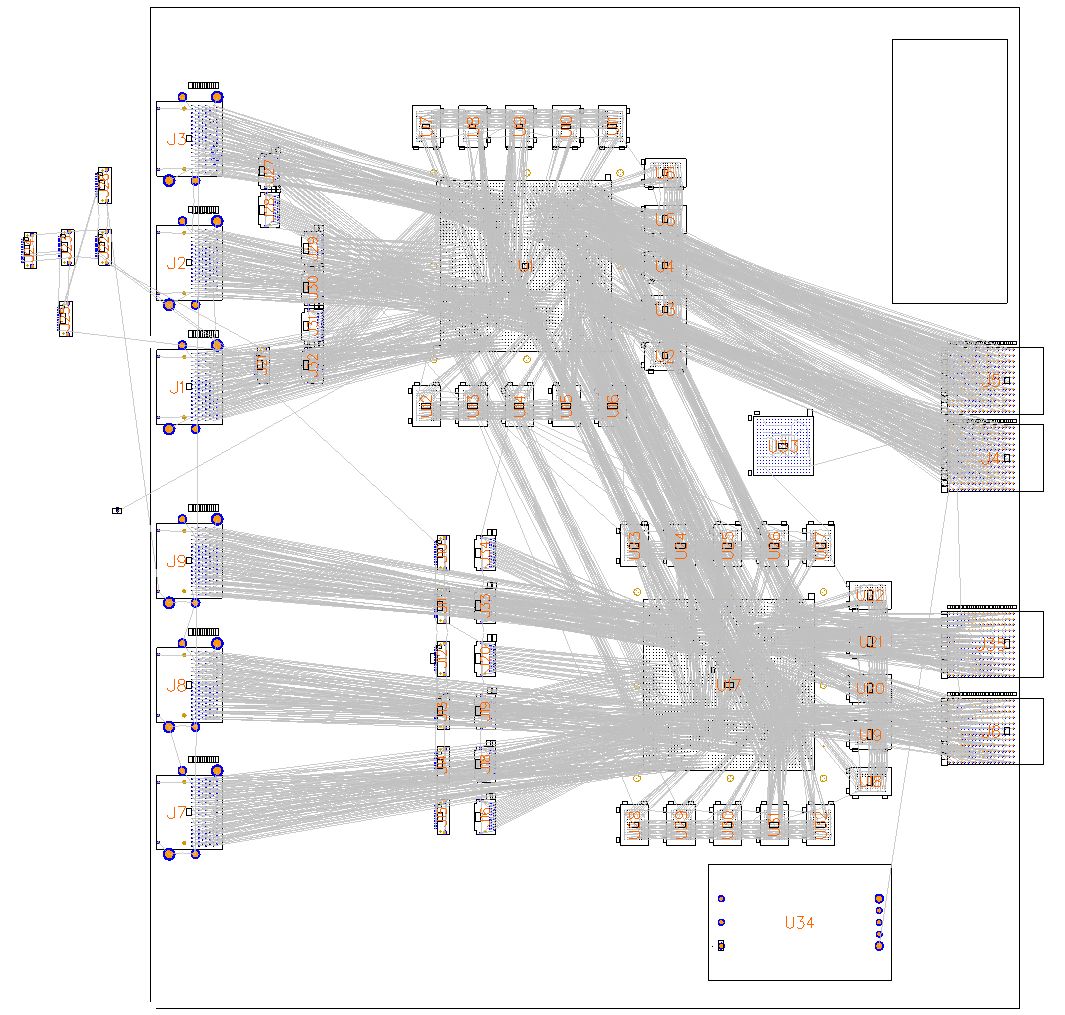

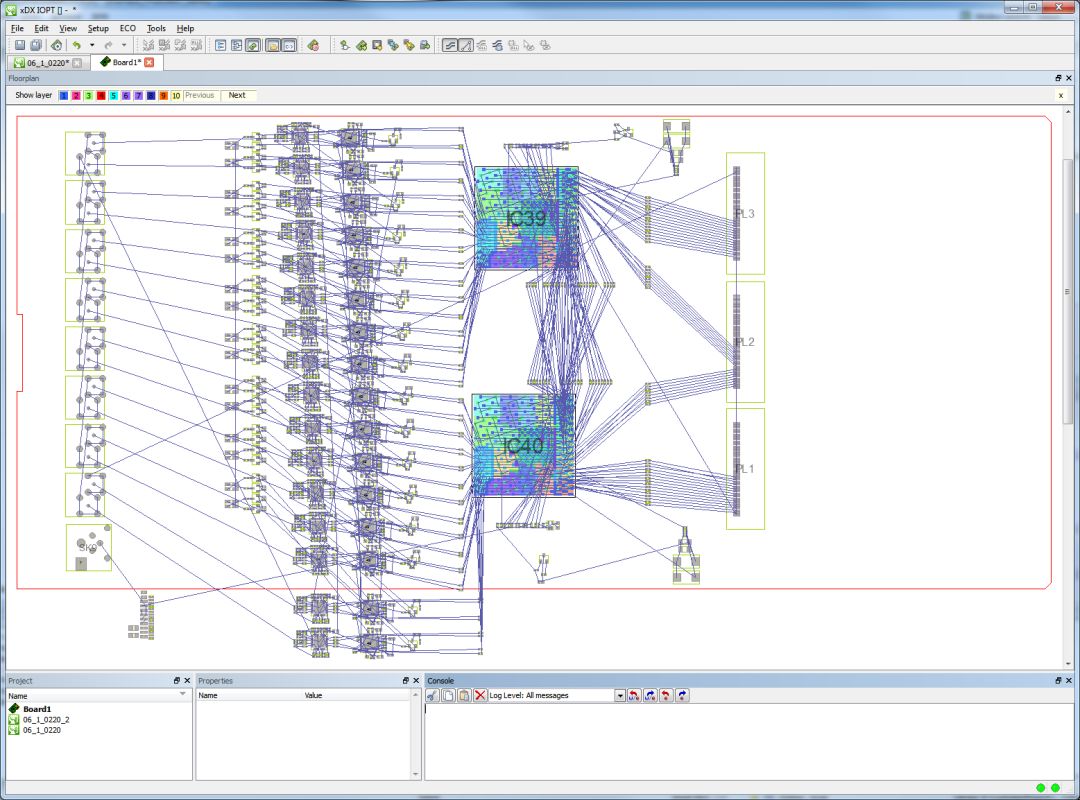

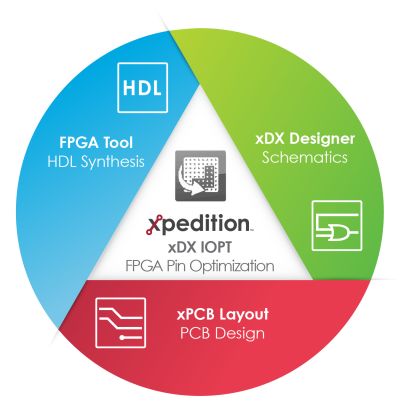

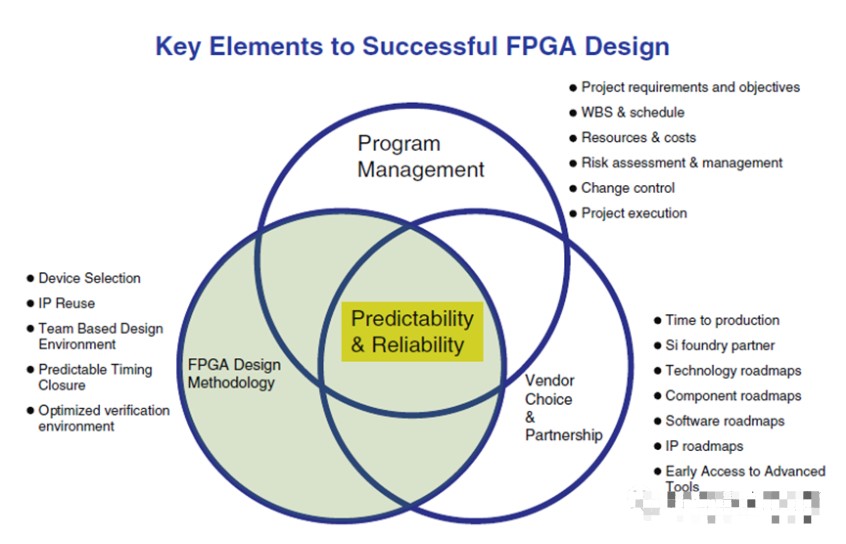

隨著電子產(chǎn)品的集成性及復(fù)雜度呈指數(shù)型增長(zhǎng),加上越來(lái)越苛刻的研發(fā)周期要求,給各種設(shè)計(jì)公司提出了難題。這其中FPGA的設(shè)計(jì)挑戰(zhàn)尤為突出。不斷增加的管腳數(shù)量,同一PCB上的多顆FPGA之間互連等等,面對(duì)這些挑戰(zhàn)如果還依照以往的手動(dòng)式設(shè)計(jì)流程,勢(shì)必會(huì)在激烈的市場(chǎng)競(jìng)爭(zhēng)中失去優(yōu)勢(shì)!Mentor公司針對(duì)這種實(shí)際應(yīng)用情況,提出了集成式管腳優(yōu)化方案,根據(jù)信號(hào)連接關(guān)系及器件位置擺放信息,自動(dòng)實(shí)現(xiàn)IO管腳優(yōu)化,在保證產(chǎn)品質(zhì)量的前提下,高效完成FPGA設(shè)計(jì)及優(yōu)化工作,在最短的時(shí)間內(nèi)使產(chǎn)品順利上市!

4大技術(shù)優(yōu)勢(shì):

| 1 |

縮減設(shè)計(jì)成本: 減少過(guò)孔數(shù)量 節(jié)省PCB疊層數(shù)量 減少生產(chǎn)制造迭代次數(shù) |

| 2 |

縮短設(shè)計(jì)周期: 減少設(shè)計(jì)迭代次數(shù) 提升FPGA布線效率 快速優(yōu)化IO管腳,自動(dòng)生成器件symbol |

| 3 |

減少設(shè)計(jì)失誤: 杜絕器件symbol設(shè)計(jì)失誤 避免手動(dòng)更換IO管腳而造成的失誤 |

| 4 |

提高產(chǎn)品質(zhì)量: 減少布線長(zhǎng)度,提升信號(hào)質(zhì)量 |

01

器件創(chuàng)建

02

03

網(wǎng)絡(luò)飛線優(yōu)化

選定網(wǎng)絡(luò)優(yōu)化

選定FPGA網(wǎng)絡(luò)優(yōu)化

所有網(wǎng)絡(luò)優(yōu)化

04

優(yōu)化后應(yīng)用

-

pcb

+關(guān)注

關(guān)注

4318文章

23022瀏覽量

396430 -

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26489

原文標(biāo)題:不容錯(cuò)過(guò)的研討會(huì) | 復(fù)雜FPGA高效設(shè)計(jì)及優(yōu)化方法

文章出處:【微信號(hào):gh_1a93bb3ab6f3,微信公眾號(hào):Mentor明導(dǎo)PADS】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA工程師是如何實(shí)現(xiàn)復(fù)雜系統(tǒng)設(shè)計(jì)的

FPGA圖書(shū)分享系列-2024.01.31

優(yōu)化 FPGA HLS 設(shè)計(jì)

高級(jí)FPGA設(shè)計(jì) 結(jié)構(gòu)、實(shí)現(xiàn)和優(yōu)化【書(shū)籍教材】

FPGA實(shí)現(xiàn)直接數(shù)字頻率合成(DDS)的原理、電路結(jié)構(gòu)和優(yōu)化...

FPGA的時(shí)序優(yōu)化高級(jí)研修班

FPGA技術(shù)的學(xué)習(xí)方法

FPGA-PCB優(yōu)化技術(shù)降低制造成本

FPGA-PCB優(yōu)化技術(shù)的意義

FPGA設(shè)計(jì)應(yīng)用及優(yōu)化策略有哪些?

海底復(fù)雜環(huán)境下機(jī)器人擺脫障礙物路徑優(yōu)化方法研究

利用FPGA工具設(shè)置優(yōu)化FPGA HLS設(shè)計(jì)

復(fù)雜FPGA高效設(shè)計(jì)及優(yōu)化方法

復(fù)雜深孔的高效加工方法!

技術(shù) | 復(fù)雜FPGA高效設(shè)計(jì)及優(yōu)化方法

技術(shù) | 復(fù)雜FPGA高效設(shè)計(jì)及優(yōu)化方法

評(píng)論