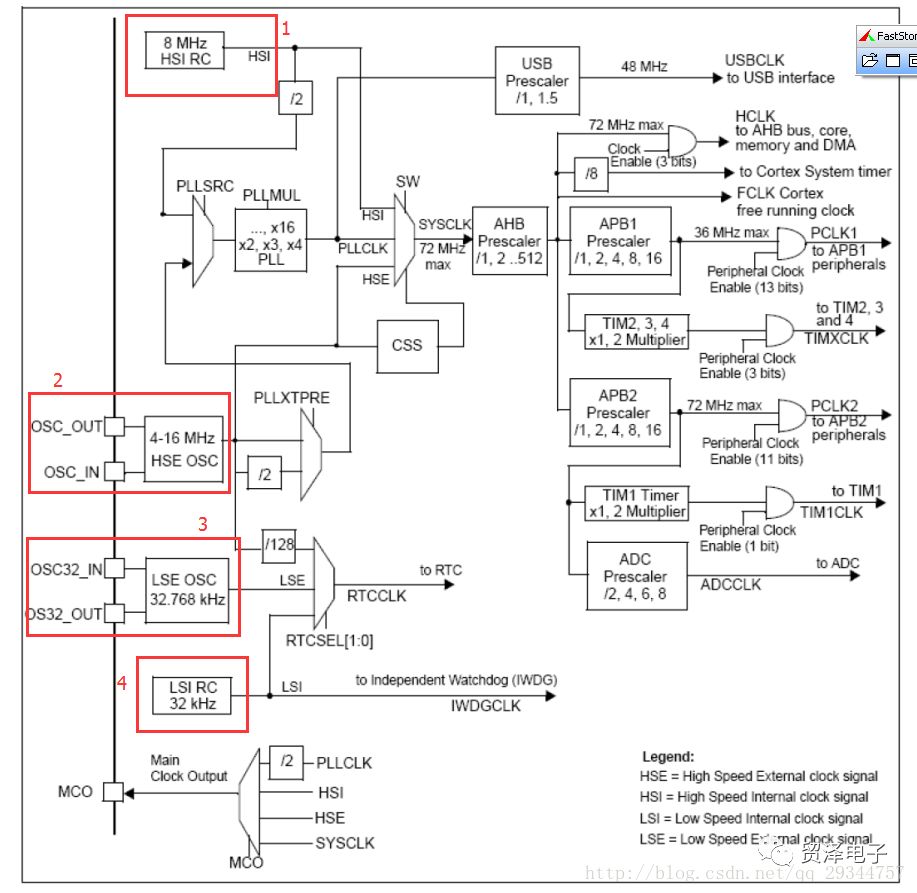

STM32的時鐘體系可以直接以圖概括(摘自STM32F10X參考手冊)

下面就此圖做分析

1. STM32輸入時鐘源

1.1 時鐘源的作用

無論是小型單片機還是像STM32這樣高級單片機,它們工作的核心都是大規模的時序邏輯電路,而驅動時序邏輯電路的關鍵則是準確而又穩定的時鐘源。它的作用就像小學在操場上做廣播體操時候播放的背景音樂,用于協調和同步各單元運行,為時序電路提供基本的脈沖信號。

1.2 STM32時鐘源的設計

在51單片機中,一般都外接一個11.0592MHz的晶振,注意,提供時鐘的不是晶振,而是RC時鐘電路,而晶振只是時鐘電路的元件之一。同理,在STM32中,時鐘源也是由RC時鐘電路產生,與51單片機的區別是區別在于,RC電路的位置。根據RC電路的位置,可以將STM32的時鐘源分為內部時鐘電路和外部時鐘、內外部時鐘電路。

(1)內部時鐘電路:

晶體振蕩器和RC時鐘電路都在STM32芯片內部,如圖中標注1、標注4。

標注1處是產生8MHz的時鐘源,稱為HSI,高速內部時鐘源(H意為高速,S意為源,I意為內部);

標注4處是產生32KHz的時鐘源,稱為LSI,低速內部時鐘源;

(2)內外部時鐘電路:

晶體振蕩器在STM32芯片外部,RC時鐘電路在STM32芯片內部,如圖中標注2、標注3。

標注2處是產生4-16MHz的時鐘源,稱為HSE,高速外部時鐘源;

標注3是產生32.768KHz的時鐘源,稱為LSE,低速外部時鐘源;

OSC_OUT和OSC_IN、OSC32_OUT和OS32_IN分別接晶振的兩個引腳。前者一般接8MHz晶振;后者一定接32.768KHz,因為這個時鐘源是供給RTC實時時鐘使用的。在51單片機中沒有集成RTC模塊,在做電子時鐘時用到的DS1302集成芯片時,也是為其提供的也是32.768KHz的晶振。

(3)外部時鐘電路

晶體振蕩電路和RC時鐘電路都在STM32芯片外部。如圖中標注2、標注3。

OSC_OUT和OSC_IN、OSC32_OUT和OS32_IN除了分別接晶振的兩個引腳,對于OSC_IN和OSC32_IN引腳,還可以接入外部的RC時鐘電路,其時鐘源直接由外部供給,不過這種方案少見。

綜上所述,STM32的時鐘源有4個: HSI、HSE和LSI、LSE。

HSI時鐘源,它是在由STM32在內部用RC振蕩電路實現的高速內部時鐘源。HIS RC振蕩器能夠在不需要任何外部期間的條件下提供系統時鐘,它的啟動時間比HSE晶體振蕩器短,但是不精準,即使在校準之后它的時鐘頻率精度仍較差。在手冊中還明確說,當HSI被用作PLL時鐘輸入時,系統時鐘能得到的最大頻率是61MHz,這顯然不能發揮STM32最極致的性能。

1.3 時鐘信號通道選擇

雖然HSI不精準,但是鑒于啟動速度原因考慮,STM32上電復位,默認是采用HSI時鐘源的,當然開發者可以不修改這個時鐘源,那么系統將一直工作在一個時鐘源不穩定不精準的環境下。

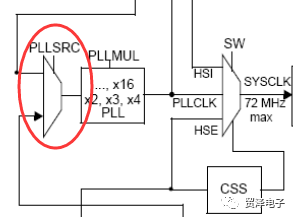

然而一般做法是改變時鐘源,將時鐘源改為HSE。改變時鐘源的通道是在相關寄存器設置的,在圖中的PLLSRC可以實現對這兩個頻率的切換。

1.4 鎖相環倍頻器PLL/預分頻器Prescaler

STM32的cpu的工作常規頻率是72MHZ(超過72MHz工作稱為超頻工作,CPU耗電加劇,且會發燙),但是我們接入的晶振是8MHz,這就需要一個對頻率加倍的操作,即倍頻。如圖中的PLLMUL,PLLMULL實現對接入時鐘源的倍頻,如x2、x3、x4…倍頻后的時鐘源為PLLCLK。

預分頻器是實現對頻率削減作用的。倍頻器將HSE倍頻之后提供給cpu,但是除了cpu之外,其他片內外設,如SPI控制模塊、IIC控制模塊等的工作同樣需要時鐘源,這些外設的時鐘源肯定是低于cpu運行時鐘的,例如USB通訊才需要48MHz,所以需要對倍頻后的時鐘源進行分頻。一般芯片的分頻做法都是對一個時鐘源倍頻后供給某些部件,其他低于此倍頻后的時鐘都是基于此時鐘源來分頻的。用戶可通過多個預分頻器配置AHB,高速APB(APB2)和低速APB(APB1)域的頻率。AHB和APB2域的最大頻率是72MHz。APB1域的最大允許頻率是36MHz。SDIO接口的時鐘頻率固定在HCLK / 2。

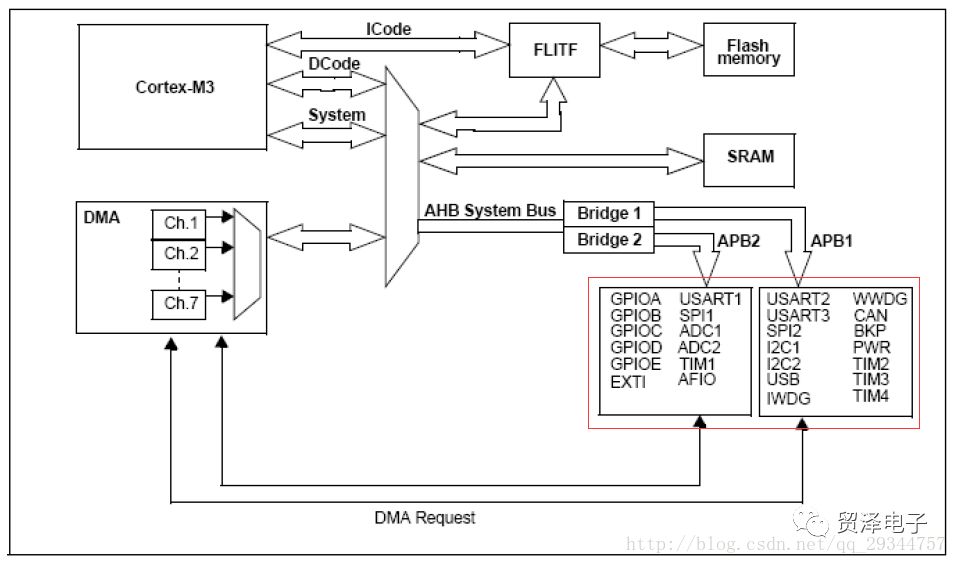

經過時鐘源的選擇、分頻/倍頻,就可以到HCLK(高性能總線AHB用)、FCLK(供給cpu內核的用,常說的cpu主頻)、PCLK(高性能外設總線APB)、USBCLK、TIMXCLK、TIM1CLK、RTCCLK等,外設是掛載STM32的總線上的,具體哪個外設掛載哪個總線,看下圖:

在軟件開發中,我們要做的也無非設置門電路以選擇時鐘源輸入、倍頻/分頻系數和打開/關閉對應外設所在總線的時鐘。

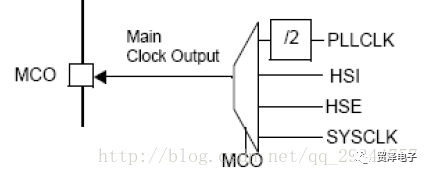

2. STM32輸出時鐘源

圖中的MCO功能模塊,可以將PLLCLK / 2、HSI、HSE、SYSCLK輸出,供給其他系統作為輸入時鐘源,對這一功能模塊也是又相應的寄存器,圖中以MCO標注。

3. 系統滴答Systick

Systick就是一個定時器而已,只是它放在了NVIC中,主要的目的是為了給操作系統提供一個硬件上的中斷,稱之為滴答中斷操作系統進行運轉的時候,也會有時間節拍。它會根據節拍來工作,把整個時間段分成很多小小的時間片,而每個任務每次只能運行一個時間片的時間長度,超時就退出給別的任務運行,這樣可以確保任何一個任務都不會霸占操作系統提供的各種定時功能,都與這個滴答定時器有關。因此,需要一個定時器來產生周期性的中斷,而且最好還讓用戶程序不能隨意訪問它的寄存器,以維持操作系統的節拍。只要不把它在SysTick控制及狀態寄存器中的使能位清除,就一直執行。

RCC(復位與時鐘控制器)通過AHB時鐘(HCLK)8分頻后作為Cortex系統定時器(SysTick)的外部時鐘。通過對SysTick控制與狀態寄存器的設置,可選擇上述時鐘或Cortex(HCLK)時鐘作為SysTick時鐘(后者圖中沒畫出)。另外,還有其他時鐘,如USB時鐘,ADC時鐘、獨立看門狗時鐘等,它們各自的時鐘源通過前面學習,也可以輕易分析出來,這里不再贅述。

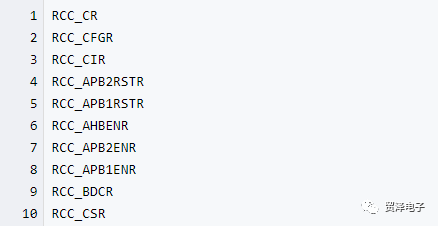

4. 時鐘相關的寄存器

時鐘體系涉及到的寄存器有:

-

電路

+關注

關注

172文章

5852瀏覽量

171942 -

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

時鐘

+關注

關注

10文章

1721瀏覽量

131378

發布評論請先 登錄

相關推薦

S3C2440時鐘體系結構

時鐘體系疑問

PSoC 5體系結構中是否存在時鐘鎖定?

為什么要了解時鐘體系呢

Arm的DRTM體系結構規范

LTE體系結構

網絡體系結構,什么是網絡體系結構

體系結構建模工具SA分析

軟件體系結構的分析

詳解STM32時鐘體系結構分析

詳解STM32時鐘體系結構分析

評論