背景:

快速傅里葉變換(FFT)在雷達、通信和電子對抗等領域有廣泛應用。近年來隨著現場可編程門陣列(FPGA)的飛速發展,與DSP技術相比,由于其并行信號處理結構,使得FPGA能夠很好地適用于高速信號處理系統,但是,由于Altera等公司研制的FFT IP核,價錢昂貴,不適合大規模應用,在特定領域中,設計適合于自己領域需要的FFT處理器是較為實際的選擇,下面將關注一些關于流水級FFT處理器的一些最新發展。

SDF FFT Core → FPGA DSP slice:

近期,在IEEE VLSI系統專欄學報處有一篇12頁的題為“Efficient FPGA Mapping of Pipeline SDF FFT Cores”的新論文即將被發表(在IEEE Xplore可見)。而在這篇論文中作者就如何將一個SDF(single-path delay feedback單路延遲反饋)FFT核映射到Xilinx的全可編程芯片內部的DSP48 slices的可編程邏輯及其他可用的存儲資源上進行了深入周密的細節性討論。盡管這篇論文主要是針對Virtex-4和Virtex-6系列FPGA進行討論的,但是作者也明確指出,由于Xilinx 7系列和UltraScale/UltraScale+ 系列FPGA與Virtex-6使用相同的slice 架構,所以這種映射其實很容易被推廣的。

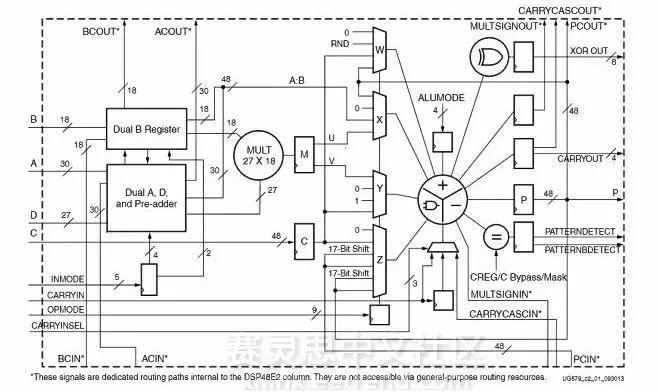

在論文中,作者詳細闡述了Xilinx的產品,主要是從Virtex-4 FPGA開始到Xilinx后來的所有全可編程芯片等多代產品內部的DSP48 slices的一個發展過程:首先,Virtex-4 FPGA系列包含一18X18bit乘法器和48bit累加器的XtremeDSP(DSP48);之后的Virtex-6系列FPGA加入了25x18bit乘法器和48bit累加器的DSP48 slices ;較新的7系列FPGA和Zynq-7000系列SoC則內嵌了25x18bit乘法器和48bit累加器的DSP48 slices;而最強的UltraScale/UltraScale+系列FPGA則包括了27x18bit乘法器和48bit加法器的DSP48E2。除此之外,在Xilinx每一代FPGA的DSP48 slices的發展中都有很多額外的改進,比如時鐘率具有較穩定的提高,也正是這么多代產品的不斷迭代,才使得現在的DSP48E2 功能更加強大。下圖是論文中作者提到的關于DSP48E2 功能實現的細節。

圖1 DSP48E2 功能細節

同時,在這片IEEE的論文中還討論了如何將此FFT核蝶形轉換到較少的LUT單元中,而如何有效轉換關系到是否可以實現DSP48 preadders的蝶形地址,在實現過程中,通過將有效的數據映射和轉換因子存儲到BRAM 及分布式存儲資源中,有效地完成 radix-2k算法轉換因子的共享,此外采用重新定時和流水的方式來縮短實現時間。

雖然這篇博客展示的任何技術都是來自于論文中,讀者也可以從IEEE論文網站得到,但是還是會給出論文中的一些結論(以便可以提起您去檢索并閱讀全文的興趣):“報告的實現結果表明,相比于之前的有關實現而言,通過利用Virtex-4和Virtex-6內部的DSP48實現一個FFT核,可以使其性能分別提高350%到400%,同時,還可以獲得一個更高的混合時鐘頻率,并且整個實現過程只需要更少的存儲資源。這也正好如以前發表過的最好的報告結果一樣,都是使用完全一樣的架構,使用同Virtex-4完全一樣的算法,也體現出這種轉換的優勢十分明顯,所以,為提高性能,可以嘗試將架構映射到FPGA硬件結構中來實現。

總結:

在目前的市場中,尤其是一些互聯網公司,都開始利用FPGA做硬件加速的實現,不僅是因為FPGA的可用性,更主要的是各大公司都看中了硬件實現軟件算法時對整個算法質量的極大提升,這類市場也恰好是我們Xilinx未來競爭的關鍵點所在。

-

算法

+關注

關注

23文章

4601瀏覽量

92677 -

硬件

+關注

關注

11文章

3260瀏覽量

66132 -

軟件

+關注

關注

69文章

4799瀏覽量

87178

發布評論請先 登錄

相關推薦

采用FPGA實現DisplayPort詳細教程【賽靈思內部資料】

FPGA設計之浮點DSP算法實現【賽靈思工程師作品】

賽靈思公司亞太區銷售與市場副總裁給XILINX客戶的信

【AD新聞】賽靈思新CEO訪華繪藍圖,7nm ACAP平臺要讓CPU/GPU難企及

【PYNQ-Z2申請】基于賽靈思PYNQ-Z2平臺的圖像實時力學測量

基于賽靈思FPGA的卷積神經網絡實現設計

為什么說賽靈思已經遠遠領先于Altera?

從賽靈思FPGA設計流程看懂FPGA設計

不僅服務硬件工程師_2018年賽靈思如何布局AI

賽靈思推出高級設計工具,能大幅簡化無線電算法的設計生產力

賽靈思推出首個基于機器學習優化算法 FPGA EDA 工具套件

賽靈思Vivado ML版優化應用設計

賽靈思未來競爭的關鍵點:硬件實現軟件算法時對整個算法質量的極大提升

賽靈思未來競爭的關鍵點:硬件實現軟件算法時對整個算法質量的極大提升

評論