為將設(shè)計(jì)團(tuán)隊(duì)的生產(chǎn)力提升到全新的水平,并將All Programmable FPGA、SoC 和3D IC 推向更廣泛的軟件工程師用戶,賽靈思近期新增了兩款SDx 開發(fā)環(huán)境系列成員。新推出的SDAccel 開發(fā)環(huán)境使沒有任何FPGA經(jīng)驗(yàn)的數(shù)據(jù)中心設(shè)備編程員都能夠運(yùn)用OpenCL、C 或C++ 語言針對(duì)數(shù)據(jù)中心和云計(jì)算基礎(chǔ)設(shè)施對(duì)賽靈思FPGA進(jìn)行編程,設(shè)計(jì)出的FPGA 設(shè)備性能功耗比遠(yuǎn)超基于GPU 和CPU 的設(shè)備。賽靈思還推出了SDSoC 開發(fā)環(huán)境,支持同樣沒有FPGA 經(jīng)驗(yàn)的軟件開發(fā)人員用C 或C++ 語言基于賽靈思及第三方平臺(tái)開發(fā)商推出的Zynq-7000 All Programmable SoC 和UltraScale+ MPSoC 平臺(tái)創(chuàng)建各種系統(tǒng)。

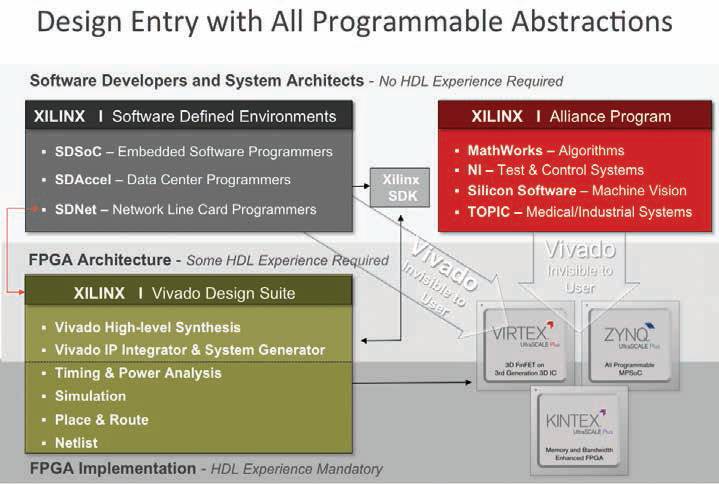

SDx 環(huán)境是賽靈思All Programmable Abstraction 計(jì)劃的最新產(chǎn)品。該計(jì)劃旨在幫助軟件工程師和系統(tǒng)架構(gòu)師方便地編程賽靈思器件,同時(shí)開發(fā)環(huán)境可根據(jù)他們的需求量身定制。

“SDNet、SDAccel 與SDSoC 這一完美組合將為系統(tǒng)和軟件工程師提供熟悉的類似CPU、GPU 和ASSP 的編程環(huán)境,這些工程師將首次盡享All Programmable 器件帶來的獨(dú)特優(yōu)勢,諸如定制加速功能,性能功耗比提升10 倍乃至100 倍,任意設(shè)備件間連接,以及提供下一代智能系統(tǒng)所需的保密性和安全性。賽靈思正力助下一代系統(tǒng)做到進(jìn)一步互聯(lián),實(shí)現(xiàn)軟件定義和虛擬化,同時(shí)還必須支持基于軟件的分析,更多云端計(jì)算功能,這通常是無處不在的視頻和嵌入式視覺應(yīng)用所需要的。這就要求SDx 軟件定義編程環(huán)境和異構(gòu)多處理技術(shù)采用新型UltraScale FPGA 和MPSoC。”

——Steve Glaser,賽靈思公司企業(yè)戰(zhàn)略與市場營銷高級(jí)副總裁

All Programmable Abstraction

賽靈思于2008 年在新任CEO Moshe Gavrielov 領(lǐng)導(dǎo)下開始規(guī)劃7 系列All Programmable 系列FPGA、3D IC 和Zynq-7000 All Programmable SoC 時(shí),就明顯發(fā)現(xiàn)7 系列和未來產(chǎn)品線的所有產(chǎn)品均具有豐富的功能,完全能讓客戶將賽靈思器件作為最新最具創(chuàng)新性產(chǎn)品的核心。

這些All Programmable 器件比賽靈思早些年的膠合邏輯FPGA 高級(jí)得多,實(shí)現(xiàn)了任何其他架構(gòu)所無法企及的系統(tǒng)功能和最終產(chǎn)品差異化。為了最大化這些最新器件的價(jià)值,在競爭中脫穎而出,管理層認(rèn)識(shí)到賽靈思必須開發(fā)出相關(guān)工具和方法,幫助系統(tǒng)架構(gòu)師乃至嵌入式軟件開發(fā)員(而僅僅只有FPGA 專家),去進(jìn)行賽靈思最新器件的編程工作。此外,公司還必須針對(duì)高增長市場,為軟件工程師開發(fā)出設(shè)計(jì)環(huán)境,并根據(jù)設(shè)計(jì)人員習(xí)慣使用的工具和流程來定制這些環(huán)境。此外,加強(qiáng)與MathWorks 和國家儀器(Nl)等公司聯(lián)盟也勢在必行,這些公司已經(jīng)構(gòu)建了各種環(huán)境,使非傳統(tǒng)FPGA 用戶能夠充分利用賽靈思All Programmable 器件的功率效率和靈活性優(yōu)勢。

對(duì)老客戶來說,如果能為設(shè)計(jì)團(tuán)隊(duì)的每個(gè)成員都提供相應(yīng)的設(shè)計(jì)環(huán)境,那就能確保高效性,縮短產(chǎn)品上市時(shí)間。如果這些環(huán)境足夠高級(jí),就能真正推廣All Programmable FPGA 和Zynq SoC 設(shè)計(jì),讓那些沒有FPGA 設(shè)計(jì)經(jīng)驗(yàn)的架構(gòu)師和軟件工程師無需硬件設(shè)計(jì)人員幫助就能進(jìn)行器件編程。全球軟件工程師人數(shù)與硬件工程師人數(shù)比為10:1。因此,提供這種開發(fā)環(huán)境(或支持這種開發(fā)環(huán)境的硬件平臺(tái))的賽靈思及其聯(lián)盟計(jì)劃合作伙伴既能擴(kuò)大用戶群,又能增加營收。

該戰(zhàn)略和支持軟件工程師及系統(tǒng)架構(gòu)師利用根據(jù)其設(shè)計(jì)需求量身定做的環(huán)境進(jìn)行賽靈思器件編程的后續(xù)開發(fā)工作就是賽靈思所謂的All Programmable Abstraction(如圖 所示)。

VIVADO HLS和IPI:設(shè)計(jì)抽象的第一步

設(shè)計(jì)抽象邁出了重大的第一步,那就是賽靈思收購了私企AutoESL 公司的高層次綜合(HLS)工具。繼并購之后,賽靈思于2012 年公開發(fā)布了集成到ISE 設(shè)計(jì)套件和Vivado 設(shè)計(jì)套件工具流程中的HLS技術(shù)。根據(jù)Berkeley Design Automation的詳細(xì)調(diào)研(結(jié)果表明AutoESL 的HLS 工具最簡便易用,而且是EDA 產(chǎn)業(yè)所有HLS 工具中能提供最佳結(jié)果質(zhì)量的HLS),賽靈思選擇了AutoESL技術(shù)。HLS 源于EDA 世界,這也意味著工具使用模型面向的是ASSP 和片上系統(tǒng)(SoC)架構(gòu)師以及擁有C 和C++ 編程經(jīng)驗(yàn)、同時(shí)對(duì)硬件描述語言(Verilog 和VHDL)及芯片設(shè)計(jì)需求有一定工作了解的成熟設(shè)計(jì)團(tuán)隊(duì)。

利用Vivado HLS,具有豐富技能的架構(gòu)師和設(shè)計(jì)團(tuán)隊(duì)能用C 和C++ 創(chuàng)建算法,同時(shí)利用Vivado HLS 來編譯并轉(zhuǎn)換那些算法為RTL IP 模塊。隨后,F(xiàn)PGA 設(shè)計(jì)人員能將這個(gè)模塊及其它模塊集成到創(chuàng)建或授權(quán)的RTL 中,并用賽靈思的IP Integrator(IPI)工具將IP 匯編到設(shè)計(jì)中。隨后,F(xiàn)PGA設(shè)計(jì)人員能將匯編設(shè)計(jì)一步步通過Vivado 流程,執(zhí)行HDL 仿真、時(shí)序與功耗優(yōu)化、布局布線等。最終,設(shè)計(jì)人員生成網(wǎng)表/ 比特文件并配置目標(biāo)All Programmable 器件的硬件。如果設(shè)計(jì)包含處理器(Zynq SoC 或MPU 軟核),配置后的器件隨即可供嵌入式軟件工程師編程。

為了幫助嵌入式軟件工程師應(yīng)對(duì)繁雜的編程工作,賽靈思提供了基于Eclipse 的集成設(shè)計(jì)環(huán)境,即賽靈思軟件開發(fā)套件(SDK),其包含編輯器、編譯器、調(diào)試器、驅(qū)動(dòng)程序和面向Zynq SoC 或FPGA 的庫,其內(nèi)嵌了賽靈思的32 位MicroBlazeTM 軟核。該SDK 于10 多年前推出,隨著賽靈思器件上處理器集成的發(fā)展變化而得到了大幅提升,此前器件上集成硬化的DSP Slice 和軟核MCU 和MPU(8位、16 位和32 位),到Virtex-4 和Virtex-5 FPGA 時(shí)已轉(zhuǎn)變?yōu)榧捎不?2 位PowerPC ;到Zynq SoC 已轉(zhuǎn)化為集成32 位ARM 處理器;而到即將推出的Zynq UltraScale+ MPSoC 則發(fā)展到集成64 位ARM 處理器。

聯(lián)盟成員為更多用戶帶來增值

10 多年來,賽靈思與國家儀器(NI)和MathWorks 公司一直保持密切合作。這兩家公司致力于為其服務(wù)的特定用戶提供量身定制的獨(dú)特高級(jí)開發(fā)環(huán)境。

美國國家儀器(NI)(德克薩斯州奧斯汀)提供的硬件平臺(tái)深受控制和測試系統(tǒng)創(chuàng)新者歡迎。賽靈思的FPGA和Zynq SoC 為NI RIO 平臺(tái)提供動(dòng)力。NI 的LabVIEW 開發(fā)環(huán)境是用戶友好型圖形化程序,底層運(yùn)行Vivado設(shè)計(jì)套件,因此NI 的客戶無需了解任何FPGA 設(shè)計(jì)細(xì)節(jié)。一些人或許根本不知道RIO 產(chǎn)品的核心其實(shí)是賽靈思器件。他們只需在LabVIEW 環(huán)境中對(duì)其系統(tǒng)編程即可,NI 硬件能提升其開發(fā)的設(shè)計(jì)性能。

MathWorks(馬薩諸塞州納蒂克),該公司10 多年前為其MATLAB、Simulink、HDL Coder和Embedded Coder 添加了FPGA 支持,底層運(yùn)行賽靈思的ISE 和Vivado工具,而且完全自動(dòng)化。因此,公司的用戶—— 主要是數(shù)學(xué)算法開發(fā)人員—— 能開發(fā)算法并大幅提升算法性能,而且能在FPGA 結(jié)構(gòu)上簡便運(yùn)行算法。

10 年前,賽靈思為其ISE 開發(fā)環(huán)境添加了FPGA 架構(gòu)級(jí)工具—— 系統(tǒng)生成器(System Generator),近期又給Vivado 設(shè)計(jì)套件添加了,以幫助具備FPGA 知識(shí)的團(tuán)隊(duì)進(jìn)一步調(diào)節(jié)設(shè)計(jì),實(shí)現(xiàn)算法性能增益。MathWorks 和賽靈思兩家公司技術(shù)的強(qiáng)強(qiáng)組合,有助于客戶公司推出成千上萬種創(chuàng)新產(chǎn)品。

近期,其他公司也開始為賽靈思環(huán)境做出貢獻(xiàn)。賽靈思近期迎來TOPIC Embedded Systems 和Silicon Software 這兩家歐洲公司加入其聯(lián)盟計(jì)劃,特別是歡迎其針對(duì)醫(yī)學(xué)和工業(yè)市場的高級(jí)開發(fā)環(huán)境。

TOPIC Embedded Systems(荷蘭埃因霍溫)擁有獨(dú)特的開發(fā)環(huán)境DYPLO,《賽靈思中國通訊第54 期》對(duì)其進(jìn)行了詳細(xì)介紹。該環(huán)境面向Zynq SoC,很快也將面向Zynq MPSoC,對(duì)系統(tǒng)級(jí)設(shè)計(jì)采用統(tǒng)一方法,從而使系統(tǒng)架構(gòu)師能夠用C 或C++ 創(chuàng)建系統(tǒng)設(shè)計(jì)結(jié)果,并在Zynq SoC 的雙核ARM Cortex-A9 處理系統(tǒng)上運(yùn)行該結(jié)果。一旦用戶發(fā)現(xiàn)設(shè)計(jì)某些部分在軟件中運(yùn)行太慢,可以將這些部分拖放到窗口中,將C 語言轉(zhuǎn)化為FPGA 邏輯(底層運(yùn)行Vivado HLS),并將其放入Zynq SoC 的可編程邏輯中。來回交換代碼片段,直到達(dá)到最佳系統(tǒng)性能。TOPIC 最初用于醫(yī)療設(shè)備開發(fā),目前也開始與工業(yè)設(shè)備制造商合作。

Silicon Software(德國曼海姆)是支持軟件工程師利用賽靈思All Programmable 器件的最新聯(lián)盟成員。公司的VisualApplets 圖形圖像處理設(shè)計(jì)環(huán)境可幫助面向Zynq SoC 平臺(tái)的系統(tǒng)架構(gòu)師和軟件工程師打造工業(yè)機(jī)器視覺應(yīng)用創(chuàng)新,而且無需硬件工程師的協(xié)助。在2013 年SPS Drives 行業(yè)展會(huì)的賽靈思展臺(tái)上,Silicon Software展示了其用VisualApplets 環(huán)境開發(fā)的光學(xué)檢查系統(tǒng)。演示顯示通過采用VisualApplets 環(huán)境將圖形處理任務(wù)從Zynq SoC 的處理系統(tǒng)轉(zhuǎn)交給器件的FPGA 邏輯來執(zhí)行,能將系統(tǒng)性能提升10 倍。

借助SDx推廣FPGA和SOC設(shè)計(jì)

借助SDx 軟件定義開發(fā)環(huán)境,賽靈思將面向關(guān)鍵市場的軟件開發(fā)人員和系統(tǒng)架構(gòu)師構(gòu)建一系列高級(jí)的設(shè)計(jì)入門環(huán)境。SDAccel 和SDSoC 在底層自動(dòng)運(yùn)行整個(gè)Vivado 流程,無需直接使用Vivado 工具,也無需硬件工程師的協(xié)助。SDNet 不會(huì)訪問Vivado HLS,針對(duì)線路卡架構(gòu)師,其提供了獨(dú)特的“兩步使用模型”。

在第一步中,線路卡架構(gòu)師采用直觀的類似C 語言的高級(jí)語言而不是晦澀的微代碼來設(shè)計(jì)需求,并制定網(wǎng)絡(luò)線路卡規(guī)格描述。SDNet 開發(fā)環(huán)境根據(jù)規(guī)格描述生成RTL 版設(shè)計(jì)。流程隨后需要硬件工程師在目標(biāo)FPGA 中實(shí)現(xiàn)RTL。

在第二步中,SDNet 還允許網(wǎng)絡(luò)公司用高級(jí)語言測試和更新協(xié)議,并升級(jí)線路卡的功能,即便在現(xiàn)場部署后也能做到,而且無需硬件設(shè)計(jì)參與。這個(gè)流程有助于企業(yè)快速創(chuàng)建并更新線路卡,這種靈活性對(duì)軟件定義網(wǎng)絡(luò)而言非常重要。

SDAccel 和SDSoc 這兩個(gè)新設(shè)計(jì)環(huán)境將SDx 的理念推廣到新的應(yīng)用領(lǐng)域。

SDACCEL可優(yōu)化數(shù)據(jù)中心性能功耗比

《數(shù)據(jù)中心學(xué)刊》(Data Center Journal)2014 年3 月的一篇文章指出,谷歌、Facebook、亞馬遜、領(lǐng)英等公司核心部分—— 數(shù)據(jù)庫——“消耗的電力占全球電力3% 以上,同時(shí)產(chǎn)生2 億公噸二氧化碳”。如此巨大的能耗使得其數(shù)據(jù)中心一年電費(fèi)超過600 億美元。即便對(duì)最大規(guī)模網(wǎng)絡(luò)公司來說,功耗也會(huì)嚴(yán)重削減盈利性,而且對(duì)環(huán)境也會(huì)產(chǎn)生不可估量的影響。

隨著越來越多的企業(yè)期望采用云計(jì)算和大數(shù)據(jù)分析技術(shù);視頻和流媒體的全球性普及,以及越來越多的人加入無線網(wǎng)并準(zhǔn)備升級(jí)到未來5G 網(wǎng)絡(luò),對(duì)數(shù)量更多、性能更好的數(shù)據(jù)中心的需求呈幾何級(jí)無止境增長趨勢。《數(shù)據(jù)中心學(xué)刊》文章指出,從當(dāng)前趨勢看,到2017 年數(shù)據(jù)中心流量預(yù)計(jì)將達(dá)7.7ZB,這意味著數(shù)據(jù)中心的功耗如果不能得到有效控制將會(huì)出現(xiàn)大幅增長。當(dāng)今大多數(shù)數(shù)據(jù)中心的功耗主要源于其基礎(chǔ)組件—— Intel x86 處理器。目前MPU 能提供良好但不是最佳的性能,而且功耗很高。

目前全球龐大的的軟件工程師隊(duì)伍均發(fā)現(xiàn)MPU 是最容易編程的器件。要解決數(shù)據(jù)中心性能問題,許多公司一直在設(shè)法構(gòu)建采用圖形處理單元(GPU)或通過GPU 實(shí)現(xiàn)CPU 系統(tǒng)加速的設(shè)備。GPU 的性能大大超越數(shù)據(jù)中心的CPU,但不幸的是功耗要高很多。性能雖然很高,但功耗巨大。

為集兩者之大成,許多企業(yè)均轉(zhuǎn)而采用以FPGA為中心的方法,將FPGA與其它處理器結(jié)合使用,以實(shí)現(xiàn)數(shù)據(jù)中心設(shè)備性能最大化。

許多數(shù)據(jù)中心設(shè)備廠商已證實(shí),分立式FPGA結(jié)合分立式CPU使用,雖然每個(gè)卡的功耗會(huì)增加一點(diǎn)點(diǎn),但性能卻得到大幅提升,從而可大幅提升性能功耗比。還有人認(rèn)為,通過采用一顆在單個(gè)SoC上集成x86處理器內(nèi)核和FPGA邏輯的芯片,有望進(jìn)一步提升性能功耗比。還有人認(rèn)為,在單個(gè)SoC上集成FPGA邏輯和64位ARM處理器IP似乎能帶來更低功耗但同樣高性能的解決方案。

在數(shù)據(jù)中心使用FPGA 的主要障礙就是編程問題。數(shù)據(jù)中心開發(fā)人員習(xí)慣于x86 架構(gòu)編程,這些開發(fā)人員通常只有純軟件編程背景。幫助開發(fā)人員將CPU 程序轉(zhuǎn)向更快的GPU 的第一步就是業(yè)界OpenCL 語言的開放開發(fā)。過去2 年來,OpenCL 取得進(jìn)一步發(fā)展,使客戶能夠針對(duì)FPGA 進(jìn)行編程,從而為未來數(shù)據(jù)中心設(shè)備架構(gòu)乃至無所不在網(wǎng)絡(luò)創(chuàng)造了新的機(jī)遇。

通過推出SDAccel 環(huán)境,賽靈思彌補(bǔ)了編程鴻溝,并為數(shù)據(jù)中心工程師使用OpenCL、C 或C++ 編程FPGA 平臺(tái)鋪平了道路,而且無需硬件工程師介入。賽靈思公司設(shè)計(jì)方法市場高級(jí)總監(jiān)Tom Feist 表示,針對(duì)OpenCL、C 和C++ 的SDAccel 開發(fā)環(huán)境使數(shù)據(jù)中心編程人員能夠打造出比CPU 和GPU 系統(tǒng)性能功耗比高出25倍的設(shè)備。

Feist 指出,在SDAccel 流程中,x86 CPU 結(jié)合運(yùn)行賽靈思20nm Kintex UltraScale FPGA 的加速卡,軟件開發(fā)人員能發(fā)現(xiàn)需要加速的應(yīng)用,并用OpenCL 編碼和優(yōu)化內(nèi)核,再為CPU編譯和執(zhí)行應(yīng)用。隨后他們再來評(píng)估并調(diào)試內(nèi)核,直到找到周期精確的模型。接下來,再用SDAccel 編譯代碼,并自動(dòng)實(shí)現(xiàn)在FPGA 中(可能因?yàn)閂ivado 在底層運(yùn)行)。隨后就能運(yùn)行應(yīng)用,驗(yàn)證通過卡加速后的應(yīng)用性能以及與單純用CPU 運(yùn)行的性能對(duì)比。Feist 指出:“他們能循環(huán)運(yùn)行迭代,直到找到性能和功耗之間的最佳平衡,相對(duì)于CPU 和GPU 實(shí)現(xiàn)方案,性能功耗比可提升多達(dá)25 倍。”

SDSOC讓嵌入式系統(tǒng)創(chuàng)新者輩出

SDNet 讓線卡開發(fā)人員能夠利用獨(dú)特的軟定義方式快速創(chuàng)建下一代網(wǎng)絡(luò),而SDAccel 則能讓數(shù)據(jù)中心設(shè)備廠商的下一代數(shù)據(jù)中心設(shè)計(jì)的實(shí)現(xiàn)最佳性能功耗比。新的SDSoC 開發(fā)環(huán)境或許能為賽靈思用戶群帶來最廣泛的影響。這是因?yàn)镾DSoC 針對(duì)廣泛的嵌入式系統(tǒng)設(shè)計(jì)團(tuán)隊(duì),特別是軟件工程師,這些軟件工程師設(shè)計(jì)面向的是賽靈思Zynq SoC 所服務(wù)的大部分市場。SDSoC 環(huán)境現(xiàn)在能讓用戶配置邏輯—— 不光是對(duì)運(yùn)行Zynq SoC 硬件平臺(tái)的嵌入式系統(tǒng)處理器編程——而且能使用C 和C++ 語言。

“軟件開發(fā)人員習(xí)慣于對(duì)主板、ASSP平臺(tái)和ASIC 進(jìn)行編程,且無需硬件工程師參與。有了SDSoC 開發(fā)環(huán)境,他們就用類似ASSP 的方式對(duì)Zynq SoC 和MPSoC 平臺(tái)進(jìn)行編程。SDSoC 的獨(dú)特之處在于現(xiàn)在我們能在Eclipse IDE 環(huán)境中用C 或C++ 語言面向Zynq SoC 和Zynq UltraScale+ MPSoC 平臺(tái)創(chuàng)建完整的系統(tǒng)設(shè)計(jì)。”

——Nick Ni,賽靈思SDSoC 產(chǎn)品經(jīng)理

使用SDSoC 環(huán)境,嵌入式軟件開發(fā)人員能運(yùn)用C 或C++語言創(chuàng)建設(shè)計(jì)并進(jìn)行測試,以發(fā)現(xiàn)Zynq SoC 處理系統(tǒng)上哪些部分運(yùn)行得不佳。一旦發(fā)現(xiàn)可疑代碼,便突出顯示并命令SDSoC 環(huán)境自動(dòng)將該代碼分區(qū)到Zynq SoC 的可編程邏輯中,以加速系統(tǒng)性能。Nick 指出,SDSoC環(huán)境只需點(diǎn)擊按鈕就能把軟件功能移到FPGA 邏輯中,無需硬件工程師介入。SDSoC 中的編譯器將生成整個(gè)Vivado 項(xiàng)目,并為目標(biāo)硬件平臺(tái)生成可引導(dǎo)的軟件映像。

“利用針對(duì)我們Zynq SoC 的SDSoC 環(huán)境,我們主要是讓我們的嵌入式軟件工程師變成系統(tǒng)工程師。”

SDSoC 環(huán)境利用帶有用戶指定的C/C++ 代碼的宏編譯器,可在Zynq SoC 邏輯中實(shí)現(xiàn)加速。通過在底層運(yùn)行Vivado 設(shè)計(jì)套件,該環(huán)境可自動(dòng)將該代碼返回IP 模塊并將該模塊配置為器件的邏輯,從而自動(dòng)生成軟件驅(qū)動(dòng)程序。

SDSoC 可為基于Zynq All Programmable SoC 的開發(fā)板(包括ZC702和ZC706),以及第三方和特定市場平臺(tái)(諸如ZedBoard、 MicroZed、ZYBO 以及視頻與圖像開發(fā)平臺(tái))提供板支持包 (BSP)。

“我們今后幾個(gè)月將為SDSoC 添加更多BSP,尤其是隨著越來越多第三方平臺(tái)公司用Zynq SoC 開發(fā)系統(tǒng)。SDSoC 有助于賽靈思以及采用Zynq SoC 開發(fā)平臺(tái)的公司擴(kuò)大用戶群。”

“SDSoC 環(huán)境的主要目的是讓大量嵌入式軟件設(shè)計(jì)人員能用賽靈思Zynq SoC 創(chuàng)建完整的系統(tǒng),不過有傳統(tǒng)FPGA 背景的用戶和設(shè)計(jì)團(tuán)隊(duì)也能從該環(huán)境受益匪淺。”

“它能幫助設(shè)計(jì)團(tuán)隊(duì)快速用C 和C++ 語言設(shè)計(jì)系統(tǒng)架構(gòu),然后嘗試不同的配置,以獲得所需的最佳性能。如果他們團(tuán)隊(duì)里確實(shí)有FPGA 設(shè)計(jì)人員,則能讓其通過Vivado 工具來進(jìn)一步優(yōu)化模塊和邏輯布局。”

——Nick Ni,賽靈思SDSoC 產(chǎn)品經(jīng)理

-

軟件開發(fā)

+關(guān)注

關(guān)注

0文章

608瀏覽量

27338 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

514瀏覽量

44074 -

開發(fā)環(huán)境

+關(guān)注

關(guān)注

1文章

222瀏覽量

16586

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

賽靈思推出兩款開發(fā)環(huán)境軟件能配合多種系統(tǒng)級(jí)設(shè)計(jì)工具

賽靈思推出兩款開發(fā)環(huán)境軟件能配合多種系統(tǒng)級(jí)設(shè)計(jì)工具

評(píng)論