《XDC約束技巧之時(shí)鐘篇》中曾對(duì)I/O約束做過簡要概括,相比較而言,XDC中的I/O約束雖然形式簡單,但整體思路和約束方法卻與UCF大相徑庭。加之FPGA的應(yīng)用特性決定了其在接口上有多種構(gòu)建和實(shí)現(xiàn)方式,所以從UCF到XDC的轉(zhuǎn)換過程中,最具挑戰(zhàn)的可以說便是本文將要討論的I/O約束了。

I/O約束的語法

XDC中可以用于I/O約束的命令包括set_input_delay / set_output_delay和set_max_delay / set_min_delay 。其中,只有那些從FPGA管腳進(jìn)入和/或輸出都不經(jīng)過任何時(shí)序元件的純組合邏輯路徑可以用set_max_delay / set_min_delay來約束,其余I/O時(shí)序路徑都必須由set_input_delay / set_output_delay來約束。如果對(duì)FPGA的I/O不加任何約束,Vivado會(huì)缺省認(rèn)為時(shí)序要求為無窮大,不僅綜合和實(shí)現(xiàn)時(shí)不會(huì)考慮I/O時(shí)序,而且在時(shí)序分析時(shí)也不會(huì)報(bào)出這些未約束的路徑。

本文以下章節(jié)將會(huì)著重討論XDC接口約束和時(shí)序分析的基礎(chǔ),介紹如何使用set_input_delay / set_output_delay對(duì)FPGA的I/O時(shí)序進(jìn)行約束。

Input約束

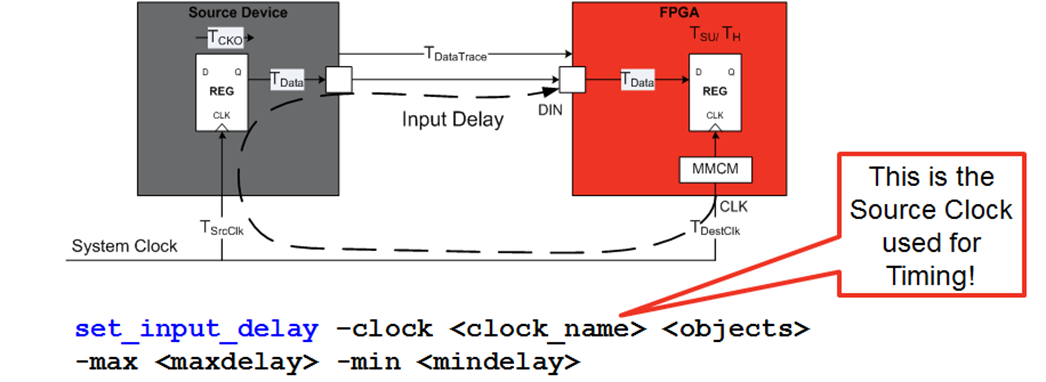

上圖所示set_input_delay的基本語法中, 是想要設(shè)定input約束的端口名,可以是一個(gè)或數(shù)個(gè)port;-clock 之后的 指明了對(duì) 時(shí)序進(jìn)行分析所用的時(shí)鐘,可以是一個(gè)FPGA中真實(shí)存在的時(shí)鐘也可以是預(yù)先定義好的虛擬時(shí)鐘;-max之后的 描述了用于setup分析的包含有板級(jí)走線和外部器件的延時(shí);-min之后的 描述了用于hold分析的包含有板級(jí)走線和外部器件的延時(shí)。

上述這些選項(xiàng)是定義Input約束時(shí)必須寫明的,還有少數(shù)幾個(gè)可選項(xiàng),如 -add_delay 和 -clock_fall用于DDR接口的約束。

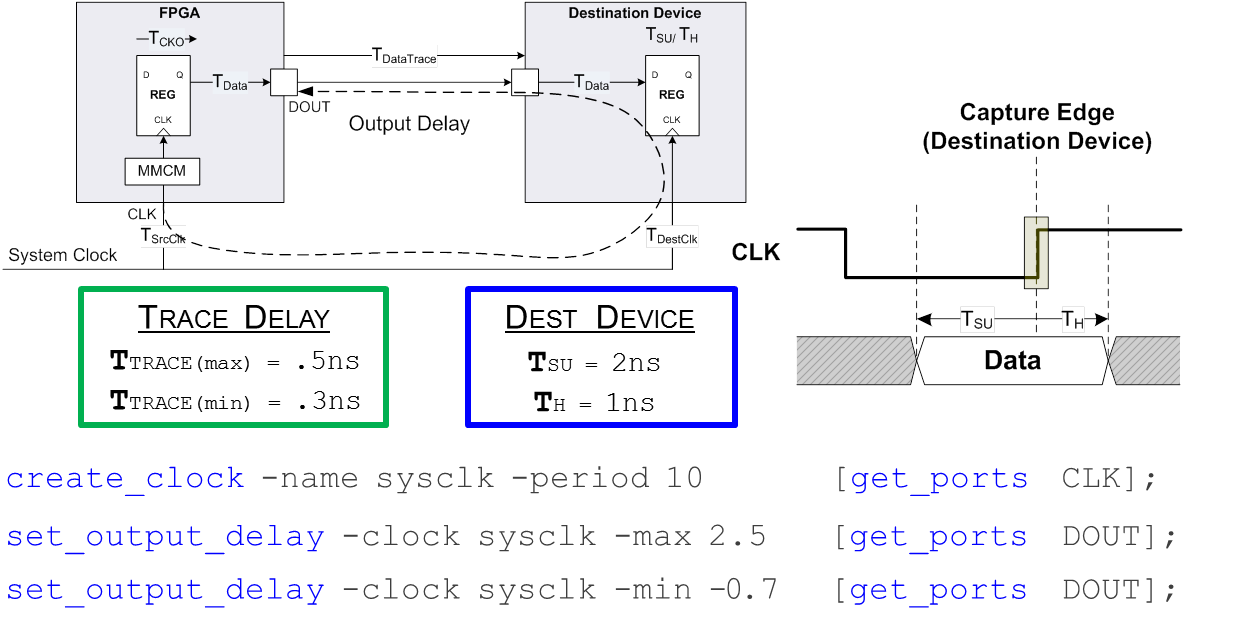

Output約束

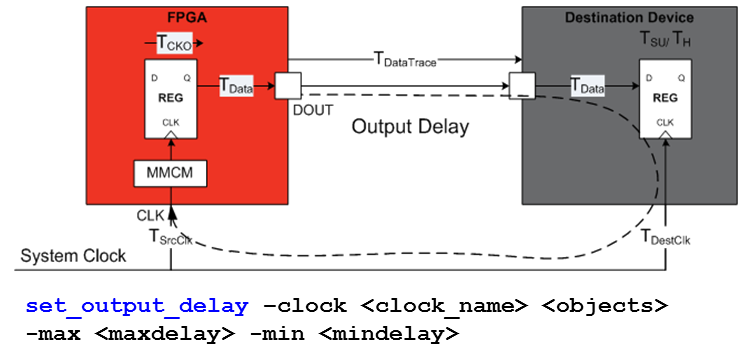

上圖所示set_output_delay的基本語法中, 是想要設(shè)定output約束的端口名,可以是一個(gè)或數(shù)個(gè)port;-clock 之后的 指明了對(duì) 時(shí)序進(jìn)行分析所用的時(shí)鐘,可以是一個(gè)FPGA中真實(shí)存在的時(shí)鐘也可以是預(yù)先定義好的虛擬時(shí)鐘;-max之后的 描述了用于setup分析的包含有板級(jí)走線和外部器件的延時(shí);-min之后的 描述了用于hold分析的包含有板級(jí)走線和外部器件的延時(shí)。

上述這些選項(xiàng)是定義Output約束時(shí)必須寫明的,還有少數(shù)幾個(gè)可選項(xiàng)如 -add_delay 和 -clock_fall用于DDR接口的約束。

Setup/Hold時(shí)序分析

我們知道約束是為了設(shè)計(jì)服務(wù),而設(shè)置好的約束必須在時(shí)序報(bào)告中加以驗(yàn)證。所以,怎樣理解時(shí)序分析中的檢查規(guī)則就成了重中之重,這一點(diǎn)對(duì)I/O約束來說尤為重要。理解時(shí)序分析工具如何選取路徑分析的發(fā)送端(Launch)和接收端(Capture)時(shí)鐘沿(Clock Edges),在Setup和Hold分析時(shí)又有怎樣的具體區(qū)別,以及這些數(shù)字在時(shí)序報(bào)告中如何體現(xiàn)等等是設(shè)置正確I/O約束的基礎(chǔ)。

更具體的時(shí)序分析方法以及如何深入解讀時(shí)序報(bào)告等內(nèi)容將會(huì)在后續(xù)另開主題文章詳述,這里僅就Setup/Hold分析時(shí)對(duì)時(shí)鐘邊沿的選擇加以描述,便于以下章節(jié)的展開。

Setup時(shí)序分析

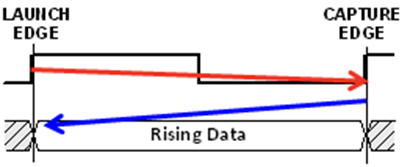

同步電路設(shè)計(jì)中,一般情況下,數(shù)據(jù)在時(shí)鐘上升沿發(fā)送,在下一個(gè)時(shí)鐘上升沿接收,發(fā)送的時(shí)鐘沿稱作Launch Edge,接收沿稱作Capture Edge。時(shí)序分析中的Setup Check跟Capture Edge的選擇息息相關(guān)。

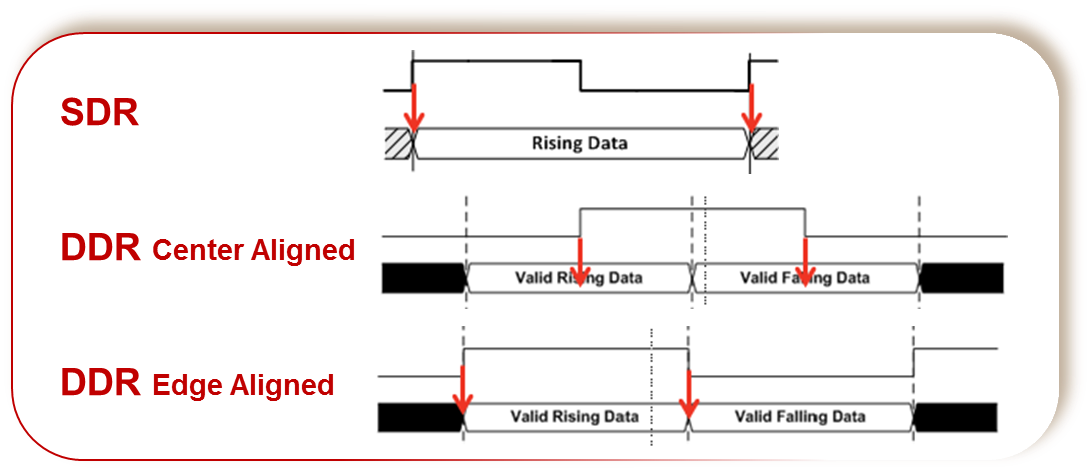

在SDR接口的setup分析中,工具如下圖這樣識(shí)別發(fā)送和接收時(shí)鐘沿。

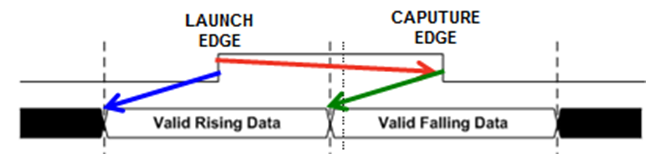

而在DDR接口的setup分析中,因?yàn)閿?shù)據(jù)是雙沿采樣,所以發(fā)送和接收時(shí)鐘沿變成上升(下降)沿發(fā)送,下降(上升)沿接收。

Hold時(shí)序分析

Hold Check主要是為了保證數(shù)據(jù)在接收(采樣)端時(shí)鐘沿之后還能穩(wěn)定保持一段時(shí)間,對(duì)Hold分析而言,同一個(gè)時(shí)鐘沿既是Launch Edge也是Capture Edge,這一點(diǎn)對(duì)SDR和DDR(不論是中心對(duì)齊還是邊沿對(duì)齊)都一樣。

Input接口類型和約束

由于歷史的原因,相當(dāng)一部分FPGA設(shè)計(jì)仍然在系統(tǒng)中起到膠合邏輯(Glue Logic)的作用,當(dāng)然,如今的FPGA中嵌入了高速串行收發(fā)器和嵌入式處理器等,早就不僅僅局限于系統(tǒng)設(shè)計(jì)的配角,反而成為了其中的主角甚至是明星。但數(shù)據(jù)接口的同步一直是 FPGA設(shè)計(jì)中的常見問題,也是一個(gè)重點(diǎn)和難點(diǎn),很多設(shè)計(jì)不穩(wěn)定都是因?yàn)閿?shù)據(jù)接口的同步有問題。

FPGA的數(shù)據(jù)接口同步根據(jù)系統(tǒng)級(jí)設(shè)計(jì)方式來講可以分為系統(tǒng)同步和源同步兩種。

系統(tǒng)同步接口

系統(tǒng)同步接口(System Synchronous Interface)的構(gòu)建相對(duì)容易,以FPGA做接收側(cè)來舉例,上游器件僅僅傳遞數(shù)據(jù)信號(hào)到FPGA中,時(shí)鐘信號(hào)則完全依靠系統(tǒng)板級(jí)來同步。時(shí)鐘信號(hào)在系統(tǒng)級(jí)上同源,板級(jí)走線的延時(shí)也要對(duì)齊。正因?yàn)檫@樣的設(shè)計(jì),決定了數(shù)據(jù)傳遞的性能受到時(shí)鐘在系統(tǒng)級(jí)的走線延時(shí)和skew以及數(shù)據(jù)路徑延時(shí)的雙重限制,無法達(dá)到更高速的設(shè)計(jì)要求,所以大部分情況也僅僅應(yīng)用SDR方式。

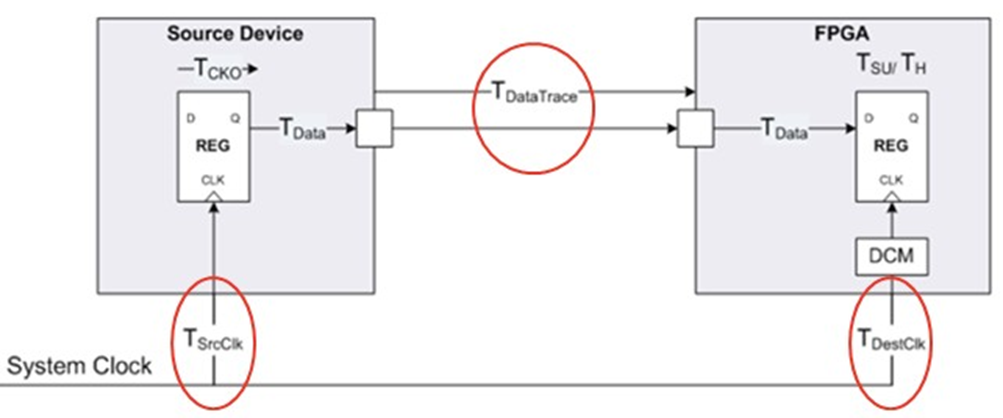

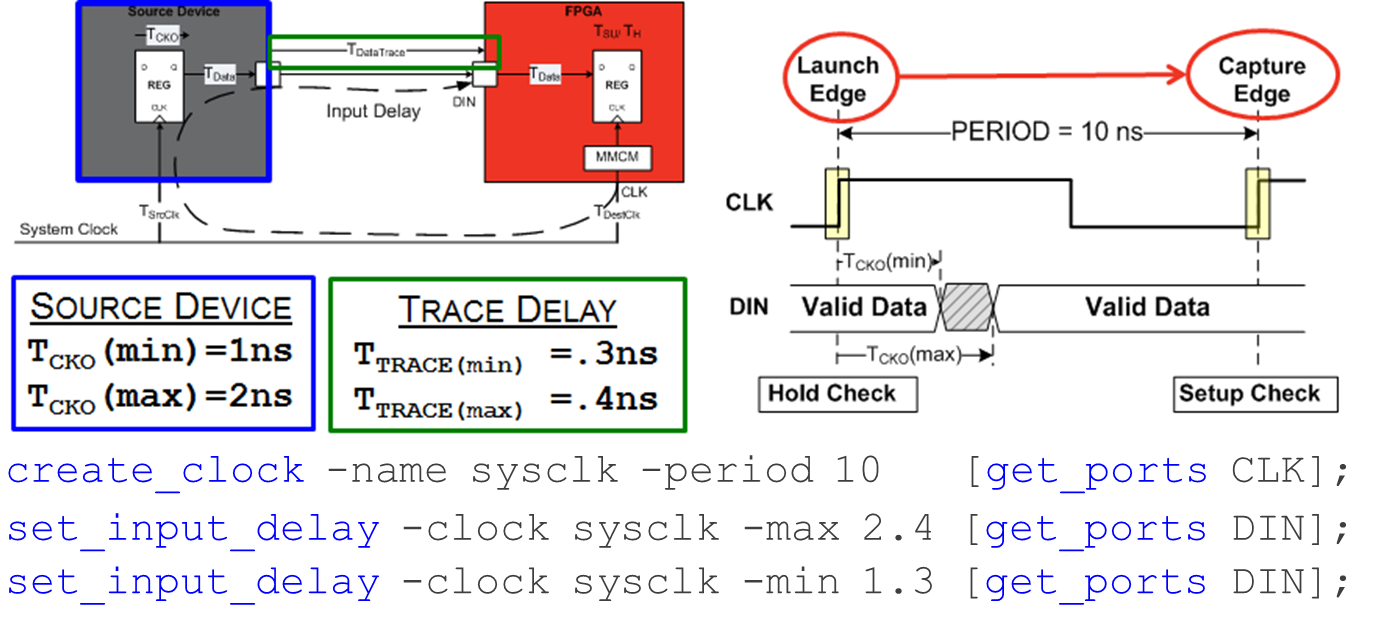

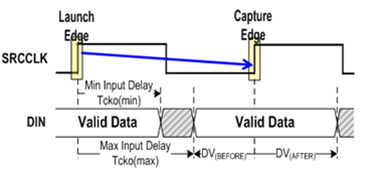

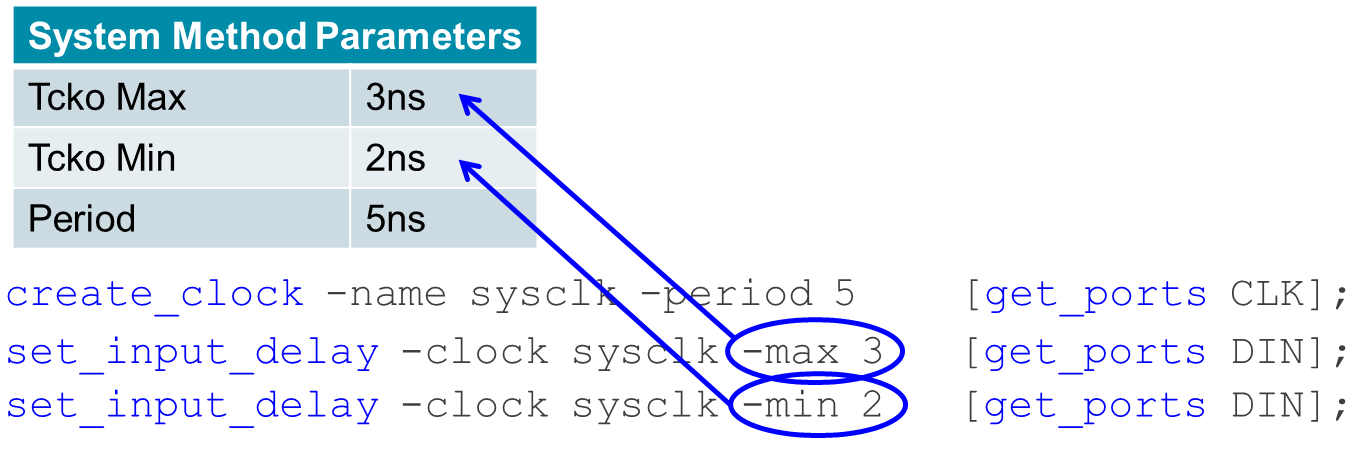

對(duì)系統(tǒng)同步接口做Input約束相對(duì)容易,只需要考慮上游器件的Tcko和數(shù)據(jù)在板級(jí)的延時(shí)即可。下圖是一個(gè)SDR上升沿采樣系統(tǒng)同步接口的Input約束示例。

設(shè)置和分析I/O約束一定要有個(gè)系統(tǒng)級(jí)思考的視角,如上右圖所示,Launch Edge對(duì)應(yīng)的是上游器件的時(shí)鐘,而Capture Edge則對(duì)應(yīng)FPGA的輸入時(shí)鐘,正因?yàn)槭窍到y(tǒng)同步時(shí)鐘,所以可以將其視作完全同步而放在一張圖上分析,這樣一來,就可以用一般時(shí)序分析方法來看待問題。

一條完整的時(shí)序路徑,從源觸發(fā)器的C端開始,經(jīng)過Tcko和路徑傳輸延時(shí)再到目的觸發(fā)器的D端結(jié)束。放在系統(tǒng)同步的接口時(shí)序上,傳輸延時(shí)則變成板級(jí)傳輸延時(shí)(還要考慮skew),所以上述 -max 后的數(shù)值是Tcko的最大值加上板級(jí)延時(shí)的最大值而來,而-min后的數(shù)值則是由兩個(gè)最小值相加而來。

源同步接口

為了改進(jìn)系統(tǒng)同步接口中時(shí)鐘頻率受限的弊端,一種針對(duì)高速I/O的同步時(shí)序接口應(yīng)運(yùn)而生,在發(fā)送端將數(shù)據(jù)和時(shí)鐘同步傳輸,在接收端用時(shí)鐘沿脈沖來對(duì)數(shù)據(jù)進(jìn)行鎖存,重新使數(shù)據(jù)與時(shí)鐘同步,這種電路就是源同步接口電路(Source Synchronous Interface)。

源同步接口最大的優(yōu)點(diǎn)就是大大提升了總線的速度,在理論上信號(hào)的傳送可以不受傳輸延遲的影響,所以源同步接口也經(jīng)常應(yīng)用DDR方式,在相同時(shí)鐘頻率下提供雙倍于SDR接口的數(shù)據(jù)帶寬。

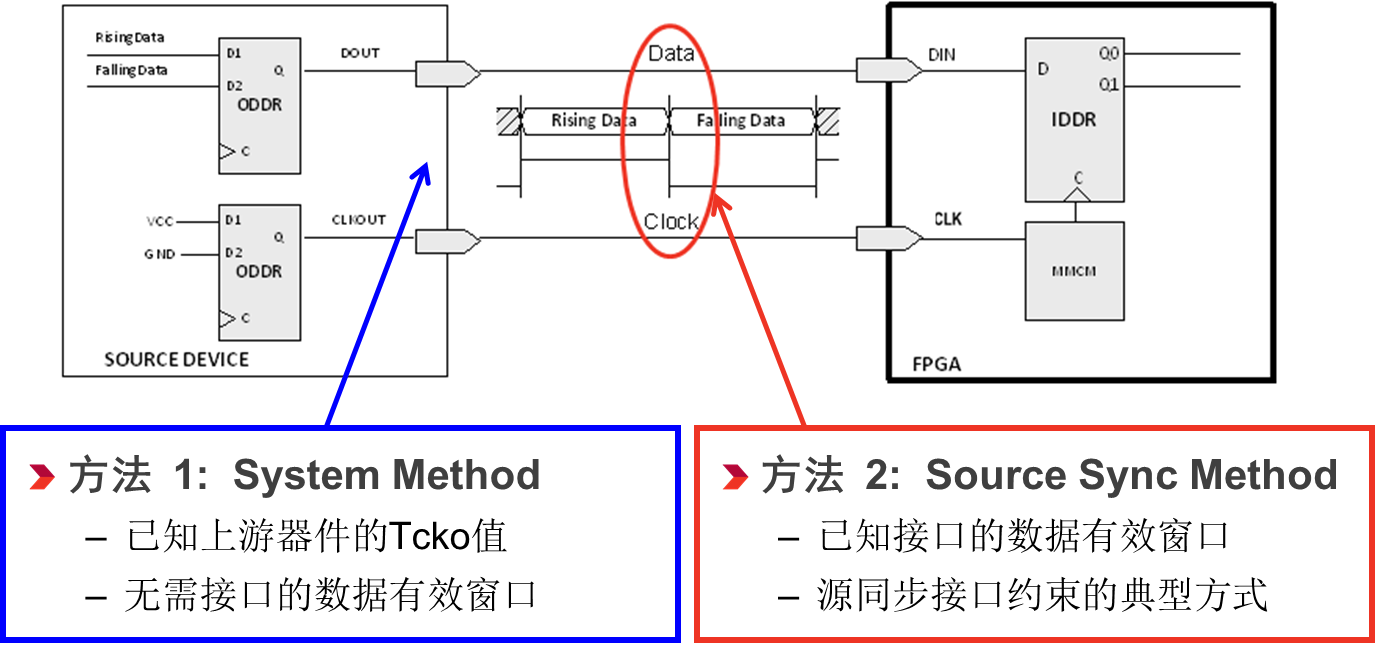

源同步接口的約束設(shè)置相對(duì)復(fù)雜,一則是因?yàn)橛蠸DR、DDR、中心對(duì)齊(Center Aligned)和邊沿對(duì)齊(Edge Aligned)等多種方式,二則可以根據(jù)客觀已知條件,選用與系統(tǒng)同步接口類似的系統(tǒng)級(jí)視角的方式,或是用源同步視角的方式來設(shè)置約束。

如上圖所示,對(duì)源同步接口進(jìn)行Input約束可以根據(jù)不同的已知條件,選用不同的約束方式。一般而言,F(xiàn)PGA作為輸入接口時(shí),數(shù)據(jù)有效窗口是已知條件,所以方法2更常見,Vivado IDE的Language Templates中關(guān)于源同步輸入接口XDC模板也是基于這種方法。但不論以何種方式來設(shè)置Input約束,作用是一樣,時(shí)序報(bào)告的結(jié)果也應(yīng)該是一致的。

針對(duì)上圖所示中心對(duì)齊源同步SDR接口時(shí)序,分別按照兩種方式來約束,需要的已知條件和計(jì)算方式雖然不同,但卻可以得到完全一樣的結(jié)果。

DDR接口的約束設(shè)置

DDR源同步接口的約束稍許復(fù)雜,需要將上升沿和下降沿分別考慮和約束,以下以源同步接口為例,分別就輸入接口數(shù)據(jù)為中心對(duì)齊或邊沿對(duì)齊的方式來舉例。

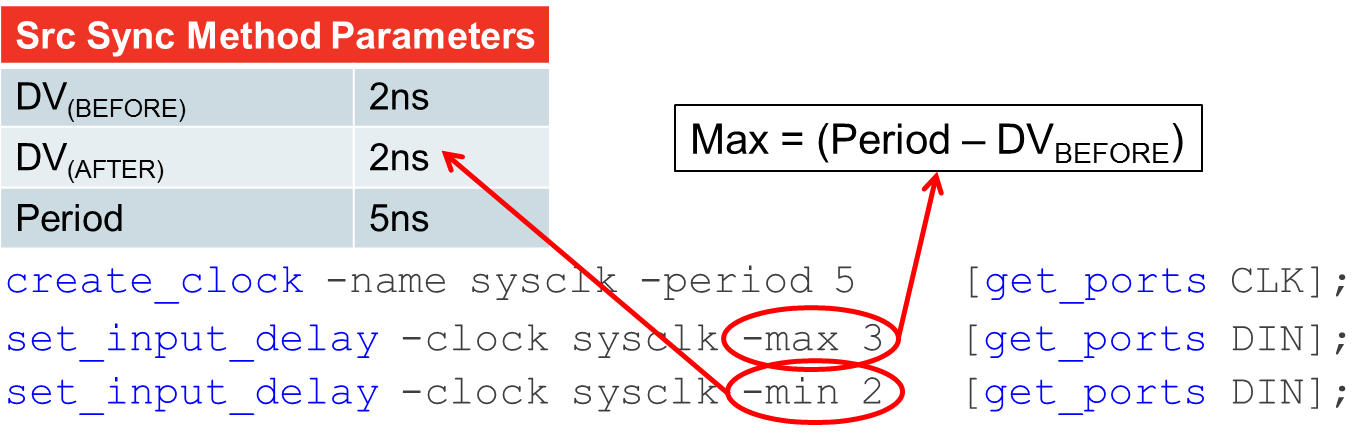

DDR源同步中心對(duì)齊輸入接口

已知條件如下:

時(shí)鐘信號(hào) src_sync_ddr_clk的頻率: 100 MHz

數(shù)據(jù)總線: src_sync_ddr_din[3:0]

上升沿之前的數(shù)據(jù)有效窗口 ( dv_bre ) :4 ns

上升沿之后的數(shù)據(jù)有效窗口 ( dv_are ) : 6 ns

下降沿之前的數(shù)據(jù)有效窗口 ( dv_bfe ) :7 ns

下降沿之后的數(shù)據(jù)有效窗口 ( dv_afe ) : 2 ns

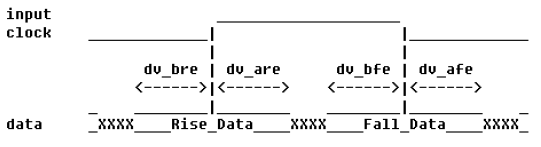

可以這樣計(jì)算輸入接口約束:DDR方式下數(shù)據(jù)實(shí)際的采樣周期是時(shí)鐘周期的一半;上升沿采樣的數(shù)據(jù)(Rise Data)的 -max 應(yīng)該是采樣周期減去這個(gè)數(shù)據(jù)的發(fā)送沿(下降沿)之前的數(shù)據(jù)有效窗口值dv_bfe,而對(duì)應(yīng)的-min 就應(yīng)該是上升沿之后的數(shù)據(jù)有效窗口值dv_are ;同理,下降沿采樣的數(shù)據(jù)(Fall Data)的 -max 應(yīng)該是采樣周期減去這個(gè)數(shù)據(jù)的發(fā)送沿(上升沿)之前的數(shù)據(jù)有效窗口值dv_bre,而對(duì)應(yīng)的-min 就應(yīng)該是下降沿之后的數(shù)據(jù)有效窗口值dv_afe 。

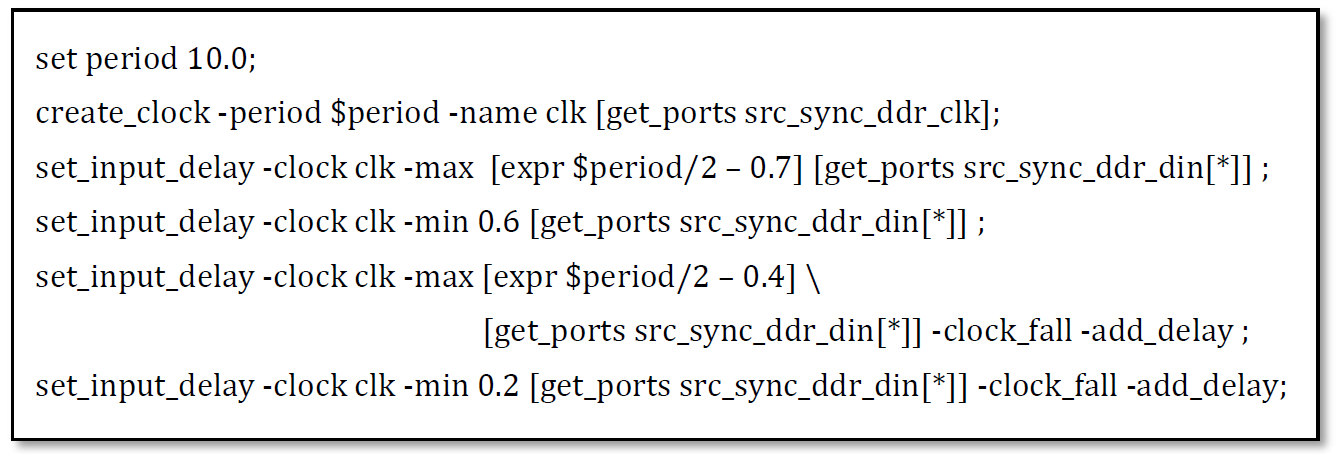

所以最終寫入XDC的Input約束應(yīng)該如下所示:

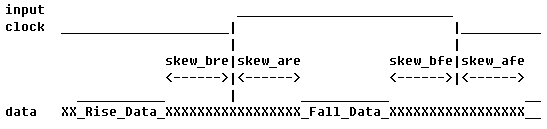

DDR源同步邊沿對(duì)齊輸入接口

已知條件如下:

時(shí)鐘信號(hào) src_sync_ddr_clk的頻率: 100 MHz

數(shù)據(jù)總線: src_sync_ddr_din[3:0]

上升沿之前的數(shù)據(jù)skew (skew_bre ) :6 ns

上升沿之后的數(shù)據(jù)skew (skew_are ) :4 ns

下降沿之前的數(shù)據(jù)skew (skew_bfe ) :3 ns

下降沿之后的數(shù)據(jù)skew (skew_afe ) :7 ns

可以這樣計(jì)算輸入接口約束:因?yàn)橐阎獥l件是數(shù)據(jù)相對(duì)于時(shí)鐘上升沿和下降沿的skew,所以可以分別獨(dú)立計(jì)算;上升沿的 -max 是上升沿之后的數(shù)據(jù)skew (skew_are ),對(duì)應(yīng)的-min 就應(yīng)該是負(fù)的上升沿之前的數(shù)據(jù)skew (skew_bre );下降沿的 -max 是下降沿之后的數(shù)據(jù)skew (skew_afe ),對(duì)應(yīng)的-min 就應(yīng)該是負(fù)的下降沿之前的數(shù)據(jù)skew (skew_bfe )。

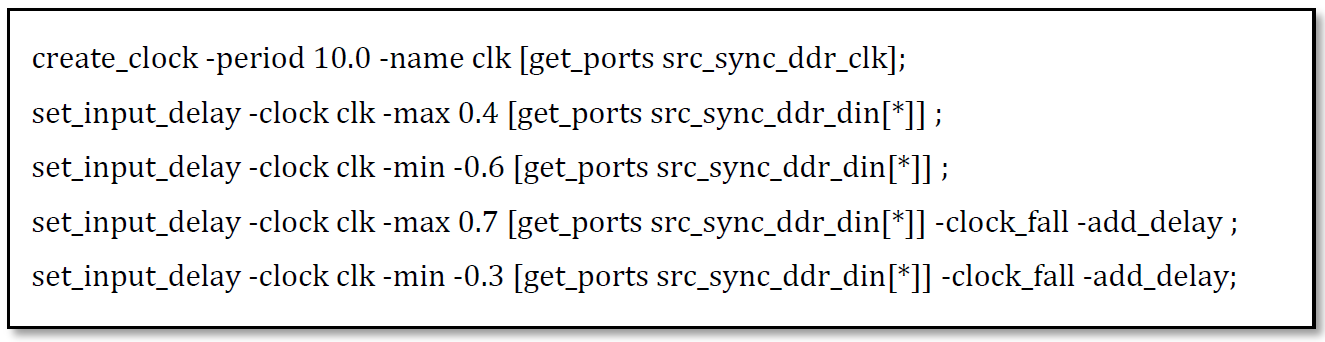

所以最終寫入XDC的Input約束應(yīng)該如下所示:

出現(xiàn)負(fù)值并不代表延時(shí)真的為負(fù),而是跟數(shù)據(jù)相對(duì)于時(shí)鐘沿的方向有關(guān)。請一定牢記set_input_delay中 -max/-min的定義,即時(shí)鐘采樣沿到達(dá)之后最大與最小的數(shù)據(jù)有效窗口(set_output_delay中 -max/-min的定義與之正好相反,詳見后續(xù)章節(jié)舉例說明)。

在這個(gè)例子中,數(shù)據(jù)是邊沿對(duì)齊,只要有jitter跟skew的存在,最差情況下,數(shù)據(jù)有效窗口在到達(dá)時(shí)鐘采樣沿之前就已經(jīng)結(jié)束,所以會(huì)有負(fù)數(shù)出現(xiàn)在-min之后。因此,在實(shí)際應(yīng)用中,F(xiàn)PGA用作輸入的邊沿對(duì)齊DDR源同步接口的情況下,真正用來采樣數(shù)據(jù)的時(shí)鐘會(huì)經(jīng)過一個(gè)MMCM/PLL做一定的相移,從而把邊沿對(duì)齊變成中心對(duì)齊。

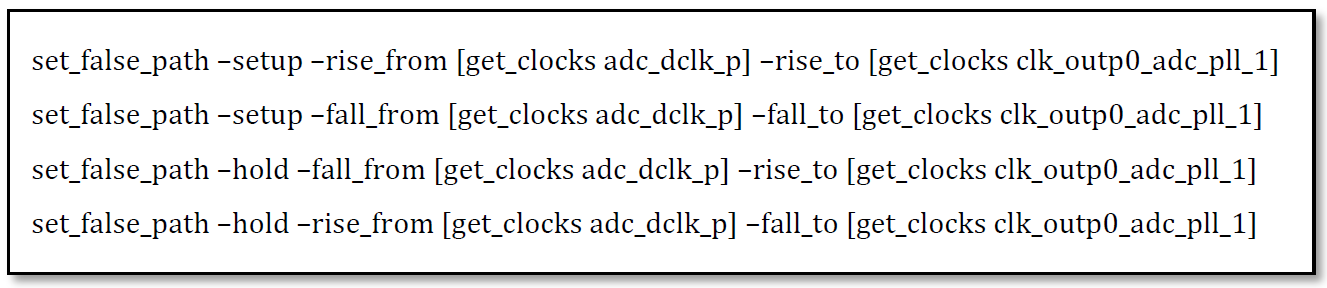

另外,在經(jīng)過MMCM/PLL相移后的采樣時(shí)鐘跟同步接口輸入的時(shí)鐘之間需要做set_false_path的約束(如下述例子)而把那些偽路徑從時(shí)序報(bào)告中剔除,這里不再詳述。

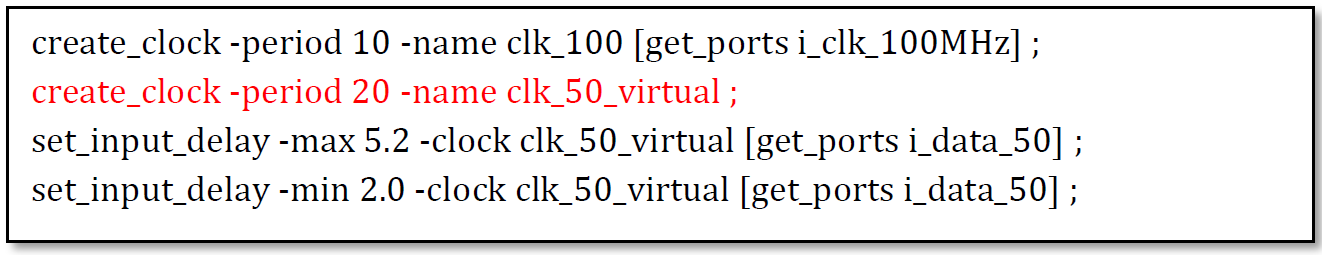

虛擬時(shí)鐘

在FPGA做系統(tǒng)同步輸入接口的情況下,很多時(shí)候上游器件送入的數(shù)據(jù)并不是跟某個(gè)FPGA中已經(jīng)存在的真實(shí)的時(shí)鐘相關(guān),而是來自于一個(gè)不同的時(shí)鐘,這時(shí)就要用到虛擬時(shí)鐘(Virtual Clock)。

舉例來說,上游器件用一個(gè)100MHz的時(shí)鐘送出數(shù)據(jù)到FPGA,實(shí)際上這個(gè)數(shù)據(jù)每兩個(gè)時(shí)鐘周期才變化一次,所以可以用50MHz的時(shí)鐘來采樣。FPGA有個(gè)100MHz的輸入時(shí)鐘,經(jīng)過MMCM產(chǎn)生一個(gè)50MHz的衍生時(shí)鐘,并用其來采樣上游器件送來的同步數(shù)據(jù)。當(dāng)然,系統(tǒng)級(jí)的設(shè)計(jì)上,必須有一定的機(jī)制來保證上游器件中的發(fā)送時(shí)鐘和FPGA中的接收時(shí)鐘的時(shí)鐘沿對(duì)齊。

此時(shí),我們可以借助虛擬時(shí)鐘的幫助來完成相應(yīng)的Input接口約束。

-

電路

+關(guān)注

關(guān)注

172文章

5851瀏覽量

171915 -

約束

+關(guān)注

關(guān)注

0文章

82瀏覽量

12718 -

Output

+關(guān)注

關(guān)注

0文章

31瀏覽量

10483

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

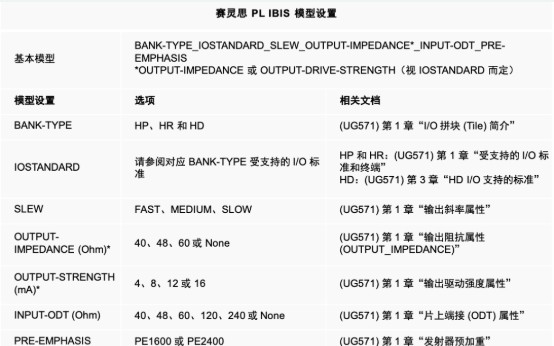

FPGA設(shè)計(jì)時(shí)序約束指南【賽靈思工程師力作】

回收Xilinx芯片 收購賽靈思芯片

這顆賽靈思是限制料還是翻新料?

FPGA設(shè)計(jì)約束技巧之XDC約束之I/O篇 (上)

賽靈思關(guān)于I/O約束法的簡要概括(下)

賽靈思關(guān)于I/O約束法的簡要概括(上)

賽靈思關(guān)于I/O約束法的簡要概括(上)

評(píng)論