許多數字處理系統都會使用FPGA,原因是FPGA有大量的專用DSP以及block RAM資源,可以用于實現并行和流水線算法。因此,通常情況下,FPGA都要和高性能的ADC和DAC進行接口,比如e2v EV10AQ190低功耗四通道10-bit 1.25 Gsps ADC和EV12DS130A內建4/2:1 MUX的低功耗12-bit 3 Gsps DAC。 通常情況下,這些轉換器的采樣率都達到了GHz的級別(見此鏈接http://www.e2v.com/products/hi-rel-semiconductor-solutions/broadband-data-converters/)。對工程師團隊來說,除了混合信號電路板布局之外,理解和使用這些高性能的設備也是一個挑戰。

這些e2v數據轉換器具有帶寬寬、性能好的特點—數據手冊上通常稱為模擬全功率帶寬—即使是在高奈奎斯特區。(這種能力是不多見的。)正是因為有著優異的轉換性能,才可以使用直接上轉換和下轉換,這樣可以減少部件數量、降低功耗以及節省成本。

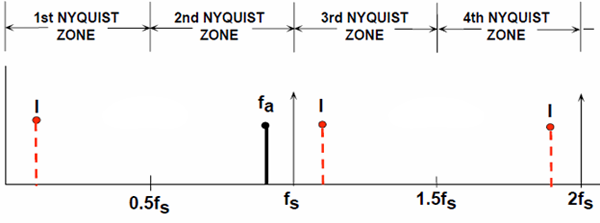

在高頻時,奈奎斯特采樣率(每個周期兩次采樣)是無法維持的。一個例子就是使用一個2.5GHz采樣率的ADC去采樣一個3GHz全功率帶寬的模擬輸入。根據奈奎斯特準則,高于1.25GHz的信號將會被混疊回第一奈奎斯特區,這些混疊圖像是基礎信號的諧波分量,因此和非混疊信號一樣,包含了同樣的信息。

相反的,如果你在使用DAC,進行直接轉換時,你需要確定在上奈奎斯特區你想要使用的諧波。然而,對于DAC,在更高的頻率下,你需要對DAC的衰減進行SINC補償。因此,很常見的是通過仔細選擇輸入組件、阻抗平衡器、交流耦合電容以及通過設計前端模擬預濾波器等等去優化一個ADC或者DAC,使其能在一個奈奎斯特區中工作。

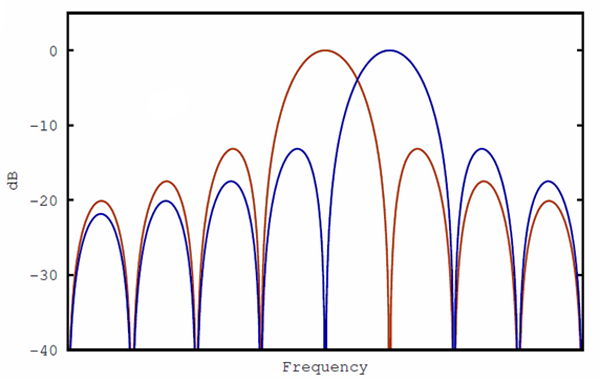

奈奎斯特區和混疊,1、3和4區中顯示的是2區一個信號的鏡像,基礎信號(Fa)和諧波或者諧波含量的鏡像

可以使用下面的算法來確定諧波或者諧波含量合成頻率位置:

Fharm=N ×Ffund

IF (Fharm=Odd Nyquist Zone)

Floc=Fharm Mod Ffund

Else

Floc=Ffund-(Fharm Mod Ffund)

End

這里N是感興趣的諧波的整數。

例如,采樣率為2500MHz,基礎頻率是1807MHz,將會在第一奈奎斯特區有一個693MHz的諧波分量。

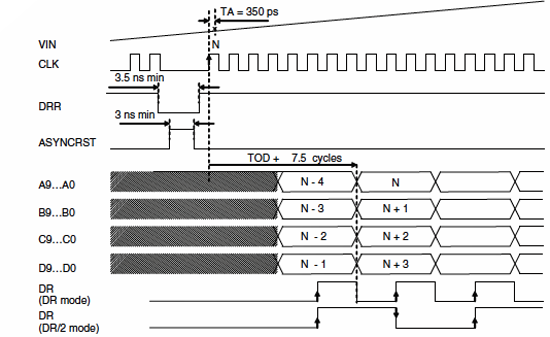

前面對頻譜做了一些解釋,另一個重要因素是這些設備和FPGA采用什么方式連接。許多高性能的數據轉換器使用一個工作在較低數據速率的多路復用器來實現轉換器的采樣率—一般都是下圖所示的使用FS/4或者FS/2,圖中顯示的是轉換器的數據流在4條并行的10-bit總線(A, B, C, and D)上的分布:

通常情況下,這些數字接口采用的是并行LVDS總線,這樣它們會占用許多的FPGA I/O管腳,但是,并行接口的延遲最小,并且由于它們使用差分信號傳遞方式,也可以降低輻射噪聲,這在高性能系統中是非常重要的。

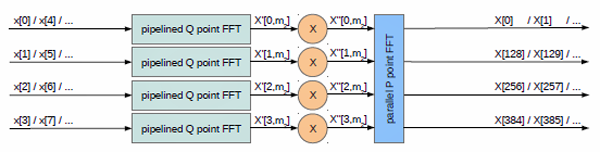

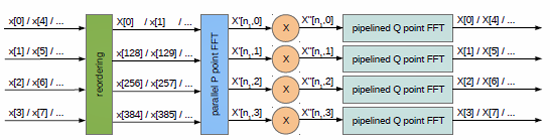

收到FPGA發出的4個數據流,你可能想知道在FPGA內部是如何處理數據的,在許多應用中,包括通信處理器和射電天文,都使用的一個常用的方法是使用組合或者分離的FFT結構,如下面兩個圖所示:

使用4個128點的FFT流水線,加上旋轉因子和1個并行4點FFT,組合成512點的FFT

分離512點FFT,與組合FFT相反。與組合FFT不同的是,在前兩個階段,對高速輸入有一個重組的操作

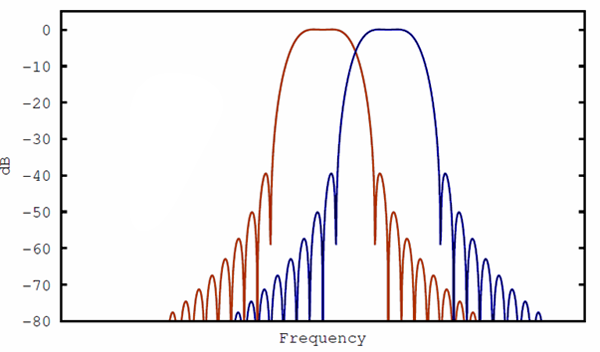

因為這些真實的數據樣本,你將需要尋找一個優化的方法以便于在FFT結構中對這些數據進行處理,高效的、大FFT的實現是一個復雜的研究領域,但是在FFT之前,許多應用使用加權疊接相加(WOLA)結構來改善頻譜泄漏。下面兩個圖顯示了使用一個矩形窗口的普通FFT和使用WOLA的FFT的行為對比:

使用普通FFT矩形窗口的相鄰信道

使用WOLA方法的相鄰信道,顯示了更少的頻譜泄漏

然后,根據應用的需求,對這些合成的FFT數據進行后處理。

---->end<----

-

頻率

+關注

關注

4文章

1459瀏覽量

59163 -

高性能

+關注

關注

0文章

156瀏覽量

20385

發布評論請先 登錄

相關推薦

正確理解時鐘器件的抖動性能

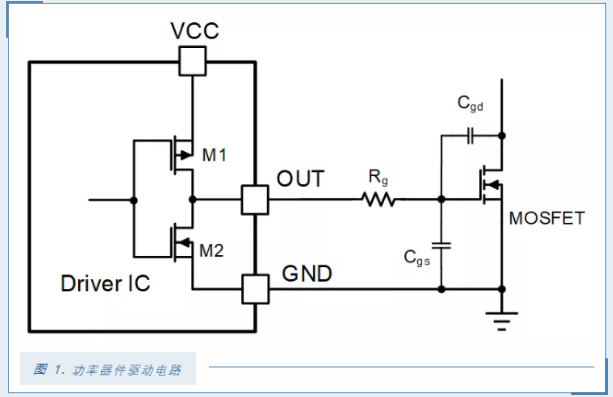

應用筆記:正確理解驅動電流與驅動速度

如何正確理解GaN?

正確理解DC/DC轉換器

正確理解AC耦合電容在高頻電路設計中的作用

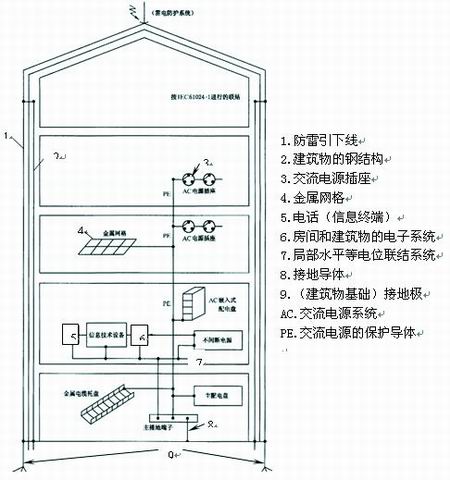

正確理解和測試信息技術設備的接地

正確理解電路保護設計及器件選擇資料下載

選型必讀:正確理解電阻在電路中的作用資料下載

如何正確理解嵌入式軟件可靠性設計?資料下載

正確理解和使用高性能設備

正確理解和使用高性能設備

評論