1 引言

1947 年 AT&T 貝爾實驗室的科學家 John Bardeen、Walter Brattain 以及 William Shockley 發明世界上第一個半導體晶體管,70 多年來,半導體集成電路得到快速發展。特別是自 1960 年代開始,芯片上的元器件數目幾乎每 12 個月就增加一倍,2000年后,半導體集成電路工業發展到了納米(nm)時代。隨著集成電路特征尺寸的逐步縮小到亞納米 100 nm 范圍,在材料、器件結構、工藝以及可靠性等方面出現了一系列新的問題。主要問題包括熱載流子效應、短溝道效應、體硅器件的閂鎖效應、功耗、寄生電阻、電容增加等等。

為解決這些問題,大量的科研人員進行了大量創新,開發了很多新的技術,如深溝槽隔離技術、HALO 結構、應變硅技術、High K 材料、Low K 材料等等。在眾多的新結構器件技術中,絕緣體上硅(SOI: Silicon on Insulator)技術以其獨特的結構有效地克服了體硅集成電路的很多不足,充分發揮了體硅集成電路技術的優勢,特別是在提高開關速度、減少寄生效應等方面。SOI 技術正逐步成為制造高集成度、高速度、低功耗、高可靠性超大規模集成電路的主流技術[1-5]。

本文就 SOI 技術的發展歷史、主要技術及應用、問題與挑戰以及將來趨勢做出整理和分析。

2 SOI 結構

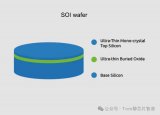

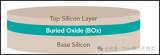

SOI 有兩種基本結構,一種是硅-絕緣層型的傳 SOI 結構,如圖 1(a)所示;另一種是硅-絕緣層-硅三明治型的新型 SOI 結構,如圖 1(b)所示。兩種基本結構的主要差別是襯底類型不同。

第一種結構中,最熟悉的例子是藍寶石上外延硅(SOS:Silicon on Sapphire),該結構是在藍寶石單晶作為襯底,在上面進行外延生長一層單晶硅的薄膜,然后在制作相應的器件。SOS 結構是由 Manasevit 和 Simpson[6]在 1963 和 1964 年間做出。這種結構能提供理想的隔離,并減小 PN 結底部的寄生電容,適合于制作高速大規模集成電路,實現高速和低功耗。一般多采用這種工藝制作 CMOS 電路(互補金屬-氧化物-半導體集成電路),即 CMOS/SOS 電路。SOS 是一種異質外延結構,硅膜的缺陷密度較大,因而少數載流子壽命較短(1~10 ns),不適于制作雙極器件和電荷耦合器件。

第二種結構中,絕緣層(如 SiO2)位于硅襯底上,在絕緣層上面再由一層單晶硅薄層,形成硅襯底-絕緣層-單晶硅組成的三明治結構。由于頂層的單晶硅薄膜近乎完美的單晶硅,同時它和中間層的界面態很低,且整體應力較小。MOS 等器件能很好地在頂層的單晶硅襯底中制作,且表現出與體硅材料近似的性能,這使得這種結構的 SOI 材料成為當今世界制作 SOI 集成電路元器件的主要材料。下面將重點講解這種類型的 SOI 技術。

3 SOI 材料的制備技術

3.1 注氧隔離技術(SIMOX)

SIMOX(Seperation by Implant of Oxygen)技術最早由日本的 Izumi 等人在 1970 年代提出[7], 原理很簡單,首先將氧注入單晶硅中,為了形成符合化學配比的二氧化硅埋層,氧的注入能量為 200 KeV 劑量為 2e18 cm-2 的氧離子。如此高劑量注入給硅片表面帶來很高濃度的缺陷,為了防止硅在注入過程中非晶化并促使注入的氧離子形成致密的 SiO2 以及形成良好的 Si/Si02 界面,注入過程中需要在 600 ℃ 的環境下實現,并且在注入后必須高溫(1 300℃)長時間(5 h)來退火,因而 SIMOX 材料成本較高。

在 SIMOX 技術中,注入劑量越大,注入的成本就越高,引入的缺陷就越多,針對這些問題,各地研究者進行不斷持續的改進,到了 1990 年代,Nakashima 和 Izumi 提出了低劑量注入的方法來[8]降低表面缺陷,他們發現在注入能量在 180 KeV 和劑量在 1.4e18 cm-2 以下時,表面位錯密度會有明顯下降,如圖 2 所示。

但是注入的劑量不能太低,太低的話,氧的分布曲線是不對稱得高斯分布[9],如圖 3 所示,形成的二氧化硅不連續。而劑量太大的話則容易造成 Silicon 空洞,如圖 4 所示。劑量在 1.4e18 cm-2 時,二氧化硅層連續且均勻。

隨著工藝制程的不斷進步,對晶圓(Wafer)表面的缺陷要求也越來越高,SIMOX 制備方法就遇到了瓶頸。

3.2 鍵合技術(WB)

1980 年代開始,已經出現了一些鍵合技術(WB:Wafer Bonding),它的原理十分簡單:將兩片被氧化的晶圓(或者一片被氧化)鍵合在一起,將其中的一片硅片用于研磨、拋光或者化學腐蝕等方法減薄到合適于 SOI 器件要求的厚度,稱為 Device wafer,另一片晶圓作為機械支撐襯底,稱為 Handle wafer,如圖 5 所示。

由于鍵合技術的減薄主要依賴機械拋光、研磨或者化學腐蝕等方法來實現,一方面表面的 EPI 層不可能做得很薄,一般>2μm。另一方面,表面比較粗糙,均勻性比較差,如圖 6 所示,這樣就限制了該技術的應用。

3.3 智能剝離技術(Smart-cut)

智能剝離技術(Smart-cut)是由 M.Bruel 等人在 1995 年提出的[10],它是建立在離子注入和健合兩種技術相結合的基礎上。其原理是利用 H+(或者 He+)注入在硅中形成注入層(深度通常小于 1μm),將注氫片與另一支撐片健合(兩片中至少有一片表面有一層熱氧化的 SiO2 層),經適當的處理后,使注氫片從粒子注入層完整分裂,形成 SOI 結構,如圖 7 所示。然后對 Wafer 表面進行拋光處理,再使用外延的方式達到想要的 Silicon 厚度。

Smart-cut 技術的優點主要包括。①H+ 離子的諸如劑量約為 1e16 cm-2,比 SIMOX 注氧劑量要低 2 個數量級,可采用普通的離子注入機就可以完成。②因為是離子注入形成表面的 Silicon,其厚膜均勻性較好,厚度可控,厚薄可用注入能量來控制。③表面缺陷小,單晶性保持較好。④ 埋氧化層(BOX: Buried Oxide)是由熱氧化形成的,具有良好的 Si-SiO2 界面。⑤ 玻璃下的硅片仍然可以繼續注氫鍵合,循環使用,大大降低了制備成本。

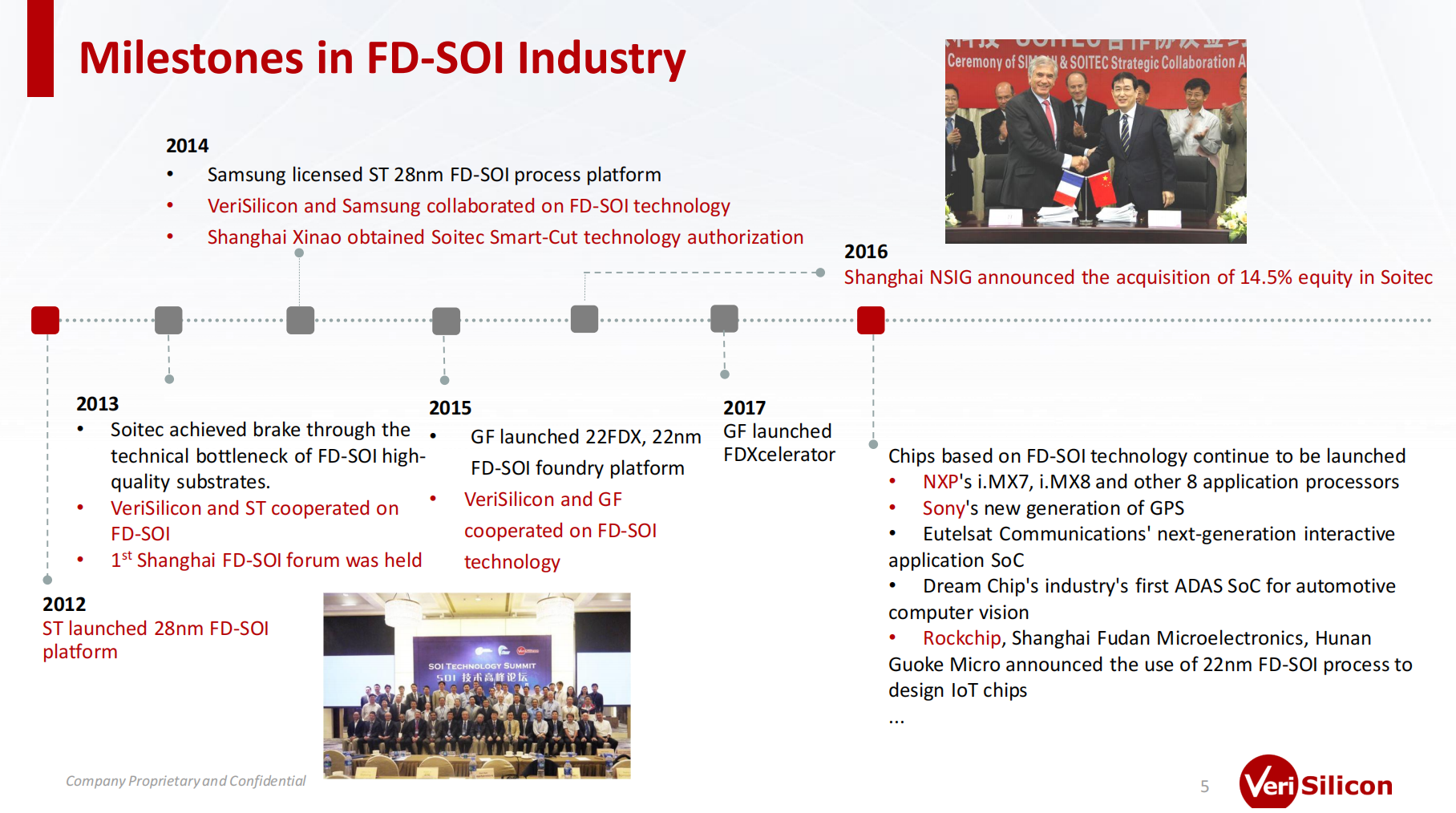

基于上述優點,Smart-cut 技術在 SOI 材料制備技術中成為最具競爭力的一項技術。自 1995 年以來的短短 20 年里,這種技術得到飛速發展。目前,法國的 Soitec、日本的信越、中國***環球晶圓等公司已經能使用該技術提供大量商用的 SOI 硅片。2014 年,Soitec 還和上海新傲科技股份有限公司(Simgui)達成了有關射頻和功率半導體市場 200 mm SOI 晶圓的戰略伙伴關系并簽署了經銷協議,合作主要包括許可和技術轉移協議。其中,上海新傲科技可以用 Soitec 的 Smart-Cut 專利技術生產 200 mm SOI 晶圓。

4 SOI 主要制程技術及應用

4.1 RF SOI

當射頻芯片在體硅基上形成時, 硅的半導特性引起了基板中射頻信號的衰減。同時, 硅基半導體元器件特性還會導致寄生干擾(串擾噪聲)的傳輸。如將 SOI 應用于高阻抗基板上能夠顯著地改善芯片的高頻特性, 極大地降低電阻衰減以及串擾噪聲。

RF SOI 稱為射頻絕緣體上硅技術,該技術不僅可以提供無與倫比的集成度,還可以給窄帶物聯網帶來優越的低功耗性能,如圖 8 所示。現今大多數 RF應用在智能手機、WiFi 等無線通信領域,其中絕大多數使用了 RF SOI 工藝制造。RF SOI 對 RF 射頻與系統芯片的集成、支持 5G 毫米波技術以及在超低功耗的實現,在手機網絡轉向 LTE 或 5G 的過程中,設備設計會更加復雜,并且隨著 5G 與物聯網的不斷進化,RF SOI 具有廣泛的應用前景,預計每年有 15% 的年增長率,如圖 8 所示。

今天,世界上主要代工廠都在大力發展 RF SOI 技術,如 Global Foundries(GF)、TowerJazz、臺積電、聯電、意法半導體、索尼以及國內的中芯國際、華虹宏力等等。他們均擁有 200 mm RF SOI 晶圓廠產能,較大的代工廠正在生產 300 mm RF SOI 晶圓,如 GF、TowerJazz、臺積電和聯電等等,工藝節點從 130 nm 到 45 nm 不等。例如,GF 正在兩座晶圓廠:紐約 East Fishkill 和新加坡推出 300 mm RF SOI 晶圓,包括 130 nm 和 45 nm 工藝,表 1 為 RF SOI 技術能力及應用市場。Tower Jazz 也在日本的晶圓廠增加 300 mm RF SOI 晶圓產能,該工藝基于 65 nm。聯電和臺積電也計劃進軍 300 mm。

300 mm 晶圓相比于 200 mm 有以下優點:① 集成度是 300 mm 晶圓最大的優勢,元器件的特征尺寸可以做到 90 nm 以下,可以在更小的面積內集成更多的元器件,滿足更加復雜的設計。② 300 mm 提供了更多的過程控制和完全自動化,產品的公差、可重復性和良品率優于 200 mm。③ 300 mm 晶圓采用銅互連層,寄生電阻、電容大大降低,同時元器件間的干擾或耦合也可以大大降低。

4.2 FD SOI

FD-SOI 技術又稱完全耗盡型絕緣體上硅(Fully Depleted Silicon On Insulator),是由伯克利教授胡正明在 2000 年發明的。FD-SOI(圖 9)可以實現對納米節點工藝制程下晶體管電流的有效控制和閾值電壓的靈活調控,因而 21 世紀伊始,以 Leti、Soitec、 STM 等為代表的歐洲半導體科研機構和公司開始投入該技術的研發[11]。

與體硅材料相比,FD-SOI 具有如下優點:① 減小了寄生電容,提高了運行速度。② 由于減少了寄生電容,降低了漏電,具有更低的功耗。③ 消除了閂鎖效應。④ 抑制了襯底的脈沖電流干擾,減少了軟錯誤的發生。⑤ 與現有硅工藝兼容,還可減少工序,成本比較低。從 ISB CEO Handel Jones 公布的數據看,目前 22 nm FD-SOI 的成本將和 28 nm HKMG成本相近。如果線寬再繼續縮小,例如到 12 nm 節點,FD-SOI 的成本將顯著低于 FinFET,12 nm FD-SOI 的成本比 16 nm FinFET 低 22.4%,比 10 nm FinFET 低 23.4%,比 7 nm FinFET 低 27%。這是因為 12nm FD-SOI 的掩膜數量要少一些,抵消了其襯底成本高于 FinFET 的部分。

4.3 Power SOI

Power SOI 又稱為功率絕緣體上硅技術,是 SOI 技術應用的另一個大的領域。在傳統的體硅功率集成電路中,由元器件注入襯底的載流子往往會被與其臨近的大面積的功率器件所收集,引起不必要的串擾甚至引起功率器件的誤開啟,這些限制了以 PN 節為隔離的功率器件的應用。而 SOI 技術,元器件在縱向可以通過埋層氧化層(BOX, Buried Oxide Layer)實現縱向隔離,在橫向可以通過深溝槽氧化層(DTI, Deep Trench Isolation)實現橫向隔離,元器件可以分別做到不同的隔離島上,避免了以 PN 節為隔離體硅功率集成電路的很多缺點,如串擾、閂鎖效應、大泄漏電流以及大面積的隔離區等問題,提高了電路的集成密度。同時,由于 SOI 技術具有比體硅元器件更低的泄漏電流,使其可以在更高電壓、更高的溫度下進行工作。圖13為兩種典型的功率SOI器件截面圖,圖 13(a)為高壓 LDMOS 產品,圖 13(b)為超高壓 LDMOS 產品,它們都分別做到不同的隔離島上,橫向、縱向都與其他元器件用介質隔離。

5 SOI 技術的主要問題與挑戰

雖然 SOI 技術比傳統的體硅技術具有隔離效果好、寄生效應小、泄漏電流低、集成密度高等優點,但還有很多不足,限制了該技術大規模的應用。

5.1 SOI 晶圓成本偏高

現有 SOI 晶圓的制造成本比較昂貴,在采購價格上比普通硅基晶圓要貴出幾倍甚至幾十倍,限制了其大規模的應用。現有世界上主流的技術有 WB 技術和 Smart-cut 技術,其中,WB 技術是由兩片晶圓經過鍵合、減薄、拋光等一系列步驟完成,增加了額外的工藝成本;同時,其中的一片會犧牲掉,也將計算在 SOI 的成本之中。而 Smart-cut 技術,目前還是 Soitec 的專利,其他廠商需要得到專利授權、轉讓等方式才能獲得;同時,該技術也需要注入、分離、拋光、外延等工序,工藝成本也比較昂貴。

5.2 浮體效應

SOI 晶體管相對襯底會形成一個寄生電容。電荷在電容上積累,而造成不利的效應,被稱作浮體效應。由于浮體效應導致寄生雙極晶體管效應、記憶效應、遲滯效應、Kink 效應等等。研究發現,浮體效應不僅可以嚴重影響模擬電路的特性,還會引起數字電路的邏輯失真和功耗增大。為了抑制浮體效應,研究人員使用了各種方法,如用氬(Ar)注入引入復合中心、源區注入鍺(Ge)減小禁帶寬度、使用超薄 FD SOI 等等,但是這些工藝復雜,控制困難,往往達不到理想的效果。近年來材料及器件制備技術的發展,問題有了明顯改善。

5.3 SOI 晶圓導熱性能差

SOI 產品的縱向隔離 BOX 層次以及橫向隔離的溝槽中,往往采用 SiO2、Poly 等材質,這些材質在隔離泄漏電流、提高耐壓的同時,也使得 SOI 元器件的散熱性能變得比傳統的體硅器件差很多。特別是針對功率的 SOI 元器件,散熱性能差使得安全工作區(SOA, Safe Operation Area)縮小,限制了其使用范圍。除非增加晶圓表面的金屬面積來增加散熱,或者通過額外的工藝,使隔離島中器件的熱從襯底中散出。這些一方面增加了元器件的面積,另一方面增加工藝的難度,提高了生產成本。

5.4 背柵效應

SOI 元器件中,背面柵壓通過襯底、埋氧化層對器件的體區產生影響。在不同的背柵條件下,體區的耗盡層寬度會隨著襯底電壓變化,進而影響到器件的性能。例如閾值電壓電壓隨著背面柵壓的增加而線形減小。器件的耐壓也隨著背面柵壓的變化而變化,對于具有上下管(high side 和 low side)的器件,需要兼容在不同背面柵壓下耐壓都能滿足需求,有時會設計出更高耐壓的器件,這樣在面積上便會有一定的犧牲。

5.5 SOI 產業鏈不夠完善

經過幾年的發展,雖然在全球逐漸打造出較為完整的產業鏈,覆蓋材料、設計、代工、封測、應用等各個環節,具備了一定的產業基礎,但是起步晚、欠完善,導致 SOI 沒能大規模地應用,與傳統的 FinFET 展開競爭。隨著各個廠商的努力,特別是中國力量的加入,SOI 具有無與倫比的優勢,將會帶動 SOI 產品更大規模的應用。隨著 5G、IoT、智能駕駛時代的來臨, SOI 技術將得到更加廣泛的使用。

6 結語

SOI 技術從 1960 年代誕生以來,人們研究開發了多種 SOI 技術,在眾多的技術中,直接鍵合和智能剝離技術在獲得 SOI 材料中最具潛力,特別是智能剝離技術,已大量應用于現有產品中。如 RF SOI、FD SOI、Power SOI 等技術,已在 5G、loT、汽車、家電等領域得到廣泛應用。雖然 SOI 技術也有一些劣勢、產業鏈還不很完善,但是它有傳統體硅器件無法比擬的優勢,相信在不久的未來,SOI 技術將大規模地爆發。

-

集成電路

+關注

關注

5381文章

11390瀏覽量

360897 -

絕緣

+關注

關注

1文章

427瀏覽量

21818 -

SOI

+關注

關注

4文章

68瀏覽量

17620 -

硅技術

+關注

關注

0文章

5瀏覽量

4046

原文標題:絕緣襯底上的硅技術 SOI 發展與應用分析

文章出處:【微信號:appic-cn,微信公眾號:集成電路應用雜志】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

解讀芯原股份基于FD-SOI的RF IP技術平臺:讓SoC實現更好的通信

IBS首席執行官再談FD-SOI對AI的重要性,在≥12nm和≤28nm區間FD-SOI是更好的選擇

芯原戴偉民博士回顧FD-SOI發展歷程并分享市場前沿技術

硅片和soi這兩種材料,他們的不同之處是什么呢?

意法半導體突破20納米技術節點,打造極具競爭力的新一代MCU

上海微技術研究院標準180nm硅光工藝在八英寸SOI上制備了硅光芯片

射頻前端底層技術的卓越性能,RF-SOI為5G賦能

半導體襯底材料的選擇

碳化硅單晶襯底的常用檢測技術

絕緣襯底上的硅技術 SOI發展與應用分析

絕緣襯底上的硅技術 SOI發展與應用分析

評論