近日,全球知名的EDA工具廠商新思科技(Synopsys)宣布,面向三星7LPP(7nm Low Power Plus)和更先進(jìn)工藝的良率學(xué)習(xí)平臺設(shè)計(jì)取得了重大突破,這將為三星后續(xù)5nm、4nm、3nm工藝的量產(chǎn)和良品率的提升奠定堅(jiān)實(shí)基礎(chǔ)。

周所周知,隨著半導(dǎo)體制程工藝的不斷推進(jìn),晶體管的大小也越來越逼近物理極限,芯片的設(shè)計(jì)和生產(chǎn)也變得更加的復(fù)雜,良率的提升也越來越困難。因此要想提高芯片的良率,就需要對各個(gè)環(huán)節(jié)進(jìn)行細(xì)致的分析。

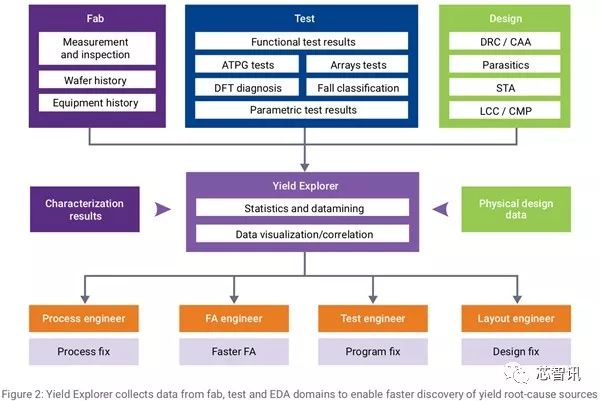

為此新思科技打造了量產(chǎn)探索平臺(Yield Explorer),這是一種復(fù)雜的芯片量產(chǎn)良品率學(xué)習(xí)平臺,可用來分析芯片設(shè)計(jì)、晶圓廠生產(chǎn)、產(chǎn)品測試三大方面的數(shù)據(jù),以便幫助工程師找到缺點(diǎn)、改進(jìn)良品率、提高產(chǎn)能。

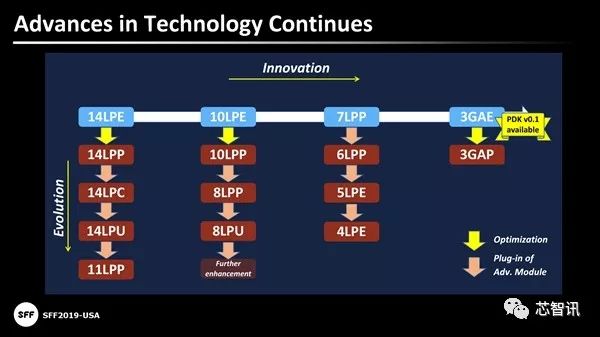

根據(jù)此前三星公布的路線圖顯示,三星工藝近期有14nm、10nm、7nm、3nm三個(gè)重要節(jié)點(diǎn),其中14nm會演化出11nm,10nm會演化出8nm,7nm則會演化出6nm、5nm、4nm。

而每種工藝往往又會根據(jù)性能、功耗的不同而分為多個(gè)版本,比如14nm分成了14LPE、14LPP、14LPC、14LPU,3nm則分成3GAE、3GAP,預(yù)計(jì)會采用全新的材料。

不久前,在三星在韓國舉行的晶圓代工制造論壇上,負(fù)責(zé)晶圓代工業(yè)務(wù)的三星副總裁Jung Eun-seung對外公布了三星在半導(dǎo)體制造工藝上的進(jìn)展。他透露,三星7nm EUV工藝將于2020年1月份量產(chǎn)。此外他還透露三星目前已經(jīng)完成了5nm FinFET工藝的技術(shù)研發(fā),有望在2020年上半年進(jìn)入量產(chǎn)。4nm則將在今年下半年完成開發(fā),新思的新平臺將在其中發(fā)揮巨大作用。

再之后的重大節(jié)點(diǎn)就是3nm了,三星此前宣布3nm節(jié)點(diǎn)將使用GAA環(huán)繞柵極晶體管技術(shù),三星通過使用納米片設(shè)備制造出了MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應(yīng)管),該技術(shù)可以顯著增強(qiáng)晶體管性能,主要取代FinFET晶體管技術(shù)。

-

芯片

+關(guān)注

關(guān)注

453文章

50387瀏覽量

421782 -

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

26998瀏覽量

216254 -

三星電子

+關(guān)注

關(guān)注

34文章

15855瀏覽量

180920 -

新思科技

+關(guān)注

關(guān)注

5文章

787瀏覽量

50304

原文標(biāo)題:新思科技助力,三星5nm/4nm/3nm工藝再加速

文章出處:【微信號:icsmart,微信公眾號:芯智訊】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

臺積電產(chǎn)能爆棚:3nm與5nm工藝供不應(yīng)求

AI芯片驅(qū)動(dòng)臺積電Q3財(cái)報(bào)亮眼!3nm和5nm營收飆漲,毛利率高達(dá)57.8%

臺積電3nm/5nm工藝前三季度營收破萬億新臺幣

消息稱臺積電3nm/5nm將漲價(jià),終端產(chǎn)品或受影響

概倫電子NanoSpice通過三星代工廠3/4nm工藝技術(shù)認(rèn)證

臺積電3nm工藝穩(wěn)坐釣魚臺,三星因良率問題遇冷

三星與新思科技攜手,備戰(zhàn)2nm工藝量產(chǎn)

三星電子開始量產(chǎn)其首款3nm Gate All Around工藝的片上系統(tǒng)

三星電子:加快2nm和3D半導(dǎo)體技術(shù)發(fā)展,共享技術(shù)信息與未來展望

臺積電升級4nm N4C工藝,優(yōu)化能效與降低成本

三星電子澄清:3nm芯片并非更名2nm,下半年將量產(chǎn)

臺積電擴(kuò)增3nm產(chǎn)能,部分5nm產(chǎn)能轉(zhuǎn)向該節(jié)點(diǎn)

三星電子3nm工藝良率低迷,始終在50%左右徘徊

三星3nm良率 0%!

三星突破4nm制程良率瓶頸,臺積電該有危機(jī)感了

新思科技助力三星5nm/4nm/3nm工藝再加速

新思科技助力三星5nm/4nm/3nm工藝再加速

評論