與我在校期間在籃球隊中茁壯成長的父親不同,我在試訓期間幾乎無法反彈。毋庸置疑,我在開始之前就退出了運動。雖然我成為NBA職業球員的夢想破滅了,但后來我發現了我對武術的熱情。我從來沒有真正開始處理籃球,但至少在武術中,我可以從我的腳上反彈以迎接我的對手。

不能反彈籃球是一回事。然而,不了解電子設備中的接地反彈對于您的電路來說可能是非常有問題的。要想成為電路板,必須了解接地反彈對電路的影響。通過考慮接地反彈減少技術,您可以最大限度地減少設計中信號完整性的接地反彈。保護您的設計免受信號完整性問題的影響。

什么是接地反彈?

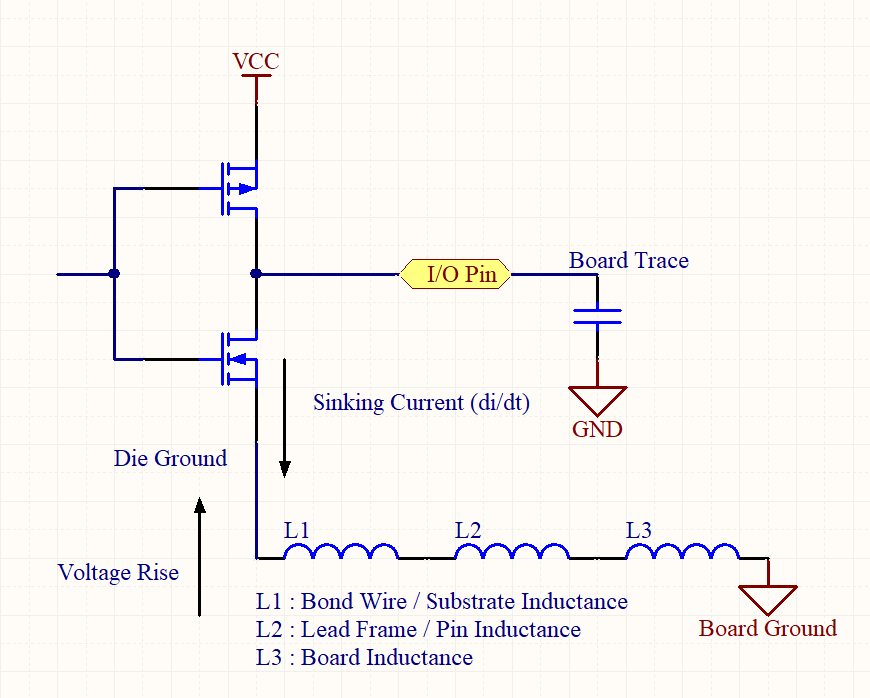

要了解接地反彈,您需要深入了解形成的晶體管的基礎知識集成電路(IC)的核心。下圖顯示了微控制器和隨機存取存儲器(RAM)等IC的互補金屬氧化物半導體(CMOS)電路。

CMOS邏輯門中的接地反彈

在大多數設計中,輸出引腳通常連接到容性負載。當輸出引腳置為邏輯'1'時,負載完全充電至VCC。當輸出關閉為邏輯'0'時,電流快速從輸出流向地。

在理想情況下,IC封裝和電路板的接地將保持在相同的電壓。然而,在大多數實際情況下,由于鍵合線,引線框架和電路板電感本身,在芯片接地和電路板接地之間存在電感。

當電流沖過電感時,在芯片接地和電路板接地之間建立電壓。這會導致芯片接地和電路板接地瞬間處于不同電壓電平的現象,從而導致接地反彈。

接地反彈如何影響電路

h2>

在最低水平,地面反彈不會對電子設備造成任何干擾。但是,當接地反彈很明顯時,特別是當多個輸出同時關閉時,器件的地電平上升到可能影響其他操作的水平。

例如,微控制器經歷地面反彈可能它的地面轉移到1.5V。工作在3.3V且連接到微控制器的邏輯IC可將邏輯“0”信號解釋為“1”,因為它由于器件接地的電壓電平而接收1.5V邏輯“低”信號。/p>

正在經歷地面反彈的設備也可能誤讀其他組件的輸入。例如,邏輯“高”信號會被誤解為“低”,因為輸入引腳的電壓為1.8 V而不是3.3V,這是由于器件接地的上升所致。這低于2.31V的最小邏輯高電壓。

減少接地反彈的技巧

減少接地反彈影響的最簡單方法是在受影響的元件附近放置一個旁路電容。當輸出邏輯電平快速變化時,這將使電流流入和流出電容器。重要的是將旁路電容盡可能靠近元件的VCC引腳放置,以最大限度地降低接地走線的總電感。

將一個電阻串聯到輸出負載可以減少瞬態時間變化的信號。這僅適用于輸出不是時序敏感的情況,例如并行SRAM的地址總線。此方法適用于觸發輸出的控制引腳,如繼電器或LED。

當所有輸出同時驅動為低電平時,接地反彈的影響最大。那時芯片的電壓差大幅增加。為了防止這種情況,請嘗試分散輸出驅動低的時間。在這里,甚至額外的毫秒延遲也會產生顯著的差異。

作為一般規則,你應該避免在易受攻擊的邏輯IC上放置毛刺敏感信號,如RESET,CHIP SELECT或SET地面反彈問題。總的來說,靠近GND引腳的輸出引腳可以減少接地反彈問題。因此,您應該將關鍵信號放在GND引腳旁邊的引腳上。

旁邊放置旁路電容邏輯組件。

檢測設計中的潛在接地反彈問題

最后,放置旁路電容器是一種適用于廣泛的設計。它保持良好的電力傳輸網絡并可靠地減少地面反彈。為了最大限度地減少設計中不受控制的電壓降并發現其他潛在的功耗問題,請嘗試使用Altium PDNAnalyzer?。

使用此工具,您可以同時模擬多個網絡的電力傳輸,并輕松識別直流電壓或電流密度的問題。但最好的部分是它位于AltiumDesigner?的PCB設計軟件中,可以在同一個統一的設計環境中從原理圖轉換到仿真。

地面反彈是否會對您的設計造成嚴重破壞?獲得Altium專家的幫助。

-

pcb

+關注

關注

4317文章

23012瀏覽量

396368 -

電路設計

+關注

關注

6665文章

2430瀏覽量

203362 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42983

發布評論請先 登錄

相關推薦

【轉】電源的電磁干擾技術設計要點

計算機控制抗干擾技術設計

如何降低dc to dc電路的輻射發射?

如何降低dc to dc電路的輻射發射?

模擬電子技術設計

如何地面反彈降低技術設計電路?

如何地面反彈降低技術設計電路?

評論