當(dāng)夏天結(jié)束時,我聚集了我的家人,前往州博覽會,感受神奇的興奮。在這一年中,展覽會場地空無一人,小小的塵埃滾過貧瘠的景觀。但是,當(dāng)博覽會開幕時,展覽場地充滿活力。有大象耳朵的攤位,有動物和示威的建筑物,還有帶尖叫孩子的游樂設(shè)施。這是一個充滿活力的雜耍行為。

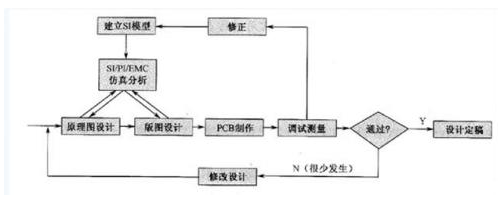

將印刷電路板與高速信號放在一起,包括設(shè)計,組件和高速信號的雜耍行為。這些高速信號為不必要的傳輸線創(chuàng)造了機會,從而對電路板造成嚴(yán)重破壞。大部分混亂都發(fā)生在PCB布局本身內(nèi)。

了解布局造成的這種破壞可以在鋪設(shè)電路板時實現(xiàn)分辨率。了解您所應(yīng)用的布局技術(shù)是否是PCB設(shè)計中信號完整性分析的最佳實踐。可以通過執(zhí)行冗長的鉛筆分析或使用信號完整性模擬工具來發(fā)現(xiàn)它。閱讀完之后,我會讓你決定你認(rèn)為對你的電路板更有效。

信號完整性模擬工具不足

信號完整性模擬工具,魔術(shù)變得混亂。阻抗計算器返回錯誤的阻抗計算。計算與PCB設(shè)計規(guī)則中定義的材料的層疊和介電常數(shù)相矛盾。模擬器假設(shè)建模的返回路徑,因此如果地平面中存在不連續(xù)性,則它們不包括在計算中。 3D場解算器返回非常錯誤的差分對的計算阻抗。

該工具很簡單,不支持PCB布局的常規(guī)選項,同時牢記設(shè)計規(guī)則。這包括剛性彎曲的規(guī)則和模擬。其仿真環(huán)境產(chǎn)生難以理解的波形。進(jìn)一步研究需要復(fù)雜的手動命令來評估普通操作。對于其3D場解算器也是如此。由于用戶界面沒有選擇來分析電氣長跡線,因此在布置電路板以實現(xiàn)高速信號完整性時沒有信心。

解釋結(jié)果的時間間隔

< p>花費數(shù)小時來分析模擬工具結(jié)果以分析炫目錯誤。瀏覽菜單需要細(xì)致的工作。時間沉沒穿過阻抗計算器,揭示了使用不正確的參數(shù)來計算走線阻抗。花時間發(fā)現(xiàn)模擬器使用的參數(shù)與PCB布局的凈規(guī)則不匹配。誰會猜到?

如果平面材料的固有電容和介電常數(shù)沒有正確的參數(shù),那么計算出的阻抗確實會減少高速信號的反射和振鈴。

隱藏的環(huán)境異常(例如缺少鉆取文件)會導(dǎo)致模擬器失敗。鑒于設(shè)置模擬所需的大量PCB編輯器和設(shè)置,丟失鉆孔文件會導(dǎo)致錯誤,導(dǎo)致設(shè)置過程混亂。它會導(dǎo)致對編輯器和設(shè)置菜單中選擇的參數(shù)進(jìn)行質(zhì)詢和重新質(zhì)詢。

通過幫助頁面和應(yīng)用程序說明進(jìn)行搜索會導(dǎo)致在分析模擬高速信號以保證信號完整性的工具時浪費更多時間。最后,獲得說明模擬結(jié)果的波形經(jīng)常顯示垃圾。如果沒有優(yōu)雅的用戶界面可以在我的指尖上使用強大的工具來將它們正確地驅(qū)動到我的電路板上,這是令人沮喪的。在一天結(jié)束時,誠信仍然可以爭奪。

識別和解決完整性的合格工具

如果工具中的阻抗計算器使用了PCB設(shè)計規(guī)則中設(shè)置的材料參數(shù),那會不會很好?將工具端口信息存儲在其總體設(shè)計規(guī)則中以計算阻抗,可以確保印刷電路板將從制造商處返回,并使用正確的組件和布局來補充電路設(shè)計。

使用模擬器使用參數(shù)從PCB設(shè)計規(guī)則中獲得對結(jié)果的信心。在工程師和布局設(shè)計人員解決信號完整性問題和解決方案的那些日子里,獲取波形顯示在原理圖捕獲和PCB布局期間的仿真結(jié)果將有助于建設(shè)性地改進(jìn)設(shè)計。它消除了進(jìn)行分析的猜測,并從鉛筆沉思中應(yīng)用最佳實踐,等待PCB制造,然后驗證信號完整性。

AltiumDesigner?采用精確的波形分析

Altium Designer 18在PCB層堆棧管理器中有一個阻抗公式編輯器。通過下拉菜單可以在PCB布局環(huán)境中輕松訪問層堆棧管理器。阻抗公式編輯器包含適用于所有拓?fù)涞恼_路由阻抗公式,包括嵌入式,雙鏈路和差分網(wǎng)絡(luò)的微帶到帶狀線。在編輯器中可以輕松訪問每個拓?fù)涞哪J(rèn)公式。這允許直接訪問每個拓?fù)涞墓剑员阍诠ぞ咧休p松修改。作為替代方案,如果更方便,也可以通過查詢助手訪問和編輯阻抗公式。

通過層堆棧管理器輕松訪問阻抗公式編輯器

一旦反射和振鈴的阻抗已經(jīng)融入PCB布局,信號完整性模擬器可以設(shè)置為高分析速度信號行為。模擬器接受設(shè)計者定義的信號刺激。 PCB設(shè)計器還包括高速信號網(wǎng)絡(luò)的參數(shù)特性,如過沖和下沖值,飛行時間和電源網(wǎng)絡(luò)限制。

模擬器使用這些值在波形分析窗口中顯示結(jié)果。由此產(chǎn)生的波形顯示了信號完整性問題,例如由于PCB布局或濾波分立特性而在高速線路上引起的振鈴,反射,串?dāng)_或電壓降。 PCB設(shè)計人員能夠調(diào)整阻抗以實現(xiàn)最大信號完整性,并繼續(xù)執(zhí)行波形分析,直到設(shè)計無噪聲。

Altium Designer 18是一種功能強大且易于使用的原理圖捕獲和PCB布局工作時允許阻抗設(shè)置為高速軌跡的工具。其統(tǒng)一的環(huán)境使其易于使用,使您能夠在印刷電路板制造之前獲得設(shè)計中信號完整性所需的結(jié)果。

如果您正在尋找包含易于使用的EDA工具用于設(shè)計PCB布局以實現(xiàn)最大信號完整性的工具,請與Altium專家交談。

-

pcb

+關(guān)注

關(guān)注

4317文章

23010瀏覽量

396344 -

測試

+關(guān)注

關(guān)注

8文章

5167瀏覽量

126474 -

模擬信號

+關(guān)注

關(guān)注

8文章

1118瀏覽量

52404 -

華強pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

42983

發(fā)布評論請先 登錄

相關(guān)推薦

基于信號完整性分析的高速數(shù)字PCB的設(shè)計方法

高速電路信號完整性分析與設(shè)計—PCB設(shè)計

基于信號完整性分析的高速PCB設(shè)計

基于信號完整性分析的高速數(shù)字PCB板的設(shè)計開發(fā)

信號完整性分析及其在高速PCB設(shè)計中的應(yīng)用

PCB信號完整性有哪幾步_如何確保PCB設(shè)計信號完整性

基于信號完整性的高速PCB設(shè)計

基于信號完整性的高速PCB設(shè)計流程解析

高速PCB設(shè)計分析:如何進(jìn)行模擬和信號完整性的檢查?

高速PCB設(shè)計分析:如何進(jìn)行模擬和信號完整性的檢查?

評論