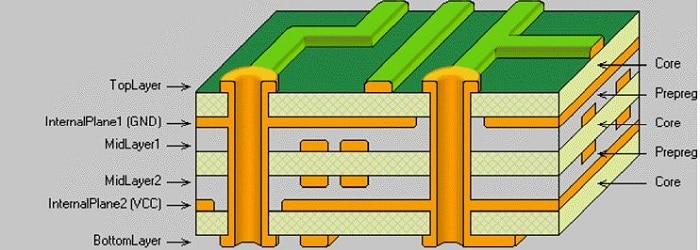

設計多層PCB,其中一個重要的事情是規劃多層PCB堆疊,以實現產品的最佳性能。設計不良的基板,選擇不當的材料,會降低信號傳輸的電氣性能,增加發射和串擾,并且還會使產品更容易受到外部噪聲的影響。這些問題可能導致間歇性操作,因為時序毛刺和干擾會大大降低產品性能和長期可靠性。

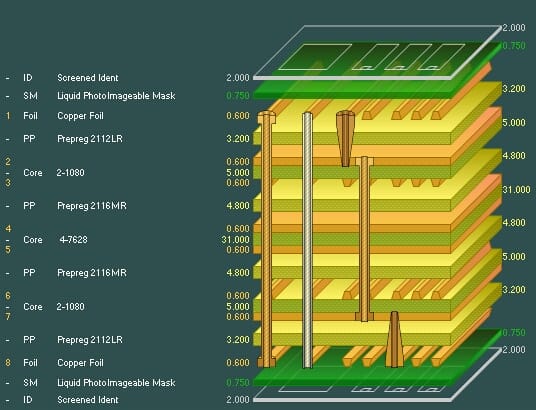

多層PCB疊層

相比之下,正確構建的PCB電路板基板可有效減少電磁輻射,串擾并改善信號完整性,從而提供低電感配電網絡。而且,從制造的角度來看,也可以改善產品的可制造性。

在產品生產過程中抑制噪音而不是試圖提升問題是有意義的。項目按時完成“正確的第一次”和預算意味著您可以通過縮短設計周期,縮短產品上市時間和延長產品生命周期來降低成本。

包含銅質平面的電路板允許在微帶線或帶狀線控制的阻抗傳輸線配置中路由的信號產生比雙層板上的不加區別的跡線少得多的輻射。信號緊密耦合到平面(接地或電源),減少串擾并提高信號完整性。

多層PCB中的平面可顯著減少兩層PCB上的輻射發射。根據經驗,與雙面PCB板相比,四層板的輻射將減少15 dB。

選擇多層疊層時,我們應考慮以下因素:

?信號層應始終與平面相鄰。這將嵌入平面之間的信號層數量限制為兩個以及頂部和底部(外部)層到一個信號。

?信號層應緊密耦合(<10 MIL)到其相鄰平面< br>?電源平面(以及地面)可用于信號的返回路徑。

?確定信號的返回路徑(將使用哪個平面)。快速上升時間信號采用最小電感的路徑,通常是最接近的平面。

?成本(凸臺最重要的設計參數)。

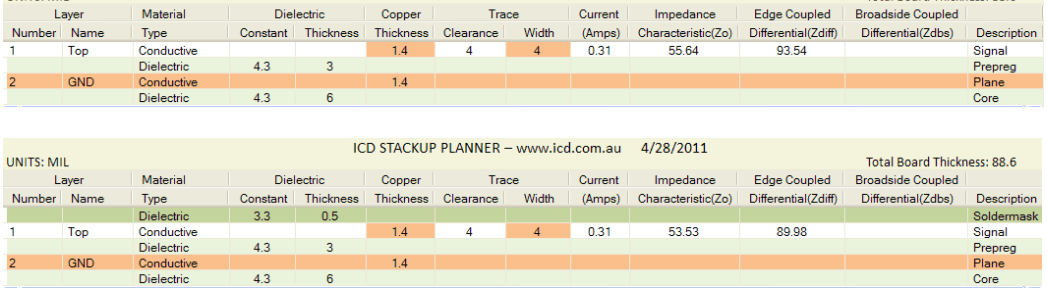

阻焊層 - 對阻抗的影響

由于印刷電路板通常覆蓋焊料掩模,因此在計算時應考慮保形涂層的影響阻抗。通常,焊接掩模將在薄跡線上將阻抗降低2至3歐姆。隨著跡線厚度的增加,焊料掩模的影響較小。

焊料掩模涂層的影響

< p>

上圖說明了阻焊層涂層對微帶阻抗的影響。這個例子是常用的液體可光成像阻焊膜,厚度為0.5 MIL,介電常數為3.3。

阻焊層使微帶特性阻抗下降2歐姆。差分阻抗為3.5歐姆。因此,如果您不考慮焊接掩模,那么

計算可能會超出3%到4%。

介電材料

最受歡迎的電介質材料是FR4,可以是芯材或預浸料(預浸漬)材料。

核心材料是薄電介質(固化玻璃纖維環氧樹脂),銅箔粘合到< br>雙方。例如:Isola的FR406材料 - 包括5,8,9.5,14,18,21,28,35,39,47,59和93 MIL核心。銅的厚度通常為?至2盎司(17至70微米)。

預浸材料是浸漬有未固化環氧樹脂的玻璃纖維薄片,在PCB制造過程中加熱和壓制時會硬化。 Isola的FR406材料 - 包括1.7,2.3,3.9和7.1 MIL預浸料,可以組合以達到所需的預浸料厚度。

最常見的疊層稱為“箔法”是具有銅箔的預浸料 - 在最外層(頂部和底部)上粘合到外部,然后在整個基材上與預浸料交替。另一種疊加被稱為“加密方法”,它與箔方法相反,并被老派軍事承包商使用。

讓我們來看看最常見的多層配置。

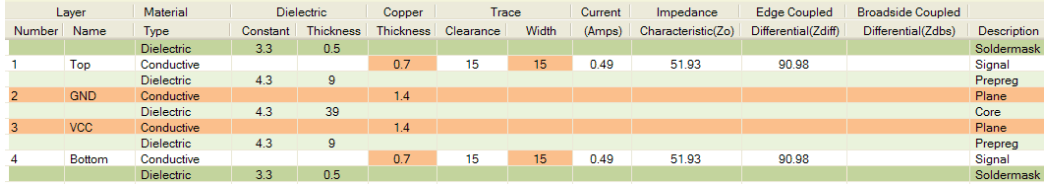

4層PCB疊層

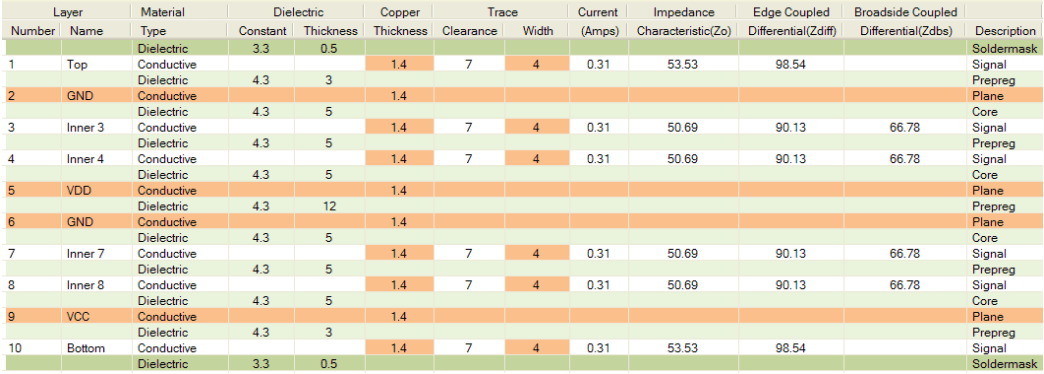

典型的四層板疊層如下所示。計算襯底的特性和差分阻抗

4層PCB疊層

通常看到四層板均勻堆疊。也就是說,四個均勻間隔的層,其中的平面位于中心。雖然這確實使得電路板對稱,但它并沒有幫助EMC。

另外,另一個常見的錯誤是讓平面緊密耦合在中心與信號之間的大電介質層和平面。這肯定會產生良好的平面間電容,但同樣無助于信號完整性,串擾或EMC - 這就是我們選擇在兩層上使用4層PCB的原因。

提高電容器的EMC性能四層板,最好將信號層盡可能靠近平面(<10 MIL),并在電源和地平面之間使用大芯(~40 MIL)保持整體基板厚度~~ 62 MIL。對平面耦合的緊密追蹤將減少跡線之間的串擾,并允許我們將阻抗保持在可接受的值。

良好的阻抗范圍(Zo)為50至60歐姆。請記住,較低的阻抗將增加dI/dt并顯著增加汲取的電流(對PDN不利),更高的阻抗會發出更多的EMI,并使設計更容易受到外界的影響干擾。

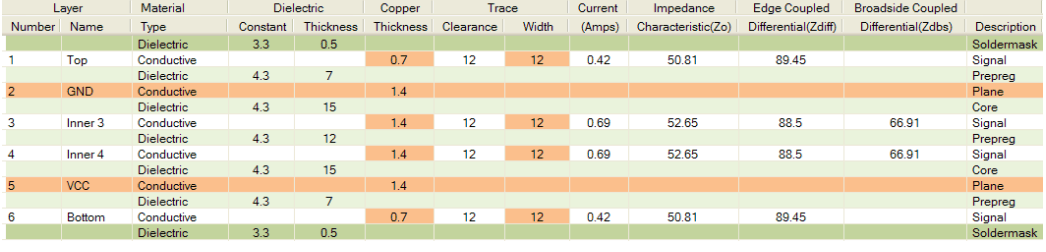

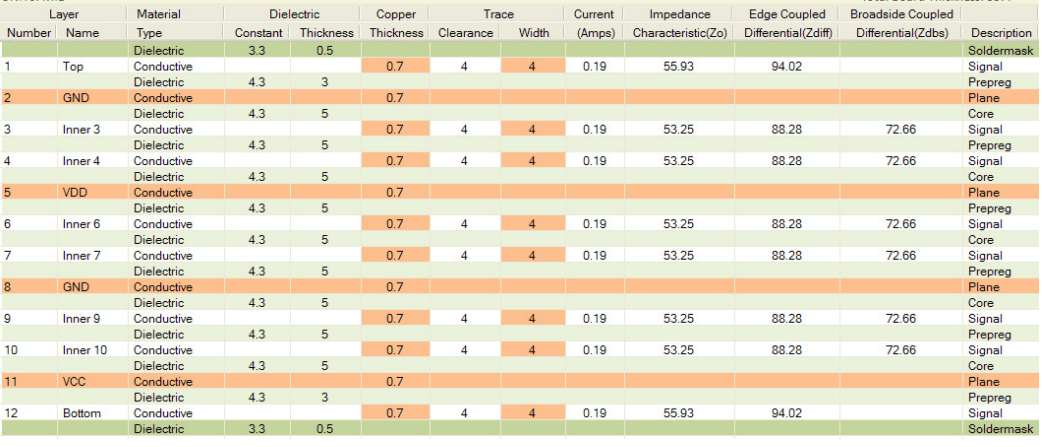

6層PCB疊層

六層板基本上是一個四層板,在平面之間添加了兩個額外的信號層。這極大地改善了EMI,因為它提供了兩個用于高速信號的埋層和兩個用于路由低速信號的表面層。

信號層應放置在非常靠近相鄰平面的位置,并且需要

板厚(62 MIL)由較厚的中心芯組成。在跡線阻抗,跡線寬度和預浸料/芯厚度之間始終存在折衷,并且最好使用Rayming建議來提供快速“假設”分析Rayming Stackup Planner計算特征阻抗加邊緣耦合和寬邊耦合差分阻抗。后者僅適用于嵌入式雙帶狀線層。差分對在高速設計中變得越來越普遍,通過使用差分模式信號來降低噪聲。

6層PCB疊層

8層PCB疊層

要提高EMC性能,請在六層疊層中再添加兩個平面。建議不要在平面之間有兩個以上的相鄰信號層,因為這會產生阻抗不連續性(信號層阻抗差為~20歐姆),并增加這些信號層之間的串擾。 p>

在下面的情況中,將兩個平面層添加到基板的中心。這允許中心平面之間的緊密耦合并隔離每個信號平面,從而減少耦合,從而顯著地增加串擾。這種配置通常用于DDR2和DDR3設計的高速信號,其中由于緊密布線引起的串擾是一個問題。

如果您有風險厭惡 - 那么這就是使用的疊加

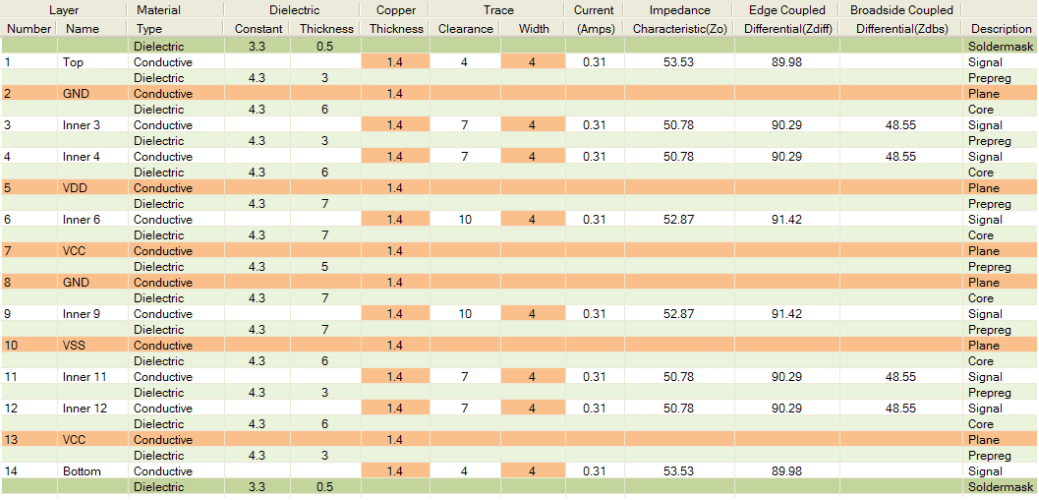

10層PCB疊層

當需要六個布線層和四個平面時,應使用十層板 - 并且EMC值得關注。

10層PCB疊層

上面演示了典型的10層圖層疊加。這種疊加是理想的,因為信號和返回平面的緊密耦合,高速信號層的屏蔽,多個接地層的存在,以及緊密耦合的電源/接地在董事會中心的飛機對。通常將高速信號路由在掩埋在平面之間的信號層上(在這種情況下為3-4層和7-8層)。但是,應該注意正確地對這些信號進行路由。

其他,避免相鄰層之間的耦合(串擾)。

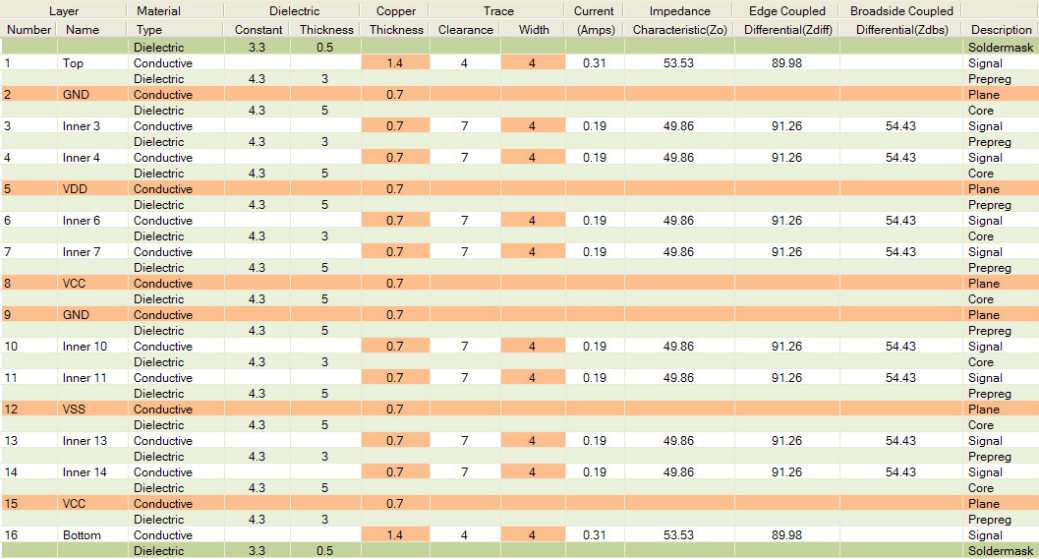

12層PCB疊層

12層是通常可以在62MIL厚板中方便地制造的最大層數。偶爾你會看到14到16層的電路板被制成62MIL厚的電路板,但制造它們的制造商的數量僅限于那些能生產HDI電路板的制造商。

高層計數板(十多個)需要薄電介質(在62MIL厚板上通常為5MIL或更小),因此它們之間會自動緊密耦合。

正確堆疊和布線后,它們可以滿足我們所有的高速要求和

將具有出色的EMC性能和信號完整性。上述十二層疊層

在六個內層上提供屏蔽。

12層PCB疊層

14層PCB疊層

當需要8個路由(信號)層時,使用下面的14層疊加

需要特殊的關鍵網盾。層6和9為敏感信號提供隔離,而層3和層3提供隔離。 4和11&amp; 12為高速信號提供屏蔽。

14層PCB疊層

16層PCB疊層

16層PCB提供十層布線,通常用于極其密集的設計。通常,您會看到16層PCB,其中EDA應用中使用的布線技術無法將設計路由到完成。 “如果它不會路由 - 只需繼續添加圖層”。雖然這是一種常見的說法,但這不是一種好的做法。

如果董事會不能完成路線,那么可能有很多原因。不良的安置往往是課程。打開布線通道,減少大鼠網中的交叉數量,在25 MIL網格上放置過孔以允許通過路由并盡可能地幫助路由器。

16層PCB堆疊

可以制造的層數實際上沒有限制在多層PCB中(請先檢查制造商的功能)。當然,隨著層數的增加,板厚度增加,以適應所用材料的最小厚度。還必須考慮縱橫比(板厚度與最小孔徑)。一般來說,厚度為100MIL的板材為10:1。例如,200 MIL厚的基板

的最小孔尺寸為20 MIL。

確定層數

技術規則基于在所使用的SMT元件的最小間距上,基本上是最大的走線,間隙和通孔允許,同時最小化PCB制造成本。采用球柵陣列(BGA)的復雜高速設計通常需要4/4 MIL(走線/間隙)和20/8 MIL(焊盤/孔)的過孔技術。但是,如果可以的話使用要求較低的尺寸,這將降低成本并提高制造產量。

一旦建立了這些規則,計算所需特征阻抗(Zo)和差分阻抗所需的疊加(Zdiff)根據組件數據表。通常,使用50歐姆Zo和100歐姆Zdiff。請記住,較低的阻抗會增加dI/dt并顯著增加吸收的電流(對PDN不利),較高的阻抗會產生更多的EMI,并使設計更容易受到外部影響干擾。因此,良好的Zo范圍為50-60歐姆。

給定設計所需的總層數取決于設計的復雜程度。因素包括:必須從BGA突破的信號網的數量; BGA所需的電源數量;組件密度和封裝類型。

經驗豐富的設計師在一段時間后會對它有所了解,但檢查是否有足夠多的層是一種很好的方法來自動調整電路板。如果沒有調整,路由器需要完成至少85%的路由,以指示所選的堆棧是可路由的。您可能需要多次重新評估放置以獲得最佳結果。

如何使用已建立的設計規則計算整個疊層的特性和差分阻抗?

對于那些不熟悉多層PCB疊層規劃的人,已經提供了常用的標準2到16層疊層。但是,您可以編輯,重命名和保存喜歡的自定義堆棧以便再次使用。

-

PCB設計

+關注

關注

394文章

4670瀏覽量

85292 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

42982

發布評論請先 登錄

相關推薦

如何設計多層PCB?

如何設計多層PCB?

評論