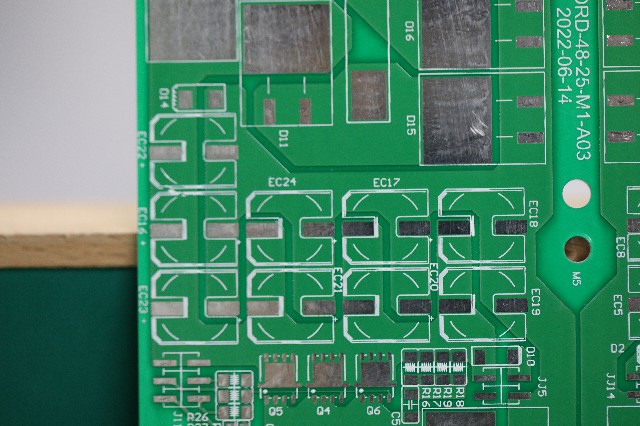

電路板設(shè)計(jì)是一項(xiàng)非常耗時(shí)且耗時(shí)的任務(wù),任何問題都需要工程師在逐個(gè)組件的基礎(chǔ)上檢查整個(gè)設(shè)計(jì)。可以說電路板的設(shè)計(jì)要求與芯片設(shè)計(jì)一樣好。

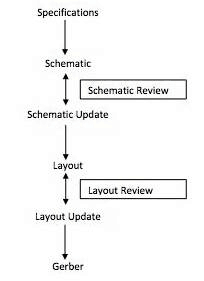

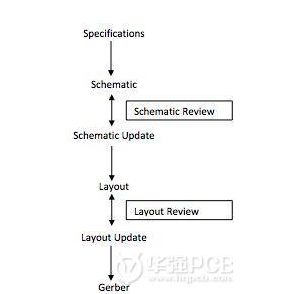

典型的電路板設(shè)計(jì)流程包括以下步驟:

前三個(gè)步驟占用的時(shí)間最多,因?yàn)樵韴D檢查是一個(gè)手動(dòng)過程。想象一下?lián)碛?000個(gè)或更多連接的SoC板。手動(dòng)檢查每個(gè)連接是一項(xiàng)繁瑣的工作。實(shí)際上,幾乎不可能檢查每個(gè)連接,這可能導(dǎo)致最終板中出現(xiàn)問題,例如錯(cuò)誤連接,浮動(dòng)節(jié)點(diǎn)等。

原理圖捕獲階段通常面臨以下類型的問題:

下劃線錯(cuò)誤:例如APLLVDD和APLL_VDD

案例問題:例如VDDE和vdde

拼寫錯(cuò)誤

信號(hào)短路問題

還有更多......

為了避免這些錯(cuò)誤,應(yīng)該有一種方法可以在幾秒鐘內(nèi)檢查完整的原理圖。該方法可以通過原理圖仿真實(shí)現(xiàn),這在當(dāng)前的電路板設(shè)計(jì)流程中很少見。原理圖模擬允許您在所需節(jié)點(diǎn)上查看最終輸出,因此它會(huì)自動(dòng)檢查所有連接問題。

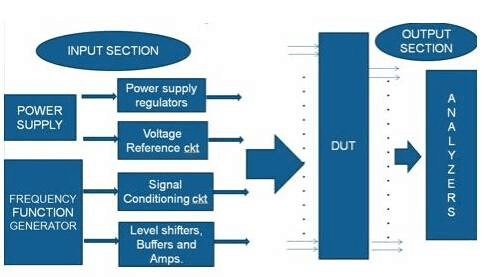

以下內(nèi)容由項(xiàng)目示例解釋。考慮一個(gè)典型的電路板框圖:

在復(fù)雜的電路板設(shè)計(jì)中,數(shù)字連接可以達(dá)到數(shù)千個(gè),很少有變化可能會(huì)浪費(fèi)大量時(shí)間進(jìn)行檢查。

原理圖仿真不僅可以節(jié)省設(shè)計(jì)時(shí)間,還可以提高電路板質(zhì)量并提高整體工藝效率。

典型的待測設(shè)備(DUT)具有以下信號(hào):

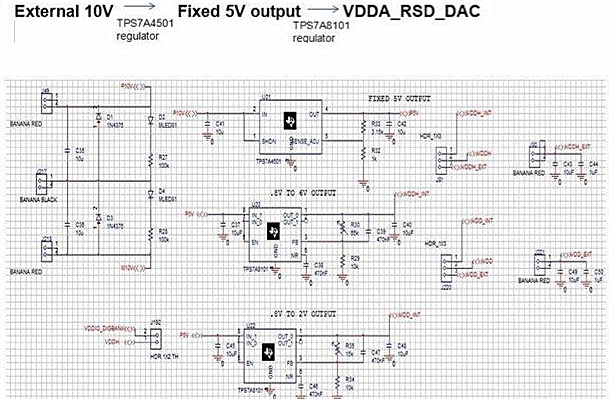

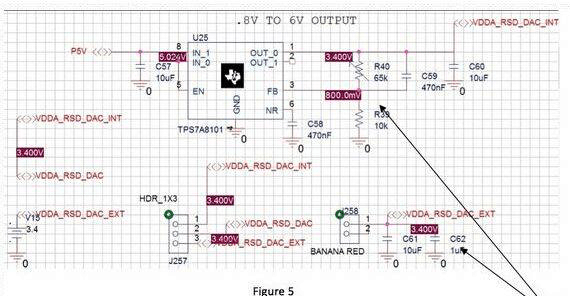

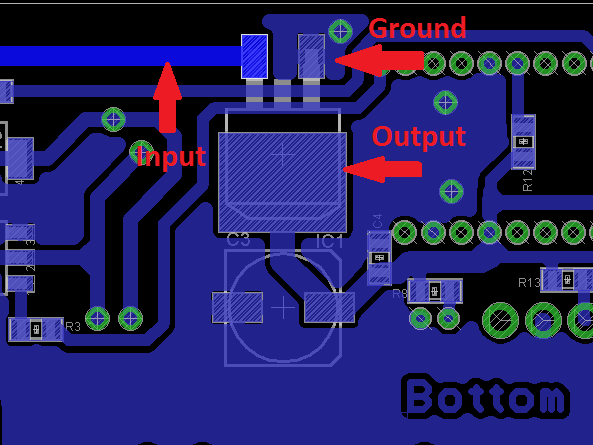

經(jīng)過一些預(yù)調(diào)整后,被測設(shè)備會(huì)有各種信號(hào)并且存在用于信號(hào)調(diào)整的各種模塊,例如電壓調(diào)節(jié)器,運(yùn)算放大器等。考慮一個(gè)由電壓調(diào)節(jié)器獲得的電源信號(hào)的示例:

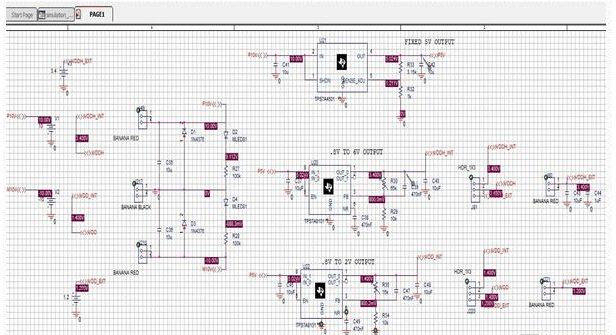

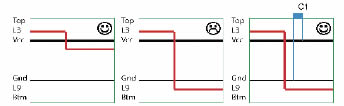

按順序?yàn)榱蓑?yàn)證連接并執(zhí)行整體檢查,使用了原理圖模擬。原理圖仿真包括原理圖創(chuàng)建,測試平臺(tái)創(chuàng)建和仿真。

在測試平臺(tái)創(chuàng)建過程中,激勵(lì)信號(hào)被發(fā)送到必要的輸入,然后輸出是在感興趣的信號(hào)點(diǎn)觀察到。

上述過程可以通過將探針連接到要觀察的節(jié)點(diǎn)來實(shí)現(xiàn)。節(jié)點(diǎn)電壓和波形可以指示原理圖中是否存在錯(cuò)誤。所有信號(hào)連接都會(huì)自動(dòng)檢查。

讓我們來看一下在上面的圖片中,檢測到的節(jié)點(diǎn)和電壓清晰可見:

所以在幫助下在模擬中,我們可以直接觀察結(jié)果并確認(rèn)PCB板的原理圖是正確的。此外,可以通過仔細(xì)調(diào)整刺激信號(hào)或元件值來進(jìn)行設(shè)計(jì)變更的調(diào)查。因此,原理圖仿真可以節(jié)省電路板設(shè)計(jì)和檢查人員的大量時(shí)間,并增加設(shè)計(jì)正確性的可能性。

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4670瀏覽量

85290 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

42982

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

盤點(diǎn)PCB設(shè)計(jì)中的常見錯(cuò)誤

請(qǐng)問如何提高PCB設(shè)計(jì)布通率以及設(shè)計(jì)效率?

軟件仿真提高PCB設(shè)計(jì)效率

PCB設(shè)計(jì)布通率及設(shè)計(jì)效率技巧

(多圖) PCB設(shè)計(jì):如何減少錯(cuò)誤并提高效率

如何減少PCB設(shè)計(jì)的錯(cuò)誤并提高效率

PCB設(shè)計(jì)過程和提高布線效率的步驟

PCB設(shè)計(jì):如何減少錯(cuò)誤并提高效率?

13種最常見的PCB設(shè)計(jì)錯(cuò)誤,我們?cè)撊绾伪苊膺@些錯(cuò)誤

3種常見的PCB設(shè)計(jì)錯(cuò)誤

PCB設(shè)計(jì)工作中常見的錯(cuò)誤有哪些?

常見的PCB設(shè)計(jì)錯(cuò)誤匯總

PCB設(shè)計(jì)工作中常見的錯(cuò)誤有哪些?

如何減少PCB設(shè)計(jì)錯(cuò)誤提高自己的設(shè)計(jì)效率

如何減少PCB設(shè)計(jì)錯(cuò)誤提高自己的設(shè)計(jì)效率

評(píng)論