背景

STM32G071的PD0,PD2作為外部中斷使用,外部接10K上拉電阻拉到3.3V。外部設備被觸發后電平變為低電平,平常保持高電平信號。

問題

在以上背景下,按道理外部設備正常時(未觸發中斷),IO口輸入電平應該是3.3V。但是實際上測量到的卻是0.9V,這跟觸發后的0V,同樣會被單片機識別為低電平,故無法產生電平跳變而觸發中斷。

分析解決

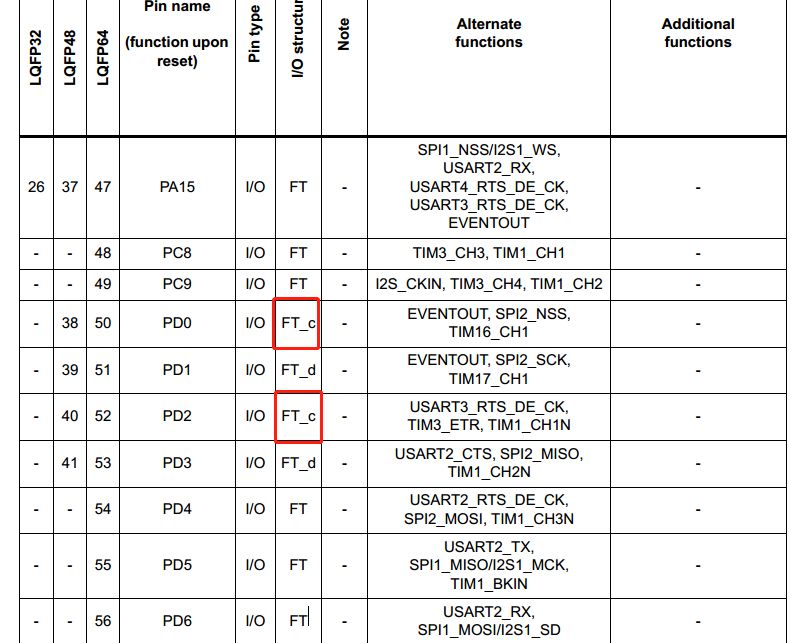

查閱STM32G0數據手冊可知:

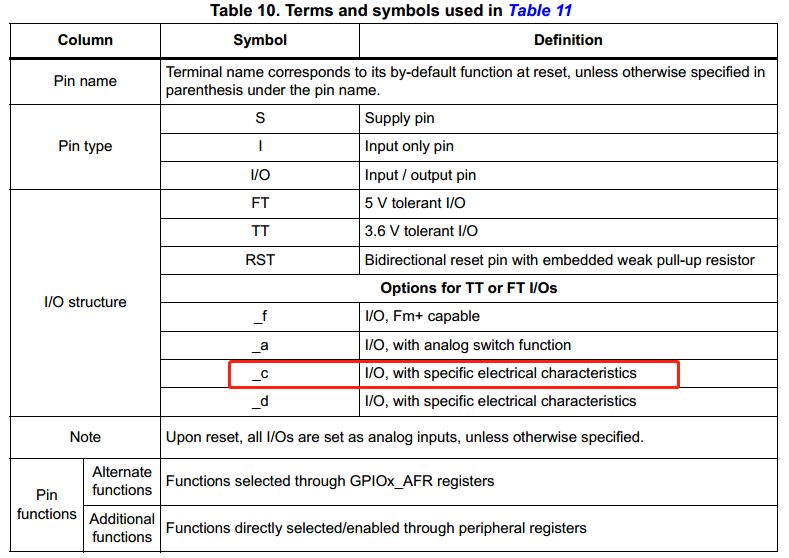

這個引腳的電平類型為FT_c,我們知道FT是容忍5V的意思,那么FT_c是什么意思?不妨看看說明:

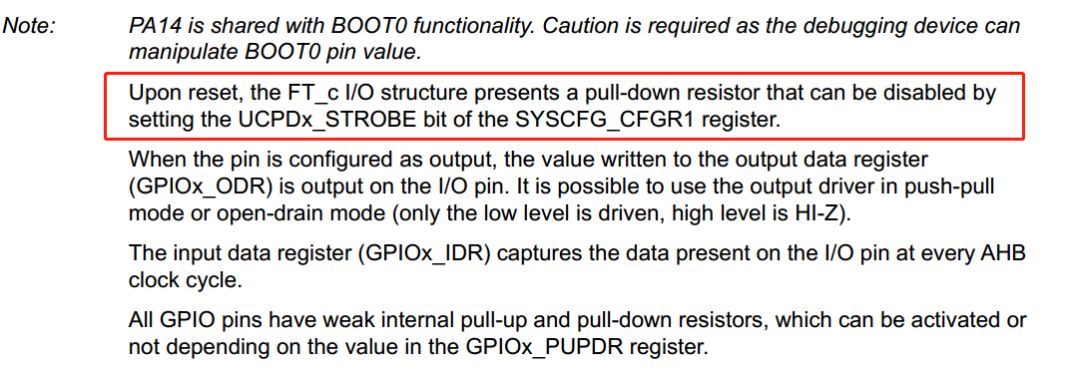

然后去用戶手冊查看GPIO相關說明,找到以下內容:

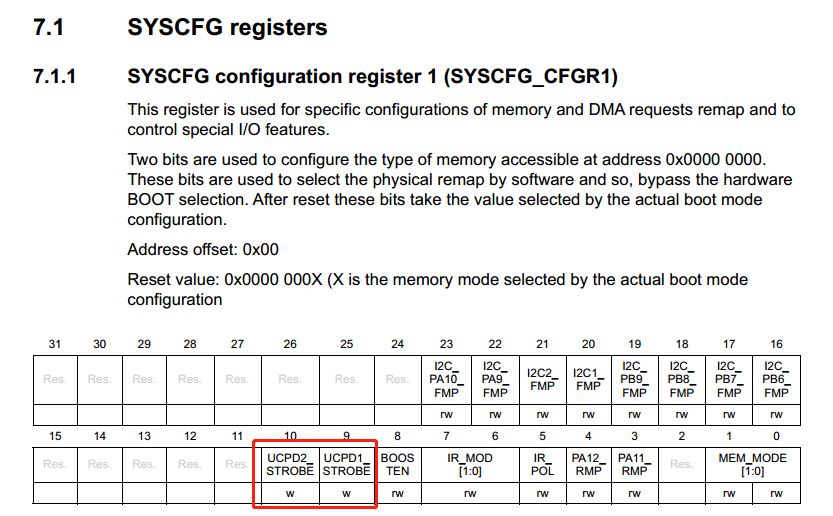

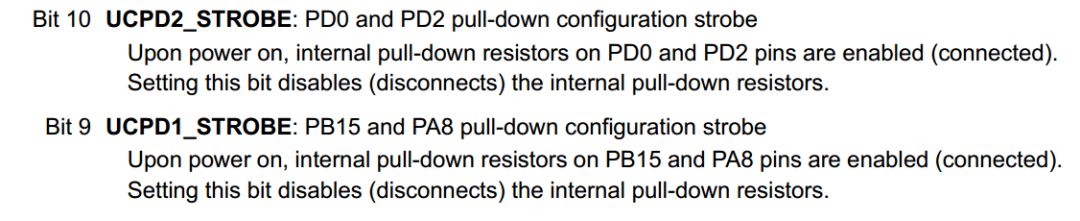

基本上了解狀況了,再看一下相關寄存器說明:

具體說明:

看了以上說明,基本明白怎么操作了。在初始化IO的時候,應該把SYSCFG registers的UCPD2_STROBE位設置一下就ok了。

HAL庫操作:HAL_SYSCFG_StrobeDBattpinsConfig(SYSCFG_CFGR1_UCPD2_STROBE);

LL庫操作:MODIFY_REG(SYSCFG->CFGR1, (SYSCFG_CFGR1_UCPD1_STROBE | SYSCFG_CFGR1_UCPD2_STROBE), SYSCFG_CFGR1_UCPD2_STROBE);

再提醒下,其實PA8和PA15也是這樣的。如果我們不需要這個下拉電阻,需要按照上面的操作調整一下。

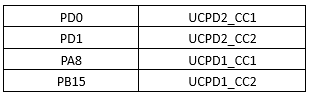

那么為什么STM32G071有這樣的設置呢?看下面IO功能即可知道,這幾個引腳其實是下面幾個管腳的復用腳。

-

STM32

+關注

關注

2266文章

10876瀏覽量

354929

原文標題:技術分享 | STM32G071 PD0 PD2引腳使用注意事項

文章出處:【微信號:STM32_STM8_MCU,微信公眾號:STM32單片機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

STM32G071或G070在未燒寫程序時,MCU上電其PB7腳輸出的是個高電平,為什么?

請問如何設置stm32f051的PD0、PD1為GPio口

請問PD2引腳沒用到戰艦開發板以太網歷程中去嗎?

嵌入式系統的核心器件:STM32G071開發事項

將CAN引腳重映射到了PD0和PD1引腳上

STM32G070的4個引腳相關資料推薦

求一種引腳PD2鎖存問題的解決方案

CH32F203的PD0,PD1作為GPIO不受控是什么原因?

CHV203C8T6的OSC_IN和OSC_OUT重映射為PD0/PD1使用程序會停止運行如何解決?

使用帶有stm32g071rb76處理器的usb-pd系統,為什么只有一個CC引腳?

STM32F103C8引腳PD0和PD1不能作為輸出要怎么解決?

如何連接STM32G071進行USB Type-C PD充電?

STM32G071KBT6“GP版”與“PD版”的區別是什么?

PD0內部上拉與PD1內部上拉一起工作,讀取的數值與實際不符是為什么?

STM32G071 PD0 PD2引腳使用注意事項

一文知道STM32G071 PD0 PD2引腳使用注意事項

一文知道STM32G071 PD0 PD2引腳使用注意事項

評論