?

隨著SoC技術應運而生的是SOPC技術。它結合了SoC和FPGA的優點,可裁減、可擴充、可升級,并具備軟硬件在系統中可編程的功能。SOPC能夠提供更好的性能以及更低的功耗,有效節省電路板空間并降低產品的總成本,電子工業正逐漸向SOPC設計轉移,使SOPC成為現代電子系統的最佳選擇之一。在充分研究EPA網絡通信和SOPC技術的基礎上,開發了一種基于SOPC技術的EPA控制器。

SOPC技術

SOPC技術是美國Altera公司于2000年最早提出的,并同時推出了相應的開發軟件Quartus II。SOPC是基于FPGA解決方案的SoC,與ASIC的SoC解決方案相比,SOPC系統及其開發技術具有更多的特色,并具備以下的基本特征:至少包含一個以上的嵌入式處理器IP核;具有小容量片內高速RAM資源;豐富的IP核資源可供靈活選擇;有足夠的片上可編程邏輯資源;處理器調試接口和FPGA編程接口共用或并存;可包含部分可編程模擬電路;單芯片、低功耗。

SOPC是一種新的系統設計技術,也是一種新的軟硬件綜合設計技術。通過它,可以很快地將硬件系統(包括微處理器,存儲器,外設以及用戶邏輯電路等)和軟件設計都放在一個可編程的FPGA芯片中,以達到系統的IC設計。這種設計方式,具有開發周期短以及系統可修改等優點。設計完成的SOPC可以通過HARDCOPY轉為ASIC芯片,從而可以實現快速量產。

EPA現場控制器設計

針對控制系統中連接管理網、控制網和現場設備單元的要求,采用SOPC技術、現場總線技術和自動控制技術,設計一種適用于EPA工業以太網的控制器,并在其可編輯軟核的CPU處理器上實現了實時操作系統及EPA通信協議棧。該EPA現場控制器可實現實時控制信息的輸入輸出,并對以太網上的其他的EPA設備進行監控、顯示和故障報警。本文將針對該EPA控制器的基于SOPC技術的CPU核心處理模塊和通信處理模塊分別進行說明。

EPA現場控制器的硬件設計總體方案

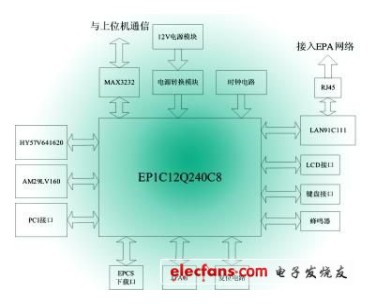

圖1是EPA現場控制器的硬件系統結構框圖。整個設計中,硬件上實現EP1C12Q240C8芯片、LAN91C111芯片的外圍接口電路的設計;實現了串口通信和網絡通信的設計;實現了復位電路、JTAG、時鐘電路、電源電路的設計;實現了鍵盤電路、LCD顯示電路、蜂鳴器報警電路的設計;實現了HY57V641620芯片、AM29LV160芯片外圍電路的設計,拓展了豐富的存儲器資源,可移植linux、windows CE操作系統等;拓展了總線接口,可以根據工業現場的實際需要接入相應的板卡(如DI/DO模塊、AI/AO模塊,實現與現場數據之間的數模、模數轉換、拓展MMC存儲卡,拓展其存儲容量等)。

?

圖1基于FPGA的EPA控制器的硬件結構框圖

在設計時,考慮到由于該控制器的結構、功能較為復雜,涉及到的器件種類較多。所以在設計時,將硬件板卡分為兩部分來做。第一部分:CPU核心處理模塊,包含CPU處理器EP1C12Q240C8、存儲器(FLASH、SDRAM)、電源部分、時鐘源、JTAG、EPCS下載口和復位電路。第二部分:通信處理模塊,包含網絡通信(LAN91C111網卡芯片和RJ45)、串口通信(MAX3232)、LCD接口、鍵盤接口和蜂鳴器。

基于SOPC技術的CPU核心處理模塊

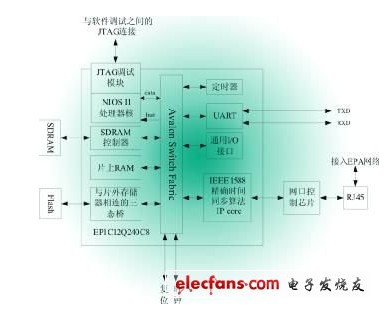

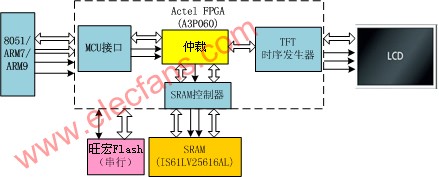

整個方案的實現是以接入實時工業以太網絡為目的,在芯片內部實現部分EPA協議,同時控制器實現對工業以太網上的其他設備的監控、顯示及數據分析。設計中采用Altera公司的新一代低成本的FPGA芯片EP1C12Q240C8芯片,該芯片包含有12060LE(邏輯單元),可根據實際需要,配置其NIOSⅡCPU軟核、與CPU相連的片內外設和存儲器以及與片外存儲器和片外設備相連的接口等。其芯片系統結構框圖如圖2所示。

?

圖2 芯片系統結構框圖

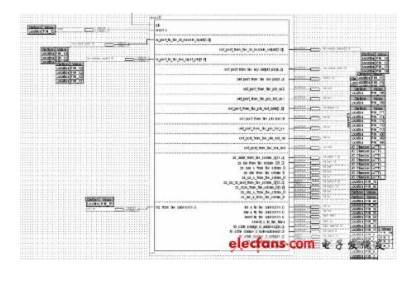

整個CPU處理器的硬軟件設計均在Quartus II 5.1版本上實現。NIOSⅡ處理器核是Altera公司的第二代用戶可配置的通用32位RISC軟核微處理器,是Altera公司特有的基于FPGA架構的可配置的軟CPU內核,其特性和外設可根據實際需要進行增加或剪裁。所有NIOSⅡ處理器系統使用統一的指令和編程模型,并有三種類型以滿足不同設計的要求,分別是快速型、經濟型和標準型。在本控制器中,所定制的NIOSⅡ軟核選用快速型,該內核處理速度為49DMIPS,耗費的邏輯門數為1400~1800LE,同時帶有硬件乘法器和硬件除法器。根據EPA網絡對控制器的要求,添加與CPU相連的片內外設和片外設備接口:SDRAM控制器、片內RAM、三態橋、UART、定時器、通用I/O口、LCD顯示驅動電路和以太網接口。按照設計要求,在Quartus II 5.1版本下的對CPU的配置情況如圖3所示。FPGA芯片可根據實際需要靈活地增加功能,同樣對不必要的功能也可進行刪減,以滿足快速、高效和低成本的設計。

?

圖3 EP1C12Q240C8芯片配置情況

在配置完CPU處理器的內部結構以后,按照設計需要對CPU的外圍進行配置。由于該控制器是接入EPA網絡,需要實現EPA協議,而FPGA芯片EP1C12Q240C8的內部只有288K的RAM,所以在片外擴展了16M bits的FLASH-AM29LV160D和64M bits的SDRAM-HY57V641620的。從外部引入12V的直流電源,經過電平轉換以后得到3.3V和1.5V的電源,為CPU、存儲器及其他受電設備供電。CPU上的時鐘源使用的是50MHz的鐘振。JTAG和EPCS下載口用于硬軟件的下載。將在Quartus Ⅱ上編輯的硬件程序和軟件程序通過JTAG和EPCS下載口,下載到FLASH和RAM(片內或者片外)中,可進行在線調試。該復位電路是由10KW電阻、10mF電容和按鍵組成,可實現按鍵低電平復位和上電低電平復位。

通信處理模塊

整個設計以FPGA芯片EP1C12Q240C8為數據處理中心,通過網絡通信,完成對工業以太網上的其他設備的數據通信,同時通過MAX3232實現和上位機的串口通信。在該模塊中,加入了LCD接口、行列式鍵盤接口和蜂鳴器接口,對工業以太網上的其他EPA設備進行監控和顯示,有較好的人機交互的功能。

在該設計中,網絡通信分為有線和無線兩種通信方式。其中,有線網絡通信使用的是10M/100M的LAN91C111的自適應網卡芯片,并通過RJ45網口接入EPA網絡。LAN91C111是SMSC公司為嵌入式應用系統推出的第三代快速以太網控制器。LAN91C111的芯片上集成了遵循SMSC/CD協議的MAC(媒體層)和PHY(物理層),符合IEEE802.3/802.U-100Base-Tx/10Base-T規范。在本控制器上預留了藍牙模塊和ZigBee模塊的無線通信接口,作為輔助處理模塊。可根據工業現場的實際情況,接入無線通信模塊,實現與EPA網絡的無線通信,通過該模塊能夠監測無線現場設備的運行情況及相關參數。

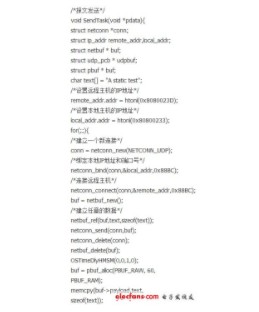

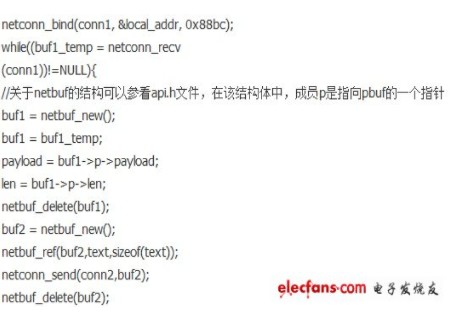

在整個EPA通信協議棧網絡層和傳輸層接收報文處理流程中。NIOSⅡ處理器復位后初始化UC/OS Ⅱ操作系統、網絡接口、堆棧以及定時器等外圍設備接口。從外部存儲器FLASH中獲取IP地址和MAC地址等網絡信息。當收到的報文IP地址和MAC地址都是本機地址時,把報文以LWIP所要求的特殊結構體形式存儲在接收緩沖區中,然后發送到EPA協議棧中進行處理,當檢查到UDP端口號是0x88BC時,將報文交由EPA應用層處理模塊進行處理。

?

圖4 EPA協議棧接收報文處理流程圖

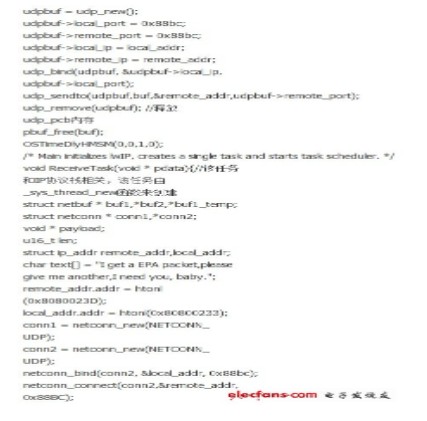

其部分報文處理程序如下:

?

?

?

結語

在完成整個設計,控制器接入EPA網絡中能夠正常運行。由于控制器中的處理器使用的是FPGA芯片,有較強的靈活性,能夠進行編程、除錯、再編程和重復操作,因而可以充分地進行設計開發和驗證。當電路有少量改動時候,更凸現出其優勢,其現場編程能力可以延長產品在市場上的壽命,可以用來系統升級,從而大大提高了控制器的性能。

電子發燒友App

電子發燒友App

評論