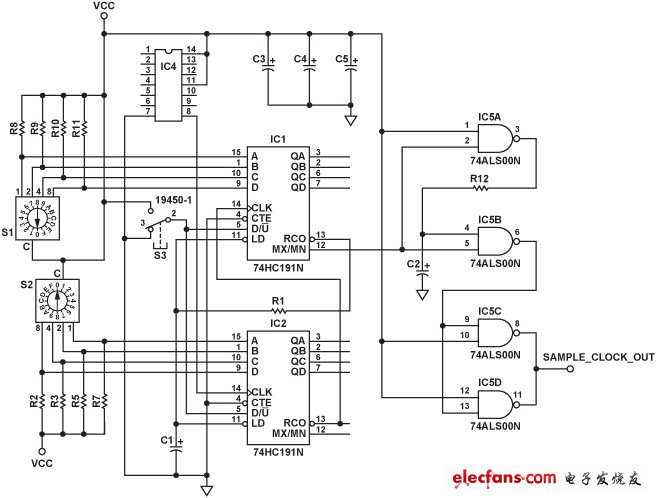

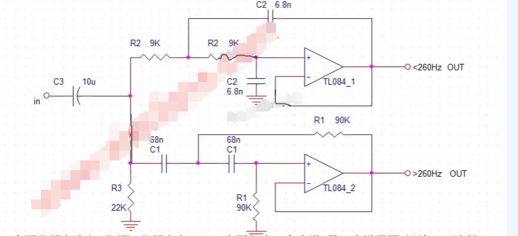

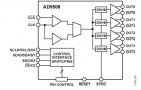

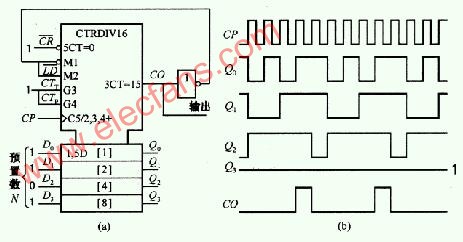

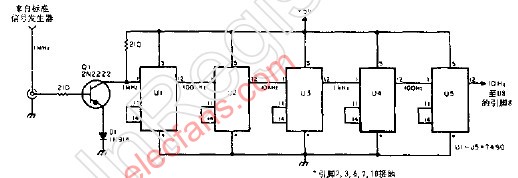

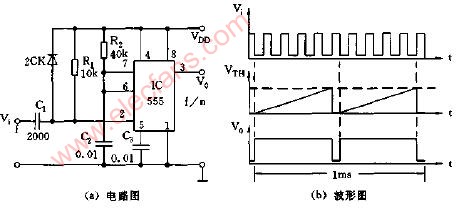

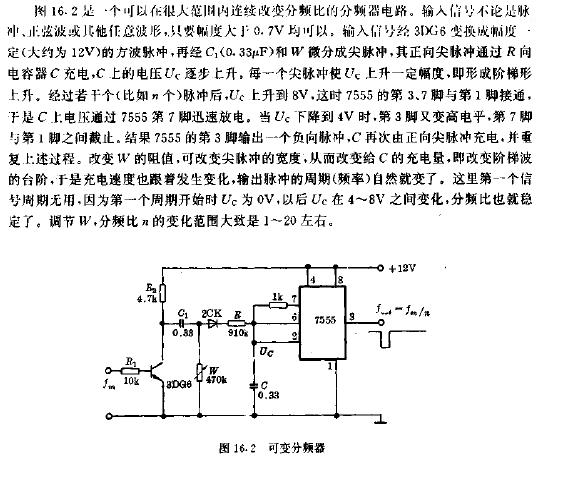

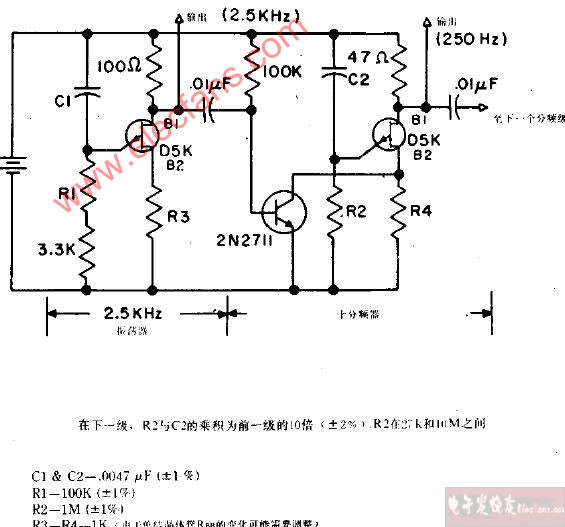

AD783要求一個寬度為150 ns至250 ns的窄正采樣脈沖。為使顯示的波形保持穩定,無來回跳動,采樣脈沖必須非常穩定,抖動很低。這一要求往往將可能的時鐘選擇限定于晶體振蕩器。另一個要求是采樣速率可以在略低于100 kHz到大約500 kHz的范圍內進行調整或調諧。為使下采樣信號落在聲卡的20 Hz到20 kHz音頻帶寬內,采樣頻率間的調諧步進必須較為精細。一個諸如圖所示的N分頻電路和一個頻率介于10 MHz到20 MHz的晶體振蕩器(IC4),可以提供從80 kHz到350 kHz的多達200種或更多的不同采樣速率,步進大小介于300 Hz到5 kHz之間。本例使用兩個4位二進制升降計數器74HC191,N可以是4到256之間的任意整數。也可以使用74HC190等十進制計數器,其引腳排列與74HC191相同,可以提供4到100的N值。分頻比利用兩個十六進制開關S1和S2設置。開關S3設置計數器是遞增還是遞減計數。電阻R1 (250 Ω)和電容C1 (68 pF)給引腳計數輸出增加一個很短的延遲,經過該延遲后,引腳計數輸出加載起始計數值。74HC00的四個NAND門用于實現單穩態模式,當R12為2.7 kΩ且C2為68 pF時,單穩態模式提供200 ns的采樣脈沖。

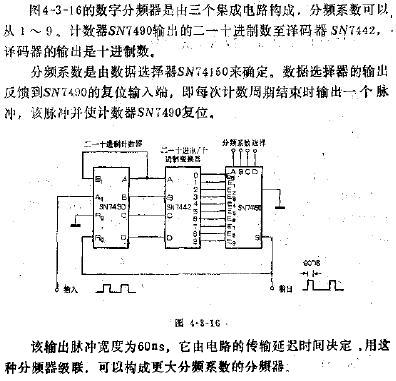

圖. 采樣時鐘分頻器電路

電子發燒友App

電子發燒友App

評論