在使用CH340芯片進行電路設計時,我們應該注意哪些細節與事項呢?接下來我們一起來看看。

電壓匹配問題

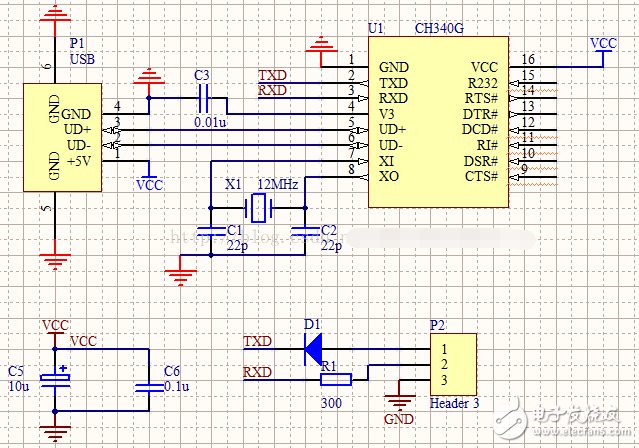

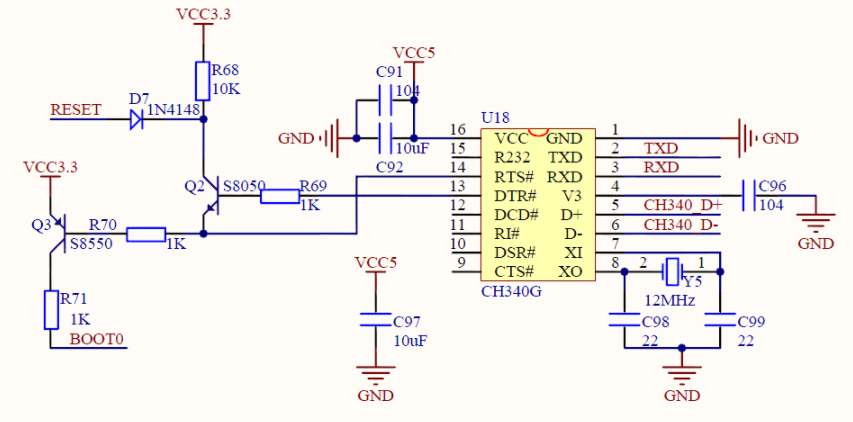

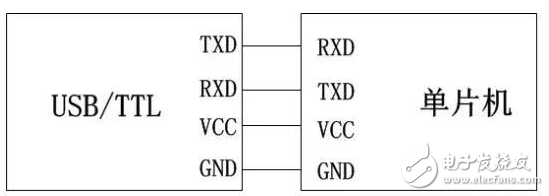

CH340芯片通過USB轉換出來的TTL串口輸出和輸入電壓是根據芯片供電電壓是自適應的。也即,如果芯片是5V供電,那么串口輸出和采樣都是5V;如果是3.3V供電,那么標準就成了3.3V,因此在實際使用的時候,串口連接到的對端設備需要注意電壓匹配的問題。其中在5V供電模式下,是可以與3.3V系統兼容的,反過來則不可以,如果CH340是3.3V供電,那么不可以接5V系統,會損壞芯片。另外如果對端是1.8V系統,那么是不能與CH340的3.3V模式兼容的,此時輸出和采樣會出錯。最好加一些器件來升降壓來進行電壓匹配。因此設計時確認好對端串口電平范圍,然后決定CH340工作在3.3V或者5V工作模式。在電路設計原理上,5V供電時芯片V3引腳需要接一個104電容到地,3.3V供電時直接將V3腳與3.3V電源引腳短接就可以了。

防止電流倒灌問題

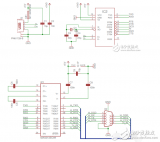

在實際應用中,當CH340與其他IC譬如MCU等器件一同使用時,如果串口直連的雙方器件有一方不需要供電工作時,要注意電流倒灌導致未供電的芯片繼續工作的情況,或者是在串口下載場景中,當MCU需要復位以實現下載時,發現復位不成功,可能也是由于該原因造成的。因此,在電路設計中可以做如下改動來防止CH340與對端IC出現任何一方被倒灌電的情況。原理圖如下:

也就是在CH340芯片的發送引腳TXD上接一個反向二極管,然后再連接到對端IC。在接收引腳上加一個限流電阻來防止對端IC對CH340倒灌電。

通過反向二極管的原理是:在CH340發送數據時,發送高電平時二極管截止,但是由于對端RXD默認上拉也是高電平不會有采樣問題,而發送低電平時二極管導通,對端RXD接收到低電平,因此可以正常通訊。并防止了CH340的TXD發送引腳將電流倒灌到對端IC。

通過限流電阻的原理是:倒灌電流導致芯片工作甚至閂鎖效應,是由于引腳電流過大超過了芯片設計時容忍的上限導致芯片內部電路出現異常。因此加一個限流電阻就可以了,其他通訊場景也可以仿照此方法進行嘗試。

晶體以及電容的選用

對于CH340系列需要外部晶振的芯片,在選用晶振時如果選擇12MHz的石英晶體,那么旁路電容選擇22pF的獨石或高頻瓷片電容。如果選用的低成本陶瓷晶體,那么旁路電路的容量必須用該晶體廠家的推薦值,一般情況下是47pF。對起振困難的晶體,建議電容數值減半。如果仍然無法起振,最好參考一下選用晶振的官方推薦電容值。

芯片CH340的V3引腳作用

V3的引腳除了在不同電壓供電模式下接法不同,對于電容數值選用也是需要注意的。V3引腳的電容用于內部電源節點退耦,來改善USB傳輸過程中的EMI,通常容量在4700pF到0.1uF范圍,建議容量為0.01uF,即103電容。

提高工作穩定性和抗干擾

因為USB信號屬于模擬信號,所以在CH340等USB芯片內部包含數字電路和一些模擬電路,另外,USB芯片中還包含時鐘震蕩及PLL倍頻電路,電路的公共地端在芯片內部已經連接在一起并連接到芯片的GND引腳。

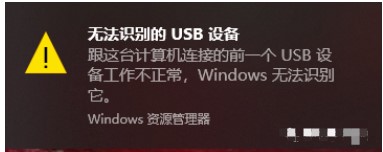

如果USB芯片有時工作不正常、或者USB數據傳輸隨機性失敗、或者抗干擾能力差,那么就應該考慮USB芯片是否穩定工作。影響USB芯片工作穩定性的幾大因素有:

時鐘信號不穩定-這是主要原因,下面將詳細分析。

時鐘信號受干擾-解決方法:PCB設計時盡量不再晶體及震蕩電容附近走線,尤其是不要走繼電器、電動機等帶有瞬時沖擊電流的電源線和強信號線;在晶體及震蕩電容周邊布置GND鋪銅屏蔽干擾;將晶體外殼接地(任何需要晶體工作的電流都可以這樣設計);或者使用有源晶振等。

USB信號受干擾-解決辦法:PCB設計時使USB信號線D+與D-平行布線,最好在兩側布置GND鋪銅,減少干擾。使用符合USB規范的帶屏蔽層的傳輸線,不能使用普通排線或者非USB線纜。

電子發燒友App

電子發燒友App

評論