本文為大家?guī)砦宸N不同的12進制計數(shù)器設(shè)計方案。

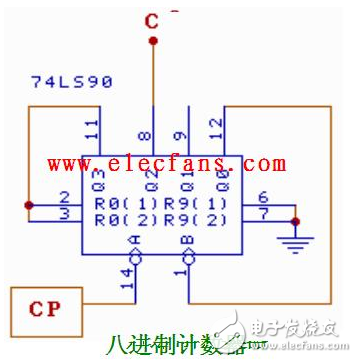

12進制計數(shù)器設(shè)計方案一:用74161設(shè)計十二進制計數(shù)器

1.74161為十六進制計數(shù)器,設(shè)計十二進制計數(shù)器時1片就可以滿足要求。

2.新建BDF文件及保存工程同前篇。

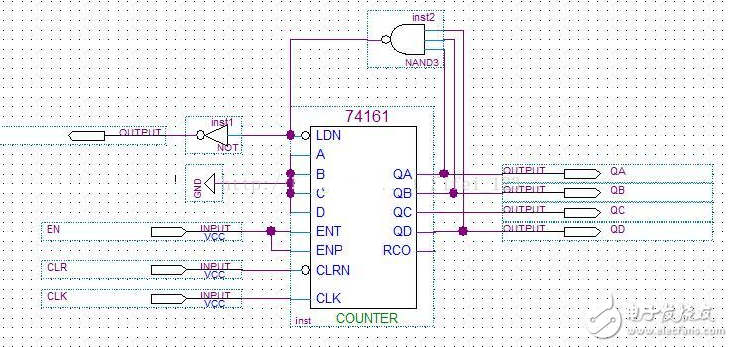

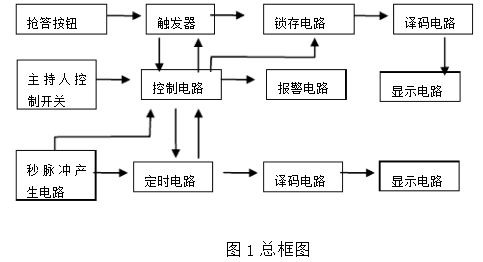

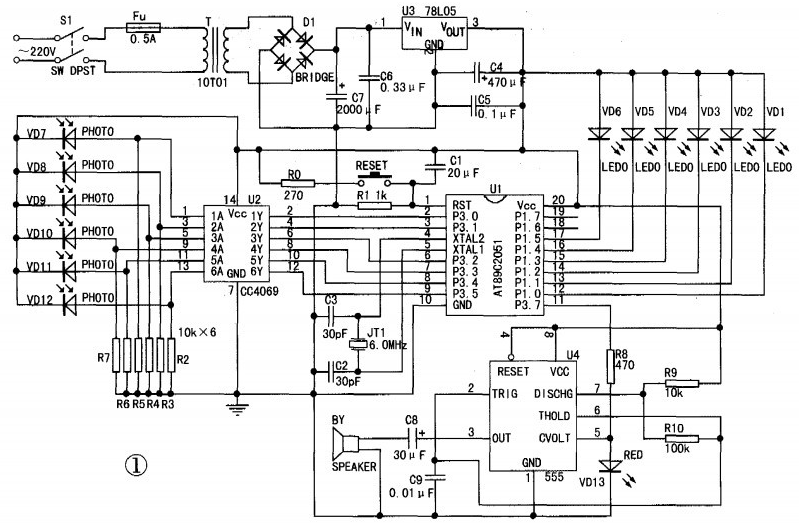

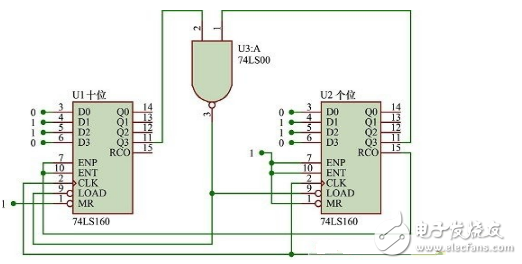

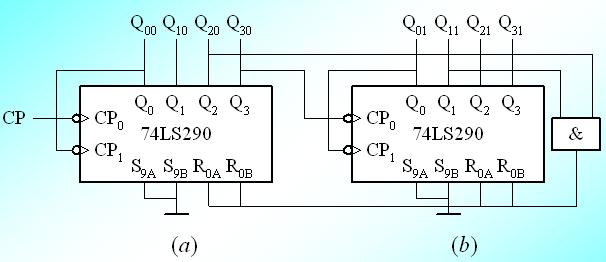

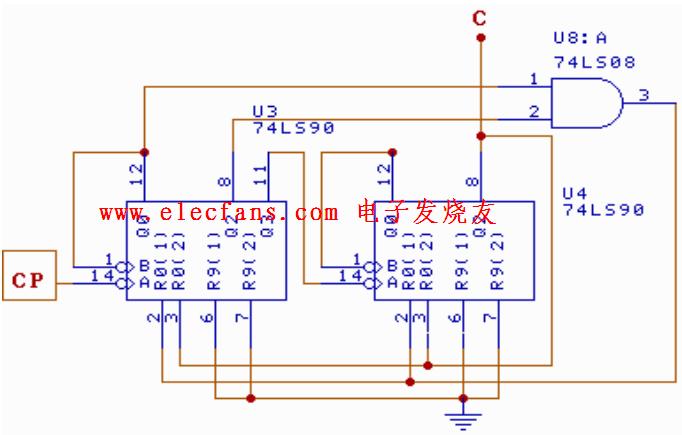

3.將所需要的元器件和引腳拖入?yún)^(qū)域內(nèi)并完成連接,如圖1所示

圖1 十二進制計數(shù)器連接圖

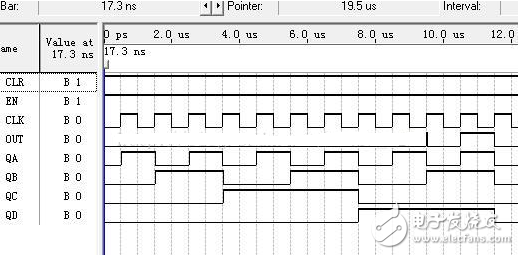

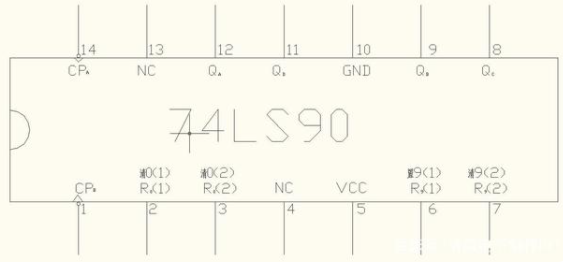

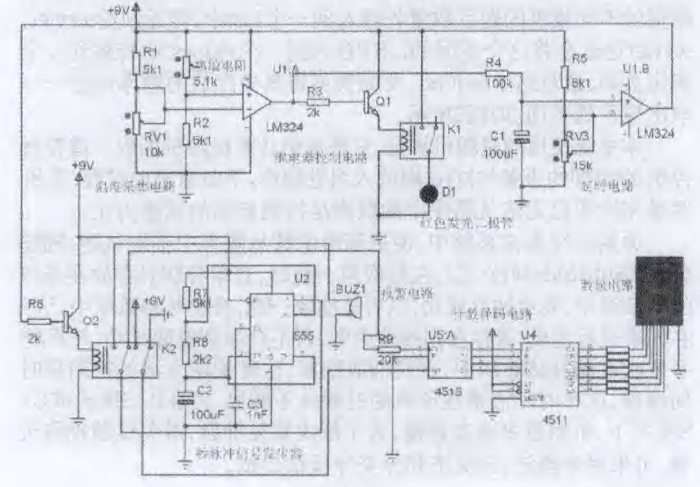

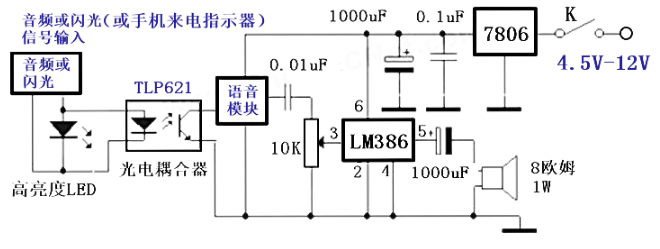

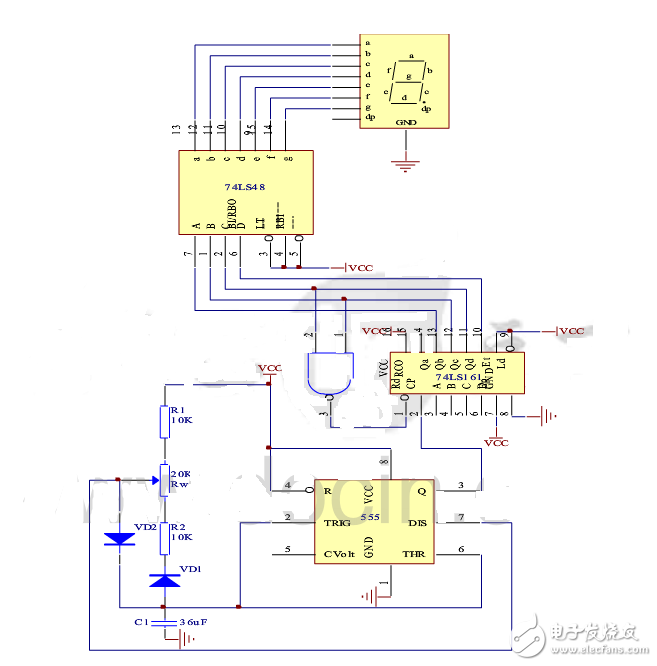

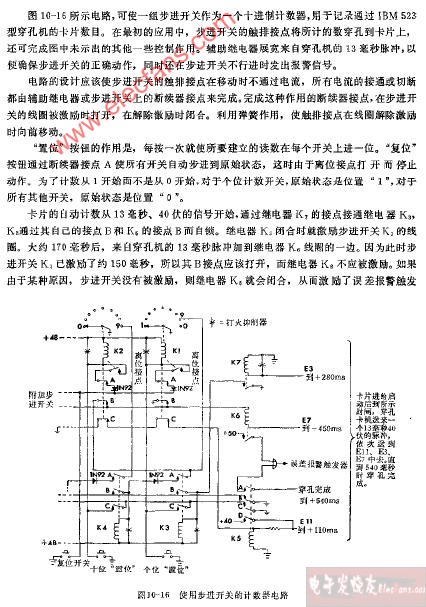

4.建立VWF文件,仿真后得到結(jié)果如圖2

仿真波形圖

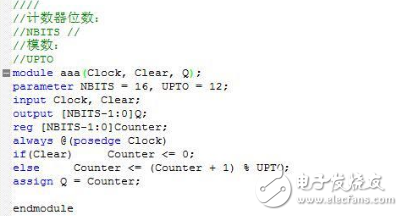

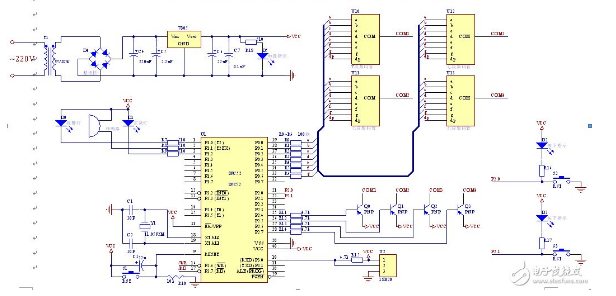

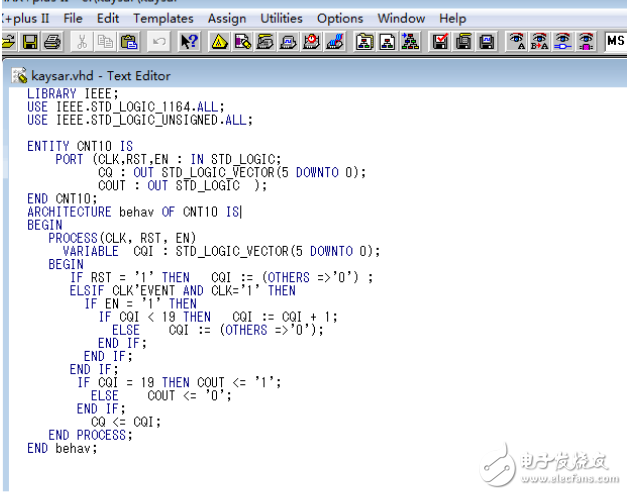

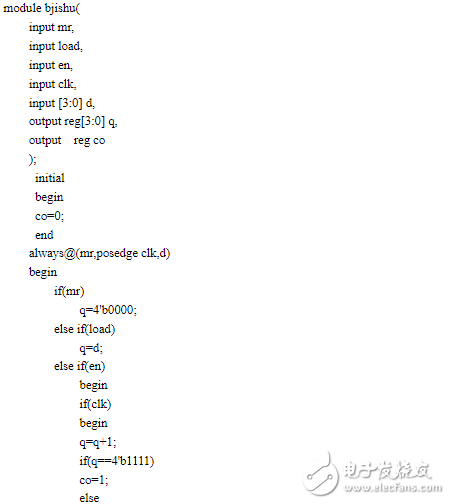

12進制計數(shù)器設(shè)計方案二:用verilog語言實現(xiàn)十二進制計數(shù)器

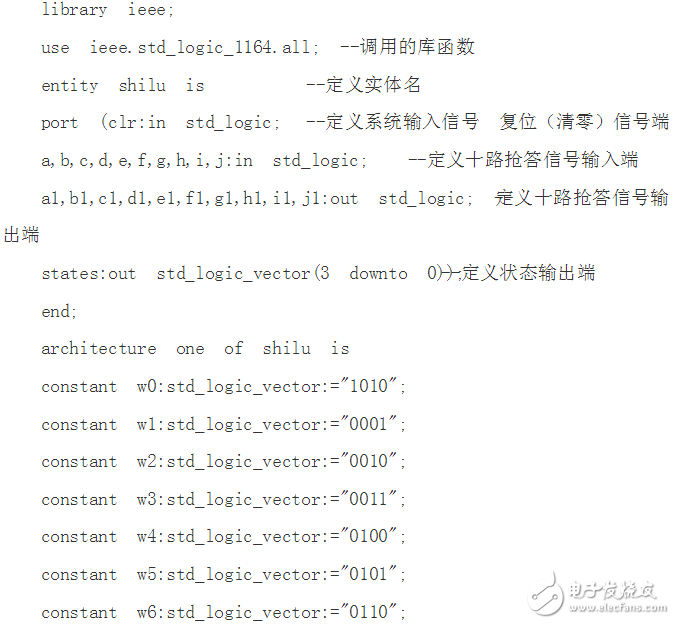

程序代碼

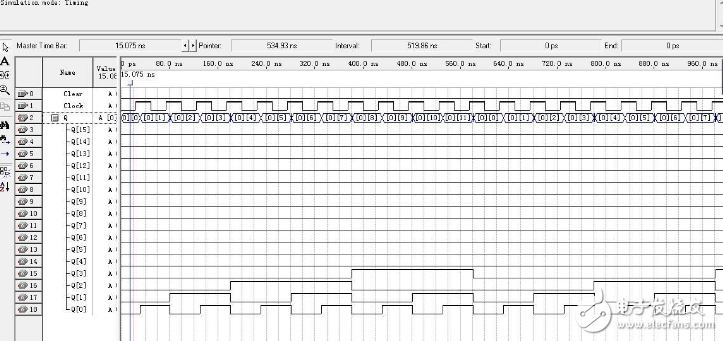

仿真結(jié)果

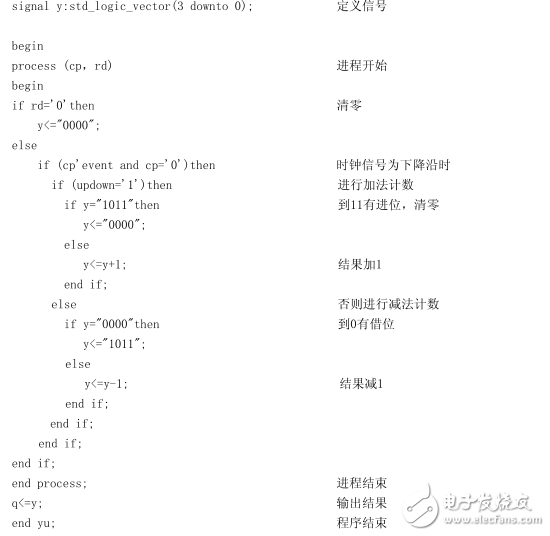

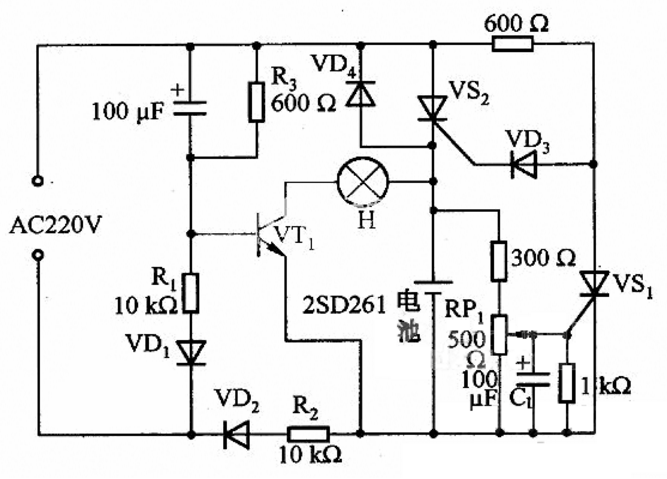

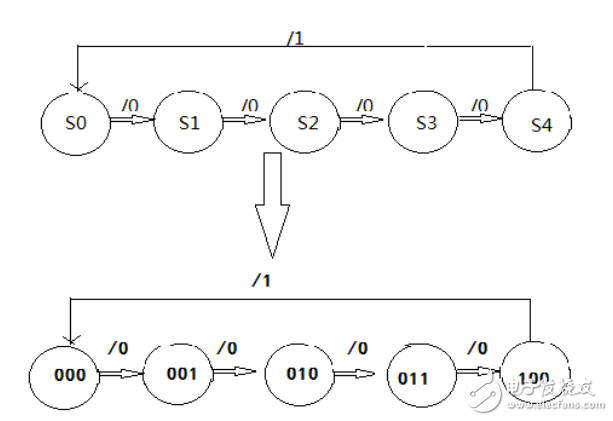

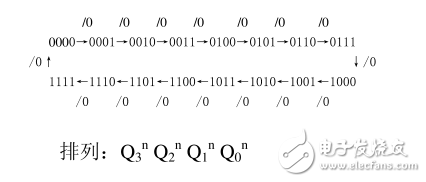

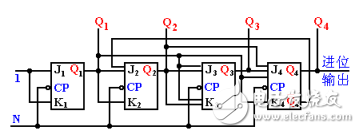

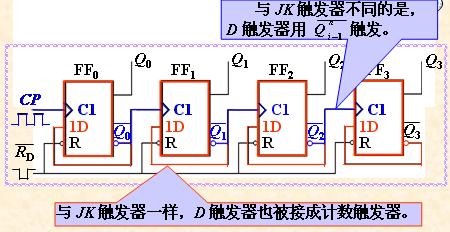

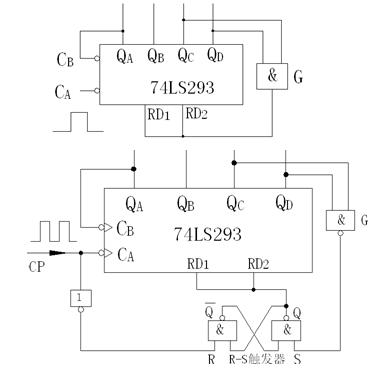

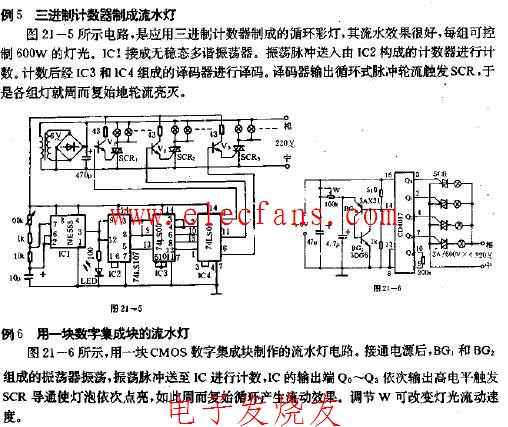

12進制計數(shù)器設(shè)計方案三:異步十二進制加減法計數(shù)器設(shè)計1

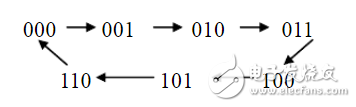

VHDl設(shè)計思路

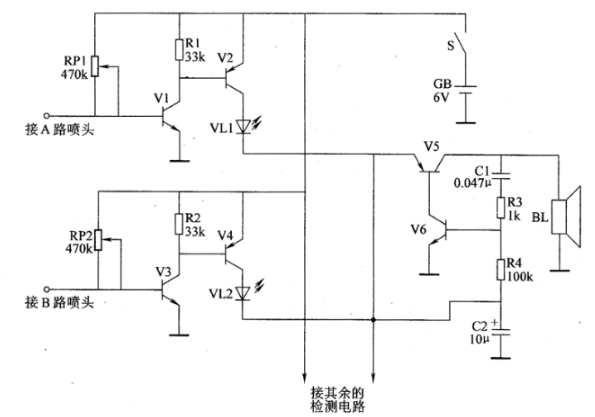

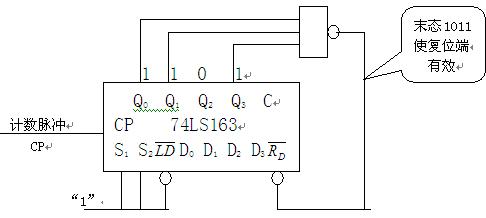

設(shè)計中,CP 是時鐘輸入端,下降沿有效;Rd 為清零控制端,低電平有效; updown 為計數(shù)方式控制端,updown=“1”時作加法計數(shù),updown=“0”時作減法計數(shù)。在計數(shù)工作之前,先由Rd 給一個清零信號,使四個數(shù)據(jù)輸入值都為“0”。y3,y2,y1,y0 為四個數(shù)據(jù)輸出端,這就實現(xiàn)了異步清零。當Rd=“1”時,計數(shù)器進行加法計數(shù),即從“0000”依次計數(shù)到“1011”,當updown= “0”,updown=“1”,Rd=“1”時,計數(shù)器進行減法計數(shù)。

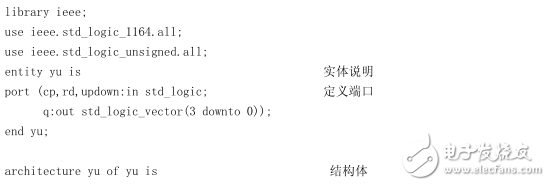

程序設(shè)計

電子發(fā)燒友App

電子發(fā)燒友App

評論