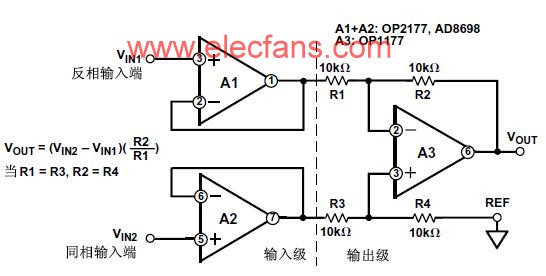

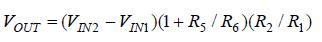

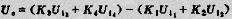

帶輸入緩沖的減法器電路

- 減法(8251)

相關推薦

頂層為原理圖的能顯示16進制減法計數器設計

)。(在圖6-1中為KZ模塊,其中Q(3:0)為數據輸出信號,D(2:0)為輸出位選通信號)。2.用VHDL設計一個16進制減法器,并用ModelSim Simulator 仿真驗證。3.用VHDL設計一

2009-10-11 08:51:38

FPGA常用運算模塊-加減法器和乘法器

本文是本系列的第二篇,本文主要介紹FPGA常用運算模塊-加減法器和乘法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:13:57 1336

1336

1336

1336

數字電路基礎知識分享4

本小節將從這些邏輯器件,門電路,觸發器開始,搭建一些相對復雜點的功能電路,比如加法器和減法器等。從這個過程中,體會一下如何從基本邏輯門開始,構建功能稍微復雜的電路。

2023-05-04 15:23:43 373

373

373

373

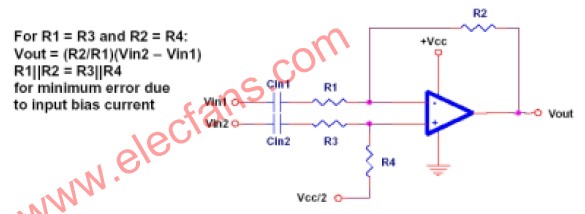

如何將運算放大器用作差分放大器查找電壓值的電壓差

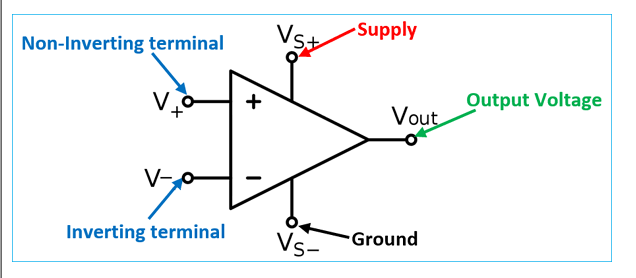

在本教程中,我們將學習如何將運算放大器用作差分放大器來查找兩個電壓值之間的電壓差。它也被稱為電壓減法器。我們還將在面包板上嘗試電壓減法器電路,并檢查電路是否按預期工作。

2022-09-22 17:16:46 3722

3722

3722

3722

DSP48E1片的數據和控制輸入提供算術和邏輯階段

DSP48E1片的數學部分由一個25位的預加器、2個25位、18位的補法器和3個48位的數據路徑多路復用器(具有輸出X、Y和Z)組成,然后是一個3輸入加法器/減法器或2輸入邏輯單元(參見圖2-5)。使用2輸入邏輯單元時,不能使用乘法器。

2022-01-21 14:14:26 842

842

842

842計算機為什么要使用補碼

,增加了計算的時間,能不能用加法器實現減法器的功能?這個實現的過程就用到了補碼。 計算機為什么使用補碼?采用補碼可以簡化計算機硬件電路設計的復雜度。 對于有符號數,內存要區分符號位和數值位,要是能把符號位和數值位

2021-09-12 16:06:43 5873

5873

5873

5873DSP48E1詳解(2):簡化DSP48E1片操作

DSP48E1片的數學部分由一個25位的預加器、2個25位、18位的補法器和3個48位的數據路徑多路復用器(具有輸出X、Y和Z)組成,然后是一個3輸入加法器/減法器或2輸入邏輯單元(參見圖2-5)。使用2輸入邏輯單元時,不能使用乘法器。

2021-01-29 08:19:37 13

13

13

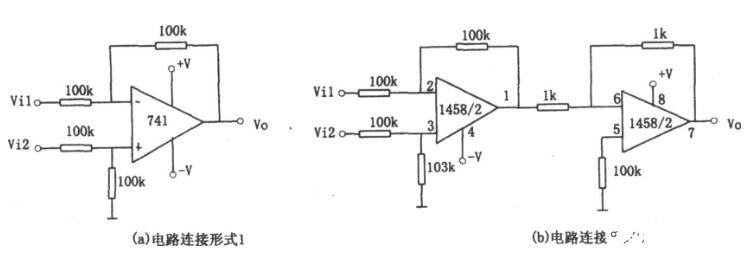

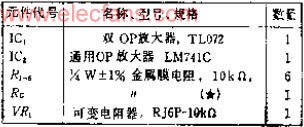

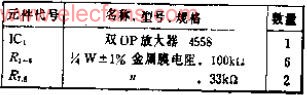

13三款減法器電路圖分享

V0=Vi2-Vi1圖中放大器的輸出信號電壓極性通常與輸入電壓極性相同。如果要求反相輸出,則采用圖(b)所示電路。其輸入輸出關系為:Vo=Vi1-Vi2。

2019-12-31 14:22:49 36625

36625

36625

36625

一些基礎的運用電路合集免費下載

本文檔的一些基礎的運用電路合集免費下載包括了:反向放大器同向放大器加法器減法器積分電路微分電路電壓轉換成電流差分放大電路電流轉換成電壓。

2019-11-12 08:00:00 37

37

37

37關于運放電路分析和介紹

分析運放電路的工作原理時,緊扣“虛短”和“虛斷”兩個概念,再結合電路原理進行計算即可,非常方便,不需要記什么同向放大、反向放大,什么加法器、減法器、差分輸入等計算公式。

2019-10-25 11:29:48 11504

11504

11504

11504運算放大器積分電路和斜坡發生器方程

積分器運算放大器產生的輸出電壓與輸入信號的幅度和持續時間成正比,可用作正反饋放大器或負反饋放大器的一部分或作為加法器或減法器類型的電路,在輸入和反饋環路中僅使用純電阻。

2019-06-26 09:28:12 42334

42334

42334

42334

12位加法器的實驗原理和設計及腳本及結果資料說明

加法器是數字系統中的基本邏輯器件。例如:為了節省資源,減法器和硬件乘法器都可由加法器來構成。但寬位加法器的設計是很耗費資源的,因此在實際的設計和相關系統的開發中需要注意資源的利用率和進位速度等兩方面的問題。

2019-04-15 08:00:00 4

4

4

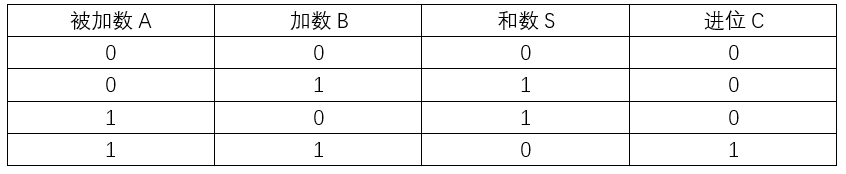

4加法器與減法器_反相加法器與同相加法器

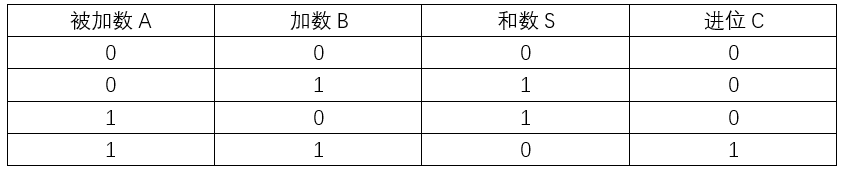

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構成,也可以由差分電路構成。基本集成運放電路有加、減、積分和微分等四種運算。一般是由集成運放外加反饋網絡所構成的運算電路來實現。

2017-08-16 11:09:48 157219

157219

157219

157219

同相加法器電路原理與同相加法器計算

同相加法器輸入阻抗高,輸出阻抗低 反相加法器輸入阻抗低,輸出阻抗高.加法器是一種數位電路,其可進行數字的加法計算。當選用同相加法器時,如A輸入信號時,因為是同相加法器,輸入阻抗高,這樣信號不太容易流入加法器,反而更容易流入B端。

2016-09-13 17:23:33 54133

54133

54133

54133

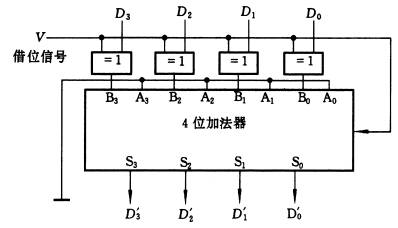

本的二進制加法/減法器,本的二進制加法/減法器原理

本的二進制加法/減法器,本的二進制加法/減法器原理

兩個二進制數字Ai,Bi和一個進位輸入Ci相加,產生一個和輸出Si,以及一個進位輸

2010-04-13 11:11:55 5077

5077

5077

5077并行除法器 ,并行除法器結構原理是什么?

并行除法器 ,并行除法器結構原理是什么?

1.可控加法/減法(CAS)單元 和陣列乘法器非常相似,陣列式除法器也是一種并行運算部件,采用大規模集成

2010-04-13 10:46:30 14405

14405

14405

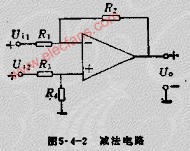

14405使用三運放搭建輸入緩沖級和輸出級電路

使用三運放搭建輸入緩沖級和輸出級電路

傳統IA使用三運放搭建輸入緩沖級和輸出級電路(圖2)。輸入緩沖級電路提供全差分增益、單位共模增益和高阻輸入,差分

2009-12-07 22:47:26 1789

1789

1789

1789

含運算放大器的電路的分析

1.運放的傳輸特性2.比例器、加法器、減法器、跟隨器等運算電路3.含理想運放的運算電路的分析計算 難點 熟練計算含理想運放的思路 運放的電路模型

2009-07-08 09:09:19 74

74

74

74減法運算

減法運算

同加法運算一樣,減法運算可采用減法器來實現。半減器和全減器的設計方法和步驟與設計加法器相同。實用上,為了簡化系統結構,通常不另外設計減

2009-04-07 10:38:39 12577

12577

12577

12577

電子發燒友App

電子發燒友App

評論