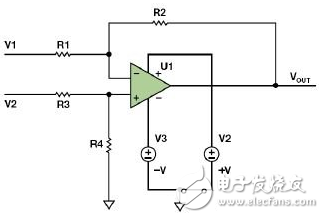

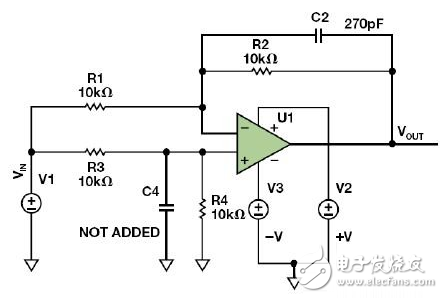

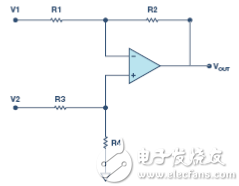

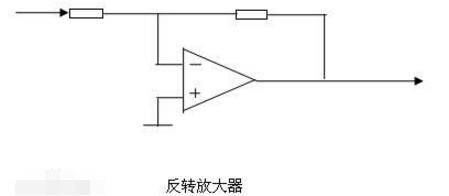

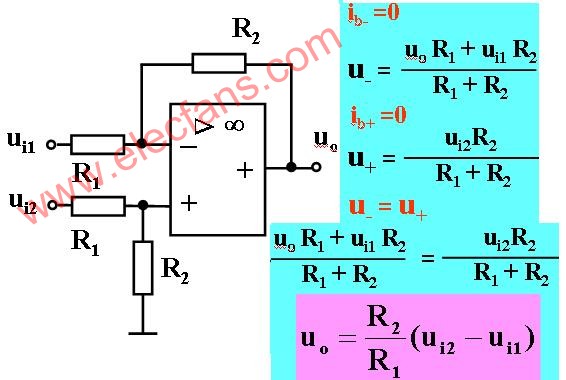

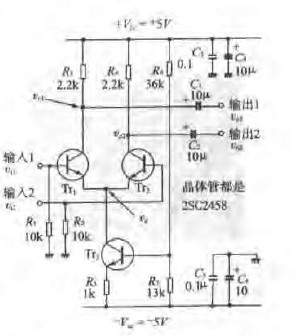

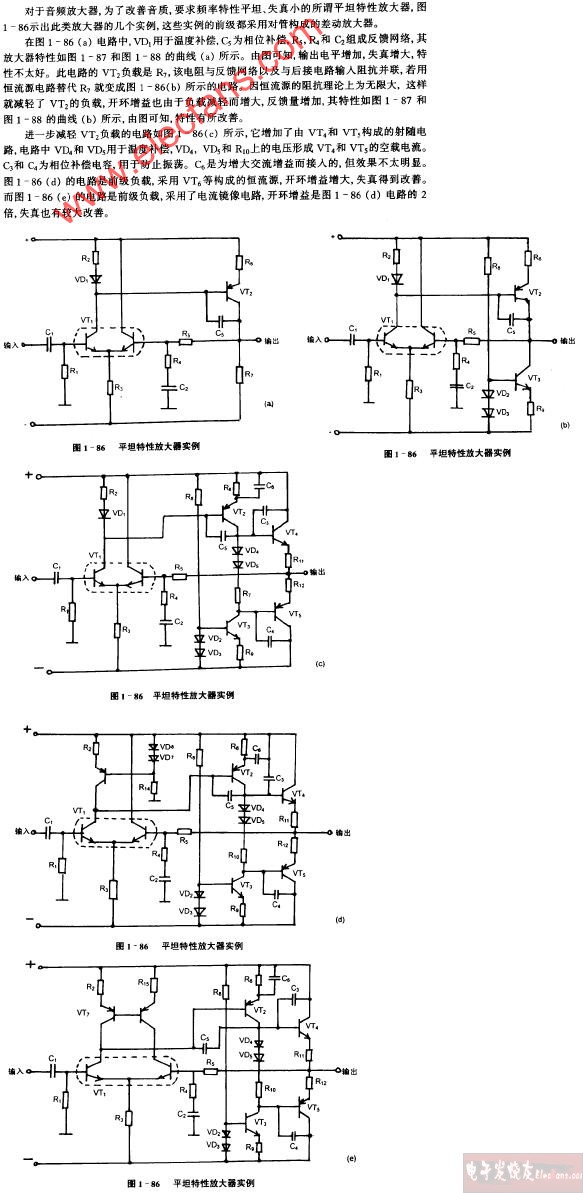

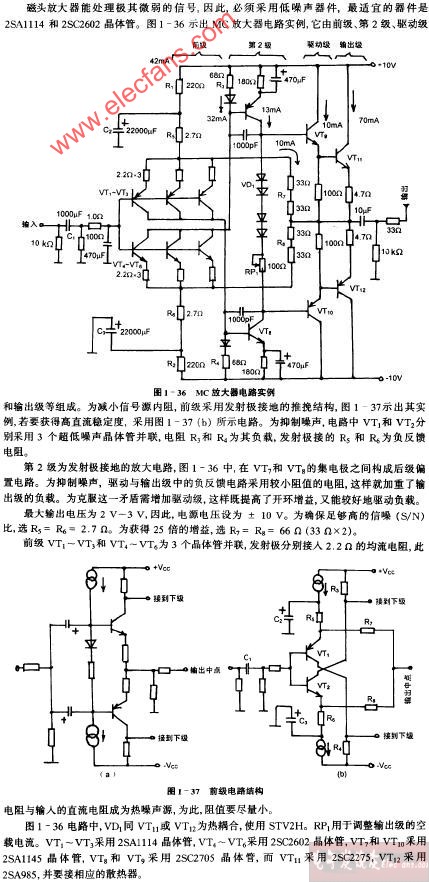

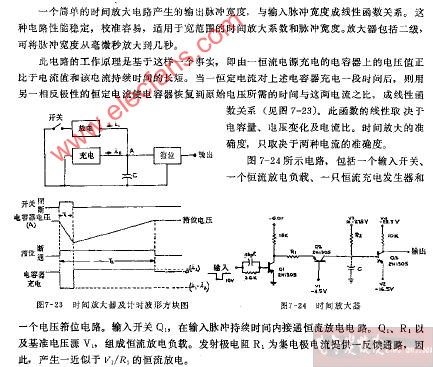

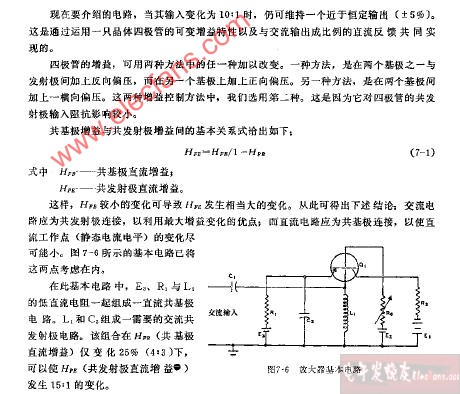

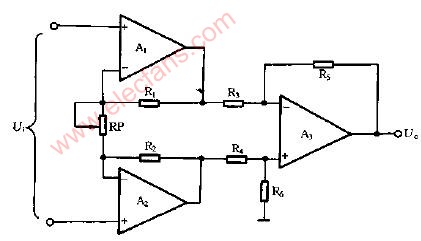

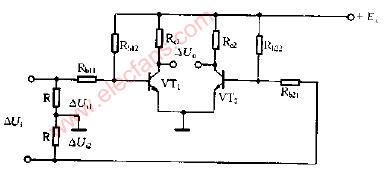

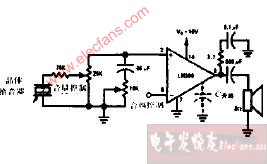

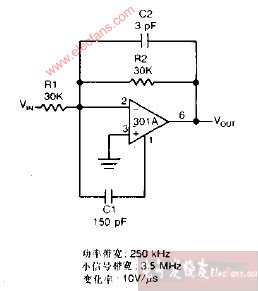

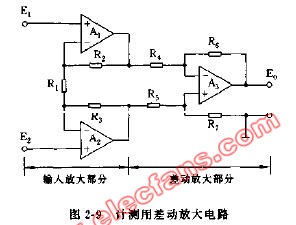

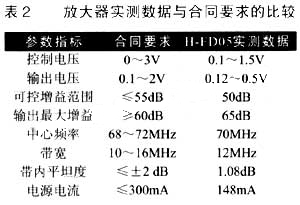

經典的四電阻差動放大器 (Differential amplifier,差分放大器) 似乎很簡單,但其在電路中的性能不佳。本文從實際生產設計出發,討論了分立式電阻、濾波、交流共模抑制和高噪聲增益的不足之處。大學里的電子學課程說明了理想運算放大器的應用,包括反相和同相放大器,然后將它們進行組合,構建差動放大器。圖 1 所示的 經典四電阻差動放大器非常有用,教科書和講座 40 多年來一直在介紹該器件。

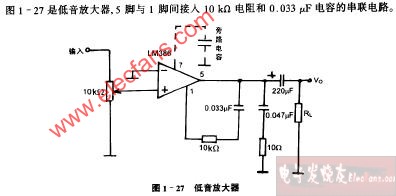

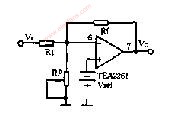

圖 1. 經典差動放大器

這種簡化可以在教科書中看到,但現實中無法這樣做,因為電阻永遠不可能完全相等。此外,基本電路在其他方面的改變可 產生意想不到的行為。下列示例雖經過簡化以顯示出問題的本質,但來源于實際的應用問題。

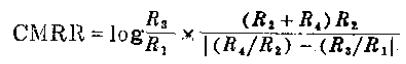

差動放大器的一項重要功能是抑制兩路輸入的共模信號。如圖1 所示,假設V2 為 5 V,V1 為 3 V,則4V為共模輸入。V2 比共模電壓高 1 V,而V1 低 1 V。二者之差為 2 V,因此R2/R1的“理想”增益施加于2 V。如果電阻非理想,則共模電壓的一部分將被差動放大器放大,并作為V1 和V2 之間的有效電壓差出現在VOUT ,無法與真實信號相區別。差動放大器抑制這一部分電壓的能力稱為共模抑制(CMR)。該參數可以表示為比率的形式(CMRR),也可以轉換為分貝(dB)。

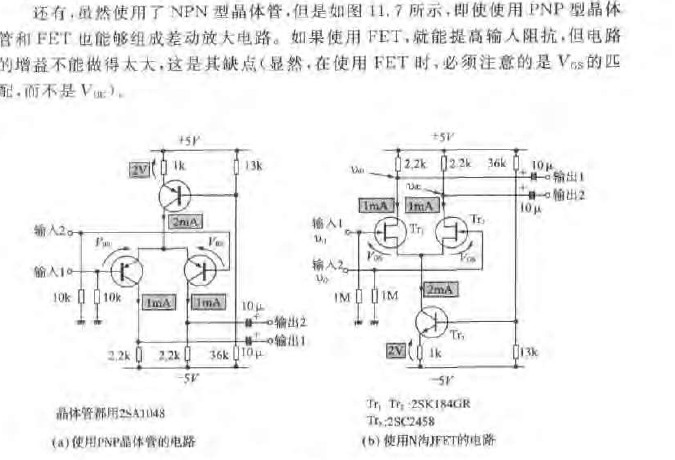

低容差電阻

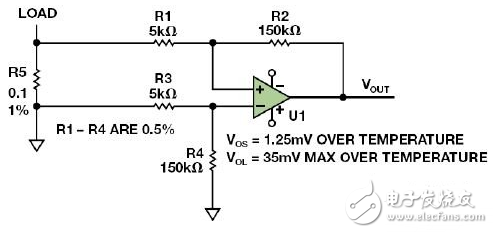

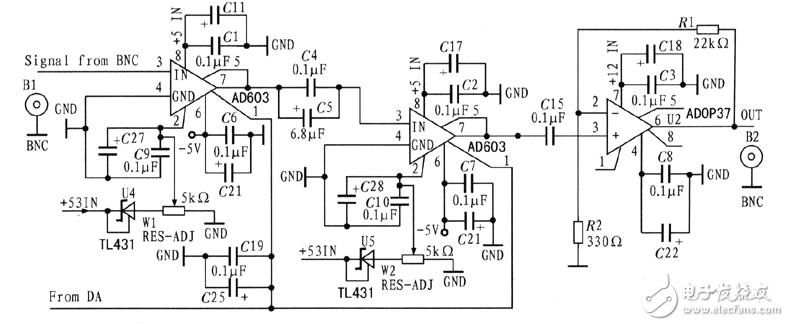

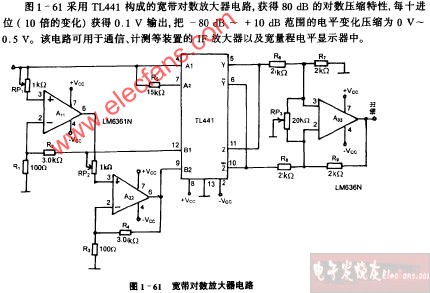

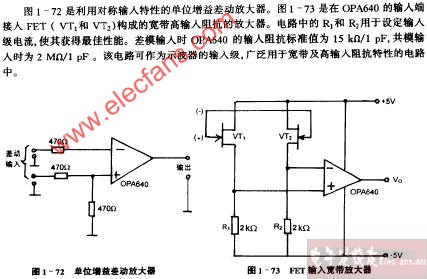

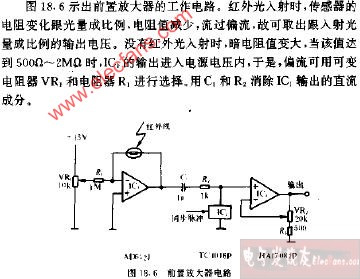

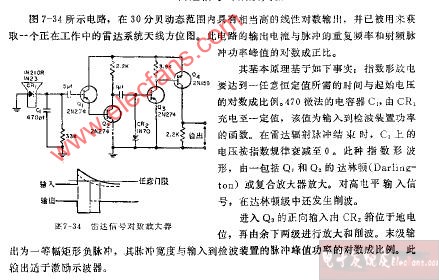

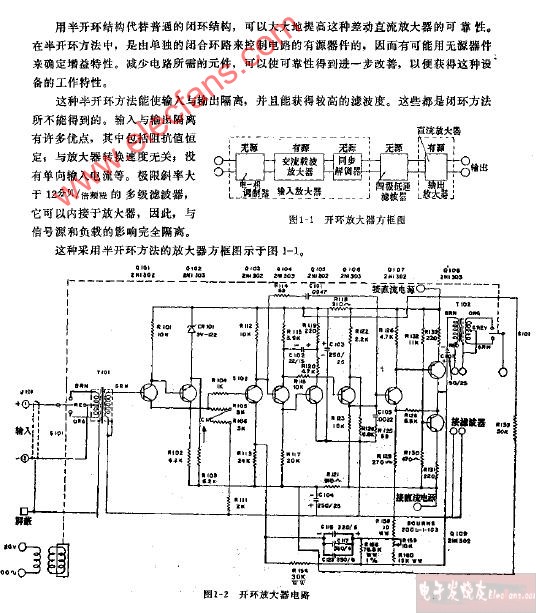

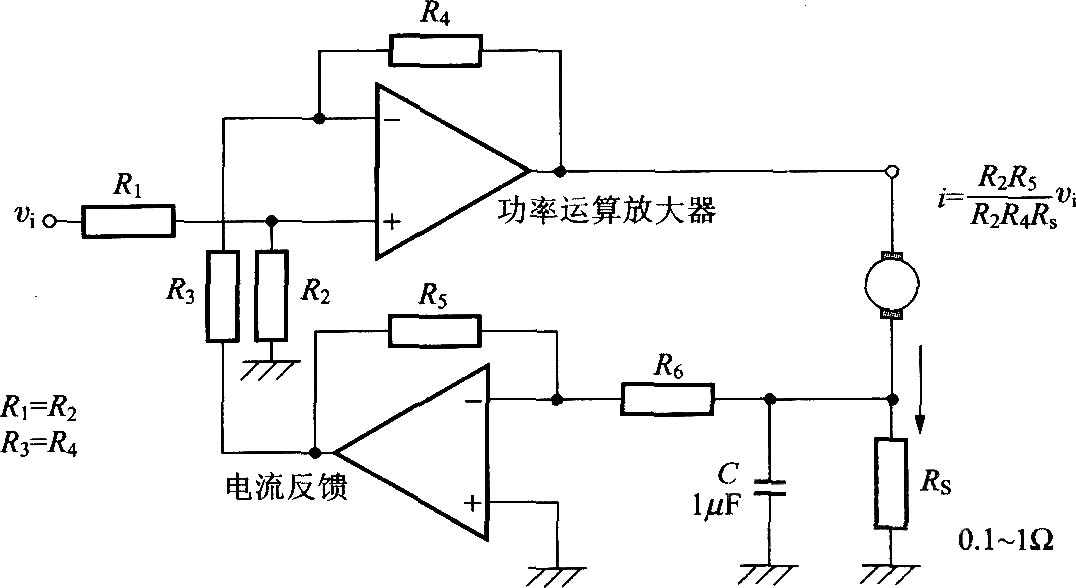

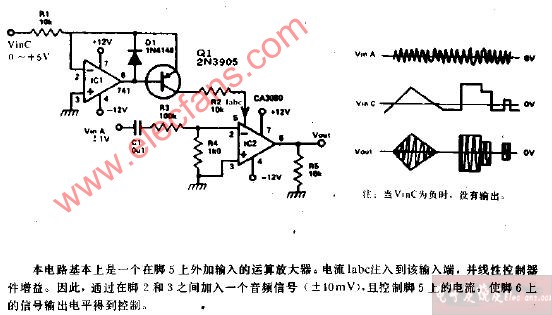

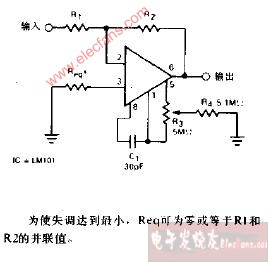

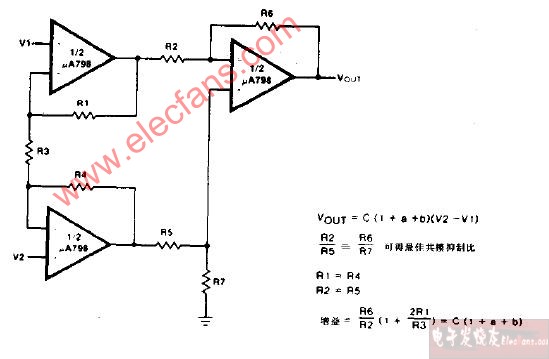

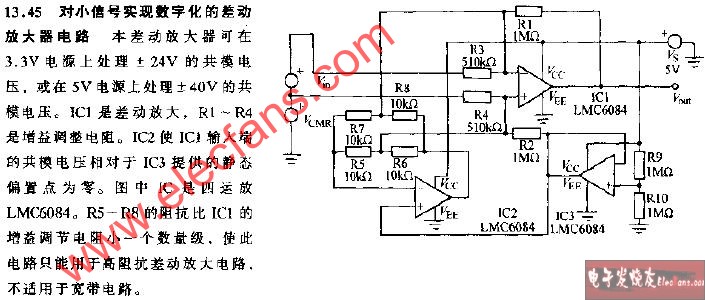

第一個次優設計如圖 2 所示。該設計為采用OP291 的低端電流檢測應用。R1 至R4 為分立式 0.5%電阻。由Pallás-Areny文章中的公式可知,最佳CMR為 64 dB.幸運的是,共模電壓離接地很近,因此CMR并非該應用中主要誤差源。具有 1%容差的電流檢測電阻會產生 1%誤差,但該初始容差可以校準或調整。然而,由于工作范圍超過 80°C,因此必須考慮電阻的溫度系數。

圖 2. 具有高噪聲增益的低端檢測

針對極低的分流電阻值,應使用 4 引腳開爾文檢測電阻。采用高精度 0.1 Ω電阻,并以幾十分之一英寸的PCB走線直接連接該電阻很容易增加 10 mΩ,導致10%以上的誤差。但誤差會更大,因為PCB上的銅走線溫度系數超過 3000 ppm。分流電阻值必須仔細選擇。數值更高則產生更大的信號。這是 好事,但功耗(I2R) 也會隨之增加,可能高達數瓦。采用較小的 數值(mΩ級別),則線路和PCB走線的寄生電阻可能會導致較 大的誤差。通常使用開爾文檢測來降低這些誤差。可以使用一 個特殊的四端電阻(比如Ohmite LVK系列),或者對PCB布局進行優化以使用標準電阻。若數值極小,可以使用PCB 走線,但這樣不會很精確。商用四端電阻(比如Ohmite或Vishay的產品)可能需要數美元或更昂貴,才能提供 0.1%容差和極低溫度系數。進行完整的誤差預算分析可以顯示如何在成本增加最少的情況下改善精度。

有關無電流流過檢測電阻卻具有較大失調(31mV)的問題,是“軌到軌”運算放大器無法一路擺動到負電源軌(接地)引起 的。術語“軌到軌”具有誤導性:輸出將會靠近電源軌--比經典發射極跟隨器的輸出級要近得多--但永遠不會真正到達電源軌。軌到軌運算放大器具有最小輸出電壓VOL,數值等 于VCE(SAT) 或RDS(ON) × ILOAD。若失調電壓等于 1.25 mV,噪聲增益等于 30,則輸出等于:1.25 mV × 30 = ±37.5 mV(由于存在VOS,加上VOL導致的 35 mV)。根據VOS極性不同,無負載電流的情況下輸出可能高達 72.5 mV。若VOS 最大值為 30μV,且VOL 最大值為 8 mV,則現代零漂移放大器(如 AD8539)可將總誤差降低至主要由檢測電阻所導致的水平。

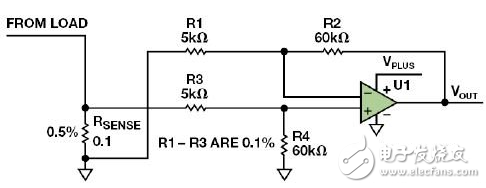

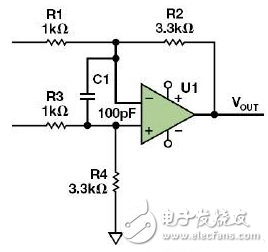

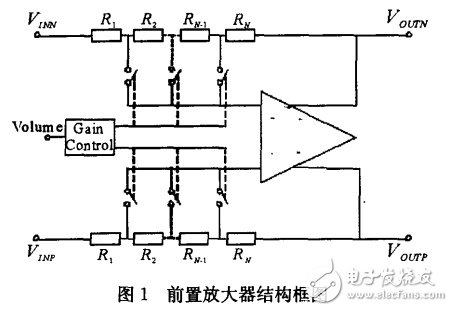

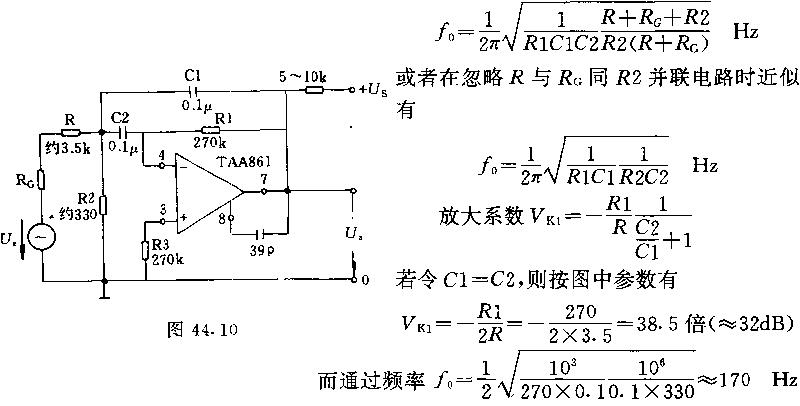

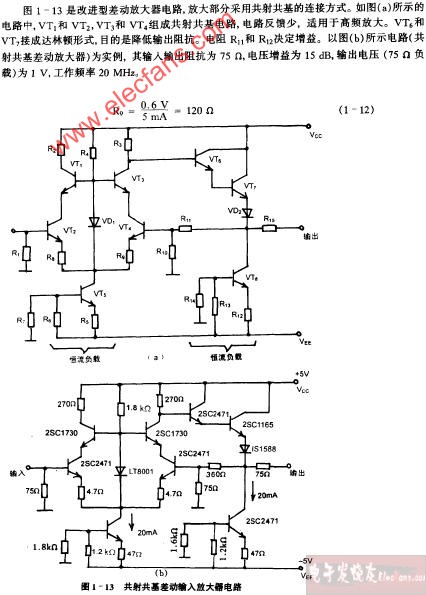

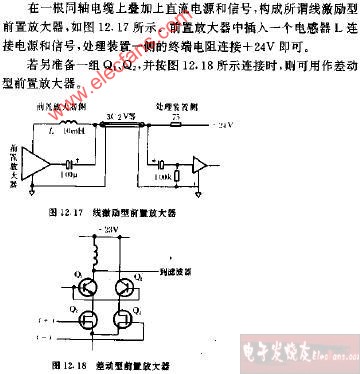

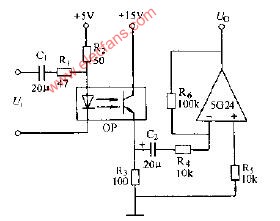

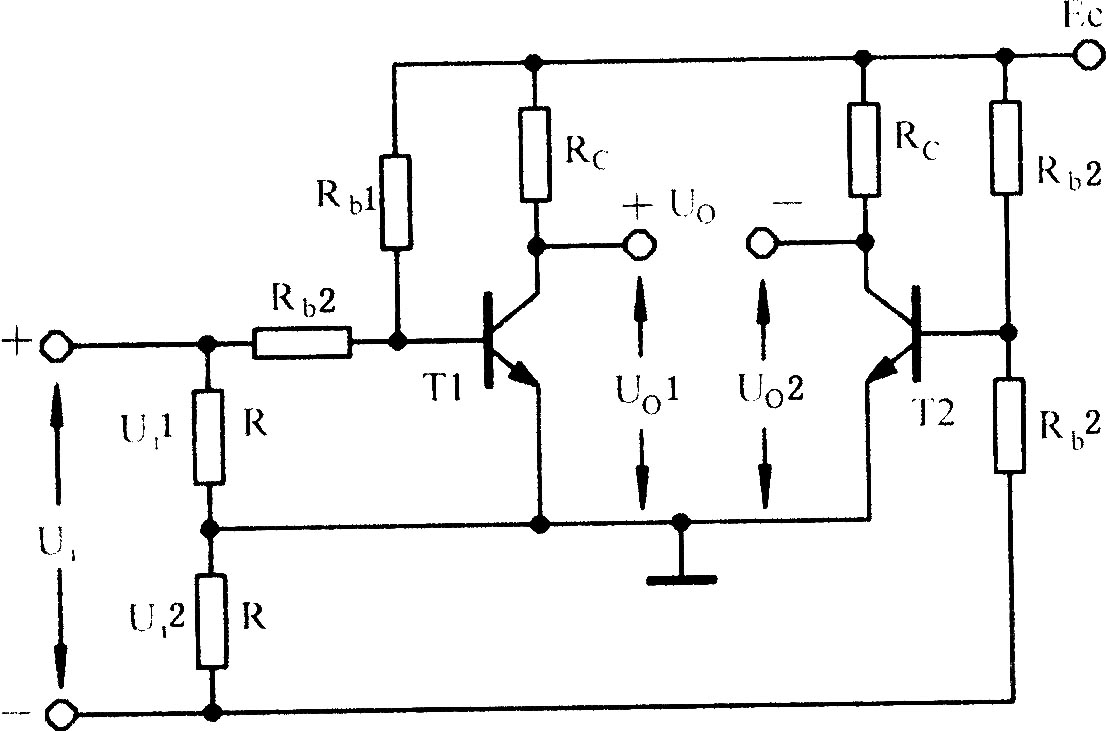

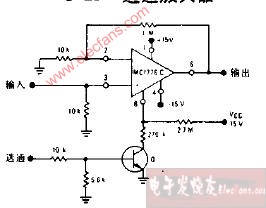

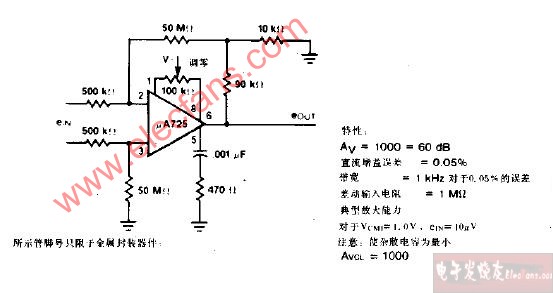

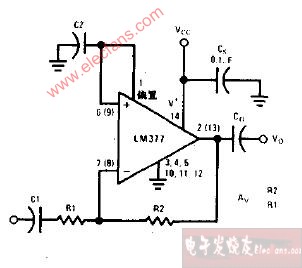

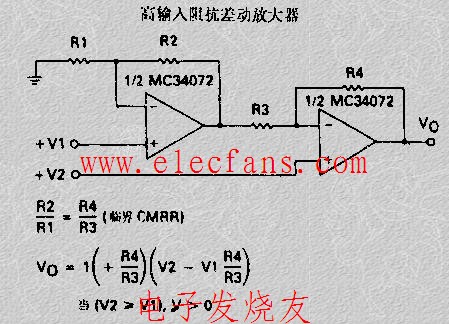

另一個低端檢測應用

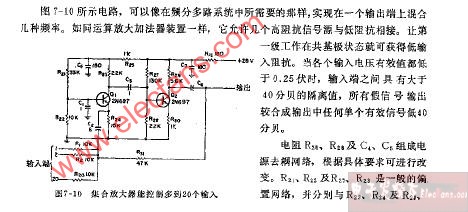

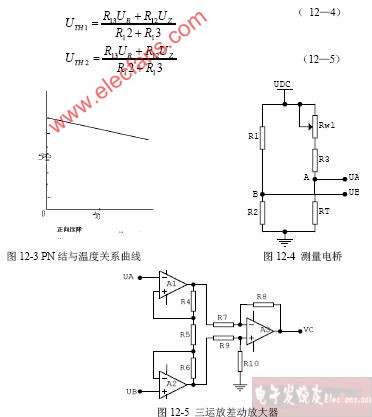

另一個示例如圖 3 所示。該示例具有較低的噪聲增益,但它使 用 3 mV失調、10-μV/°C失調漂移和 79 dB CMR的低精度四通道運算放大器。在 0 A至 3.6 A范圍內,要求達到±5 mA精度。若采用±0.5%檢測電阻,則要求的±0.14%精度便無法實現。若使用 100 mΩ電阻,則±5 mA電流可產生±500 μV壓降。不幸的是,運算放大器隨溫度變化的失調電壓要比測量值大十倍。哪怕VOS 調整為零,50°C的溫度變化就會耗盡全部誤差預算。若噪聲增益為 13,則VOS的任何變化都將擴大 13 倍。為了改善性能,應使用零漂移運算放大器(比如 AD8638、 ADA4051或 ADA4528)、薄膜電阻陣列以及精度更高的檢測電阻。

圖 3. 低端檢測,示例 2

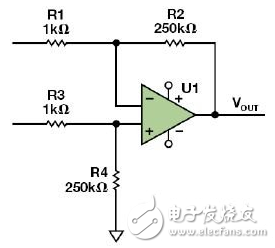

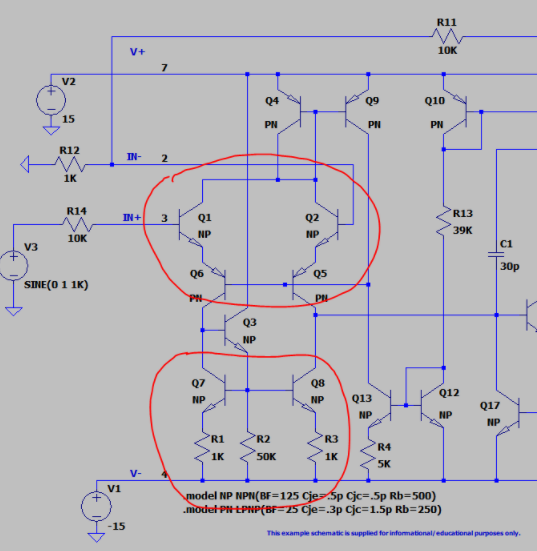

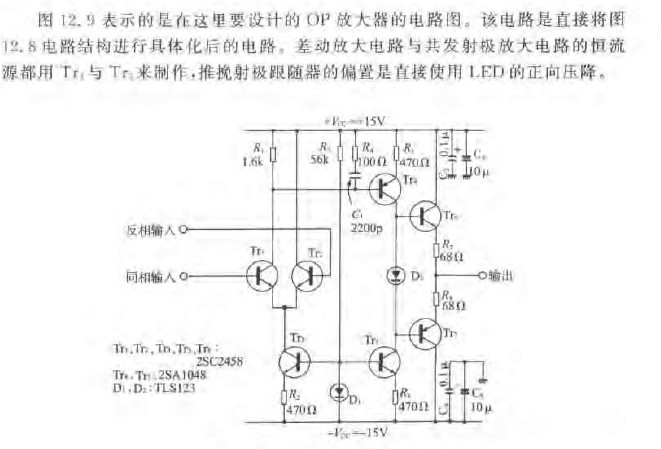

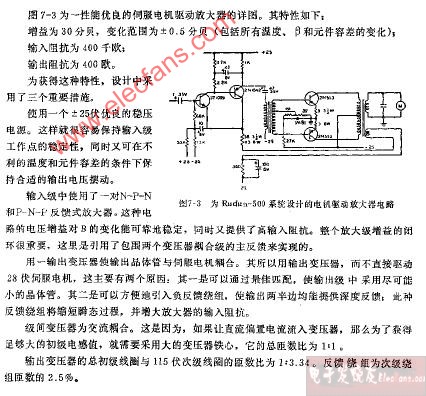

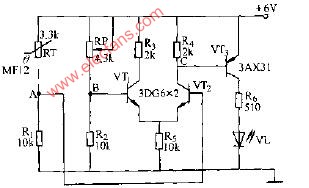

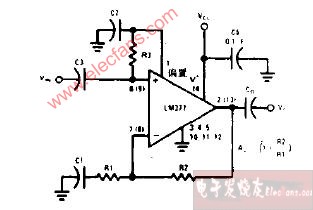

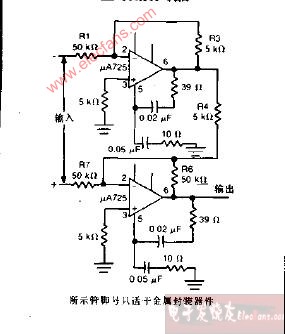

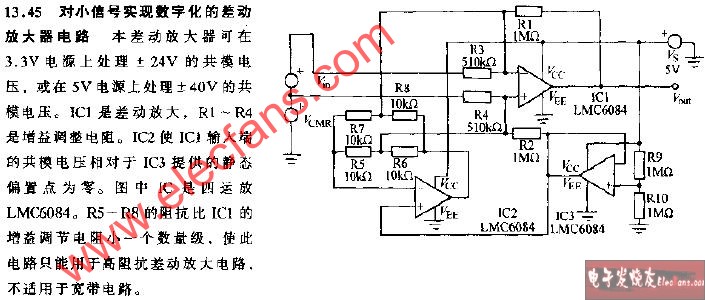

高噪聲增益

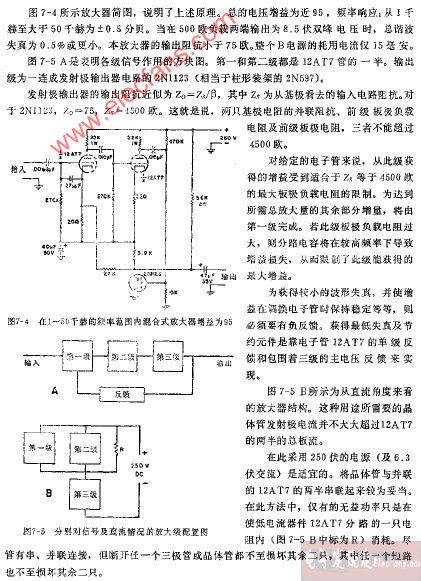

圖 4 中的設計用來測量高端電流,其噪聲增益為 250。OP07C運算放大器的VOS最大額定值為 150 μV.最大誤差為 150 μV × 250 = 37.5 mV。為了改善性能,采用 ADA4638 零漂移運算放大器。該器件在-40°C至+125°C溫度范圍內的額定失調電壓為 12.5 μV。然而,由于高噪聲增益,共模電壓將非常接近檢測電阻兩端的電壓。OP07C的輸入電壓范圍(IVR)為 2 V,這表示輸入電壓必須至少比正電軌低 2 V.對于ADA4638 而言,IVR = 3 V。

圖 4. 高端電流檢測

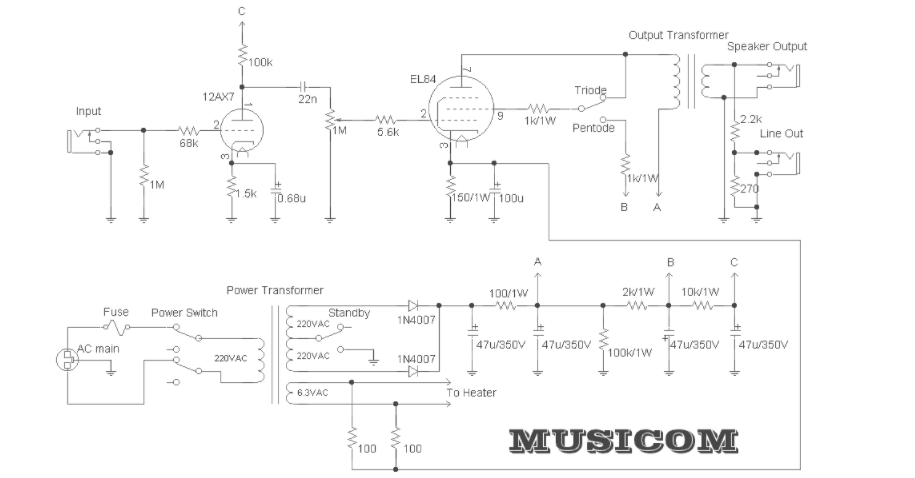

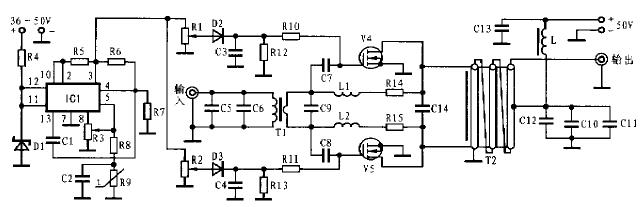

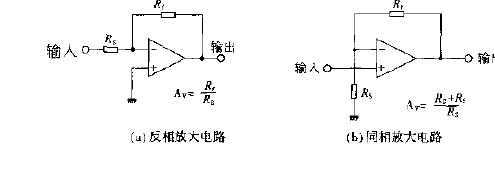

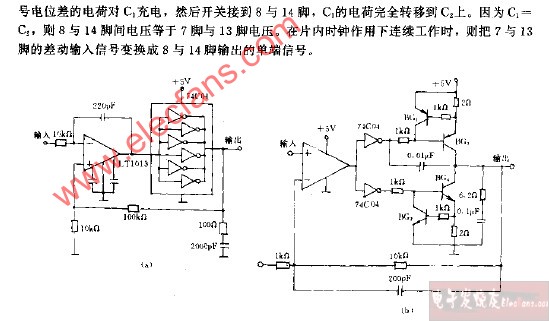

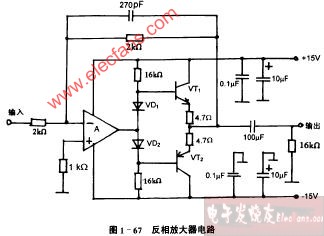

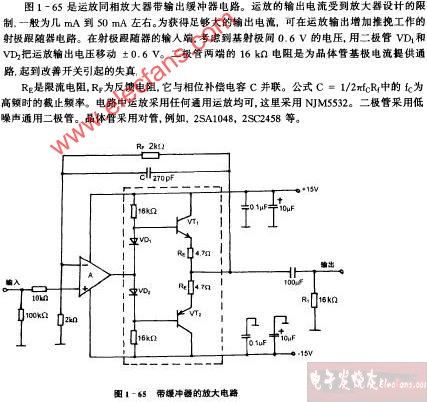

單電容滾降

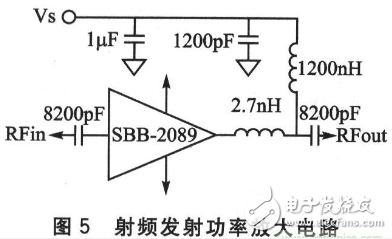

圖5 中的示例稍為復雜。目前為止,所有的等式都針對電阻而言;但更準確的做法是,它們應當將阻抗考慮在內。在加入電容的情況下(無論是故意添加的電容或是寄生電容),交流CMRR均取決于目標頻率下的阻抗比。若要滾降該示例中的頻率響應,則可在反饋電阻兩端添加電容C2,如通常會在反相運算放大器配置中做的那樣。

圖 5. 嘗試創建低通響應

如需匹配阻抗比Z1 = Z3 和Z2 = Z4,就必須添加電容C4.市場上很容易就能買到 0.1%或更好的電阻,但哪怕是0.5%的電容售價都要高于1 美元。極低頻率下的阻抗可能無關緊要,但電 容容差或PCB布局產生的兩個運算放大器輸入端 0.5 pF的差額可導致 10 kHz時交流CMR下降 6 dB。這在使用開關穩壓器時顯得尤為重要。單芯片差動放大器(如AD8271、 AD8274或 AD8276)具有好 得多的交流CMRR性能,因為運算放大器的兩路輸入處于芯片上的可控環境下,且價格通常較分立式運算放大器和四個精密電阻更為便宜。

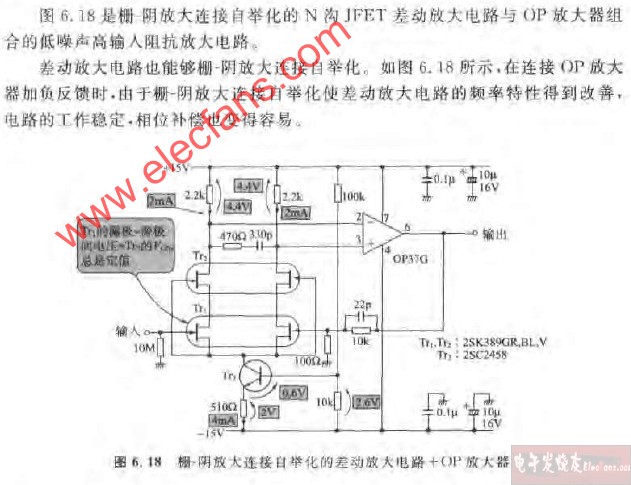

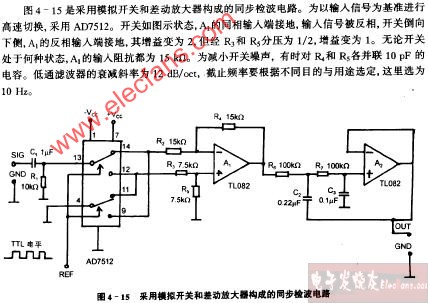

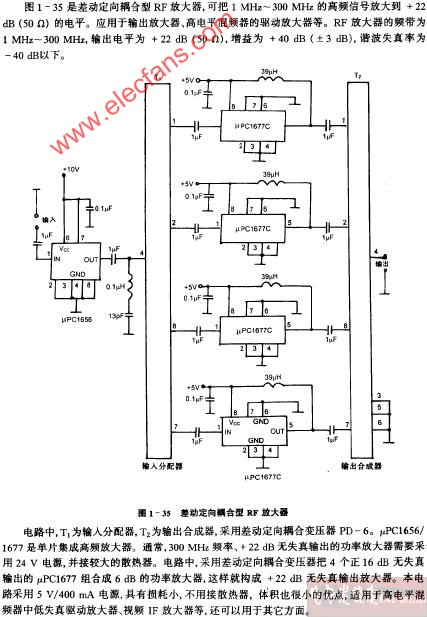

運算放大器輸入端之間的電容

為了滾降差動放大器的響應,某些設計人員會嘗試在兩個運算放大器輸入端之間添加電容C1 以形成差分濾波器,如圖 6 所示。這樣做對于儀表放大器而言是可行的,但對于運算放大器卻不可行。VOUT將會通過R2 而上下移動,形成閉合環路。在直流時,這不會產生任何問題,并且電路的表現與等式 2 所描 述的相一致。隨著頻率的增加,C1 電抗下降。進入運算放大器輸入端的反饋降低,從而導致增益上升。最終,運算放大器會在開環狀態下工作,因為電容使輸入短路。

圖 6. 輸入電容降低高頻反饋

在波特圖上,運算放大器的開環增益在-20dB/dec處下降,但噪聲增益在+20 dB/dec處上升,形成-40dB/dec交越。正如控制系統課堂上所學到的,它必然產生振蕩。一般而言,永遠不要在運算放大器的輸入端之間使用電容(極少數情況下例外,但本文不作討論)。

無論是分立式或是單芯片,四電阻差動放大器的使用都非常廣泛。為了獲得穩定且值得投入生產的設計,應仔細考慮噪聲增益、輸入電壓范圍、阻抗比和失調電壓規格。

電子發燒友App

電子發燒友App

評論