共模抑制比CMRR

運放的共模抑制比是常被關注的參數,尤其是在差分放大器和儀表放大器中。但這里只討論共模抑制比以及其帶來的誤差。

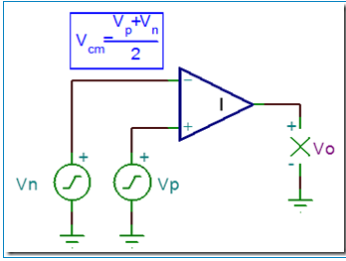

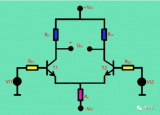

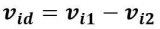

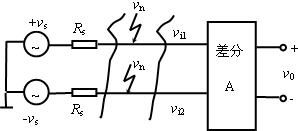

首先來了解下共模輸入電壓:指運放的兩個輸入引腳電壓的平均值。如下圖所示,對于雙極性輸入級的運放,運放的共模輸入電壓,一般達不到電源軌。而有些rail to rail 輸入運放的共模電壓是可以達到電源軌的。

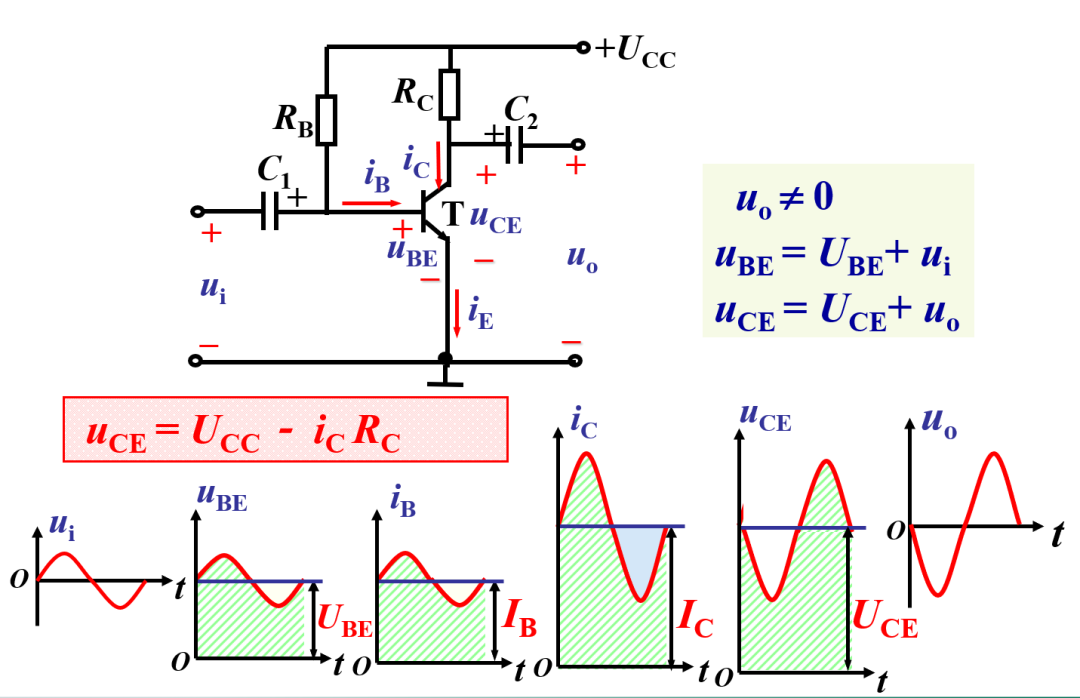

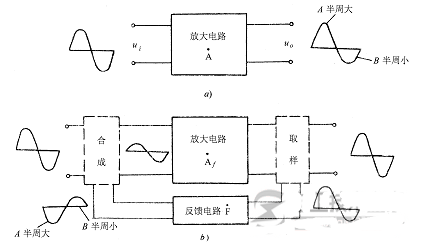

在理想運放中,差模放大倍數是無窮大,共模放大倍數是0.但是實際中卻達不到,不存在差模無窮大和共模放大0,于是就定義共模抑制比為差模增益與共模增益的比值。

還有一個參數很常見:CMR,它其實是CMRR的對數表示,如下:

這兩個參數經常被混用,不過只有了解他們都是在表示運放對共模信號的抑制能力就可以了。

運放之所以違背我們的期望,對共模信號進行放大,主要是如下原因:

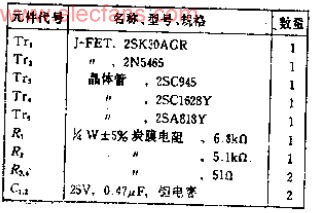

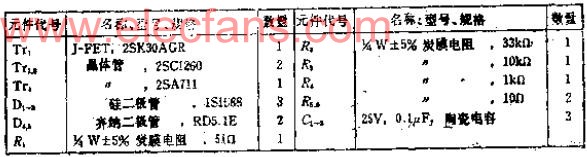

(1)運放輸入級的不匹配。這又可以分為 源極或漏極電阻的不匹配,信號源電阻不匹配,柵極-漏極電容不匹配,正向跨導不匹配以及柵極漏電流引起的不匹配問題;

(2)拖尾電流源的輸出阻抗;

(3)拖尾電流源的寄生電容會隨頻率的變化而變化。

下面就挑幾個看看其影響。

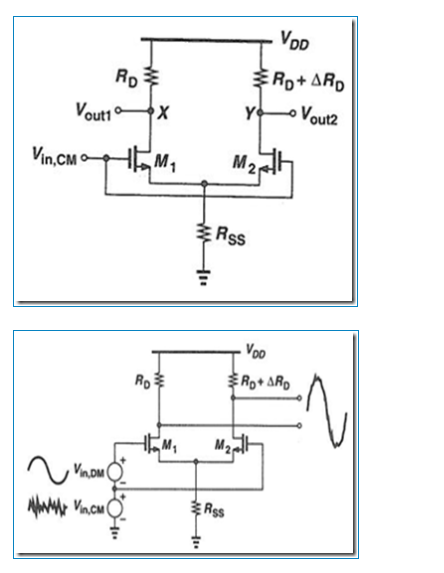

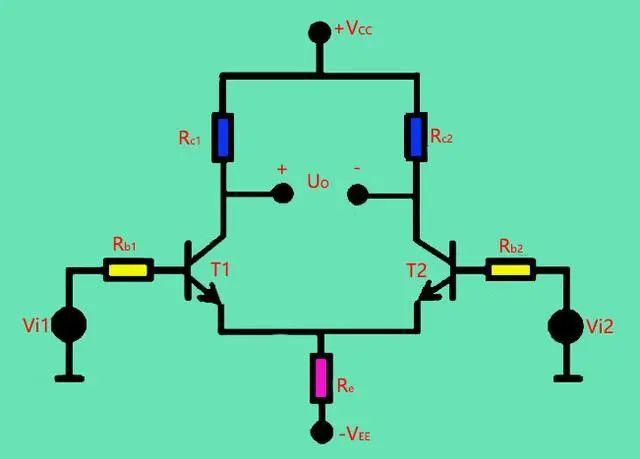

(1)電阻不匹配

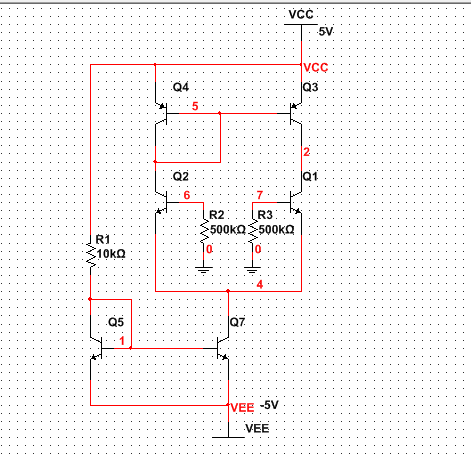

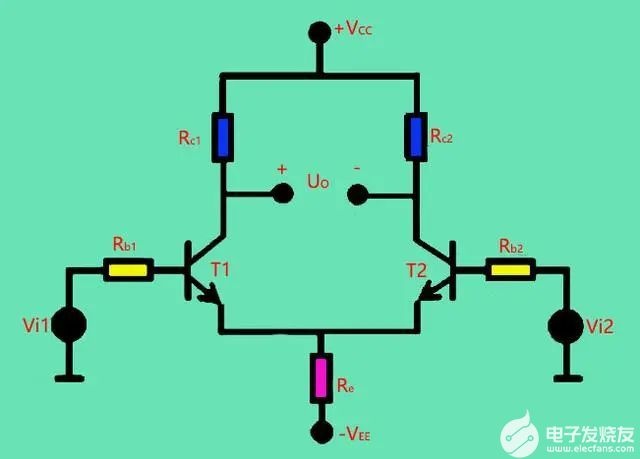

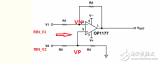

如下圖所示,由于電阻的不匹配,一個共模電壓的變化△Vin,會在X,Y 點轉化成一個差模電壓。

計算如下:

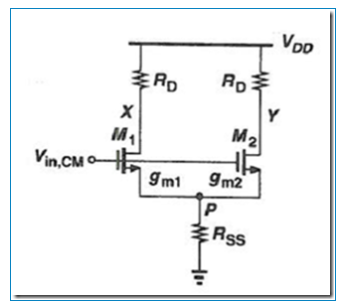

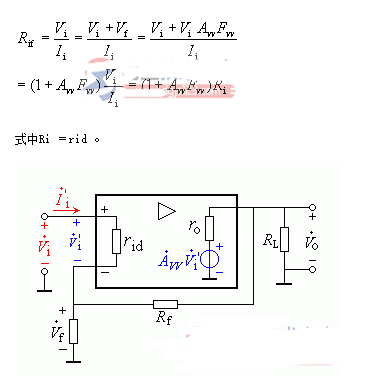

(2)晶體管的不匹配

管子的不匹配會導致兩管子的電流有微小差別,并且兩個的跨導是不一樣的。

由于輸入級管子的不匹配會導致共模信號轉化成一個差模的誤差,可以用下面的公式表示,它表示失配跨導引起的CMRR。

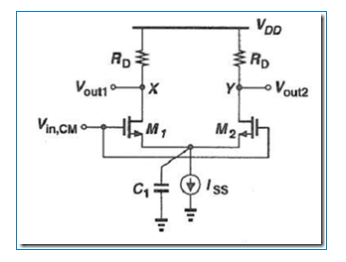

(3)拖尾恒流源的寄生電容隨頻率變化而變化

這個會引起恒流源電流的變化,差分輸入端射極或源極電阻用恒流源代替的目的是保持電流恒定和高阻抗。但它的電流如果隨頻率發生變化,勢必降低差分輸入端的共模抑制能力。如下圖:

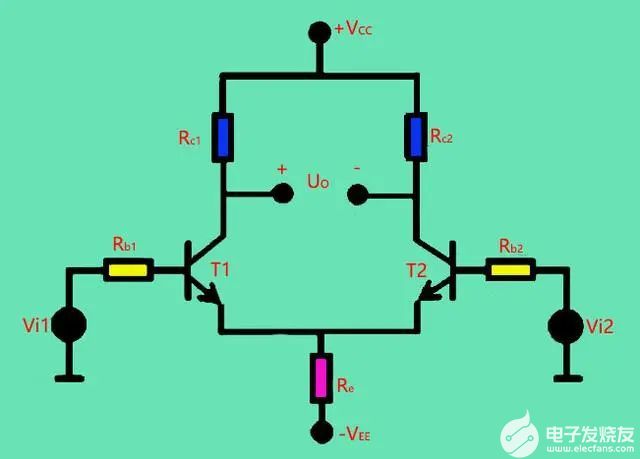

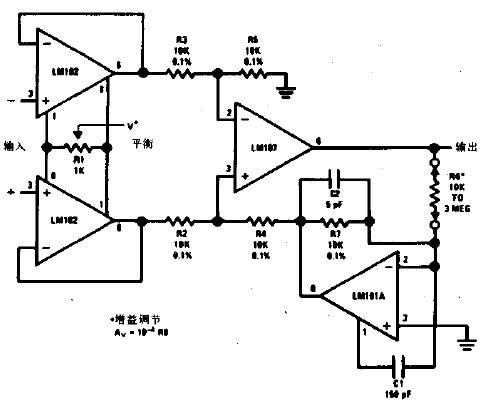

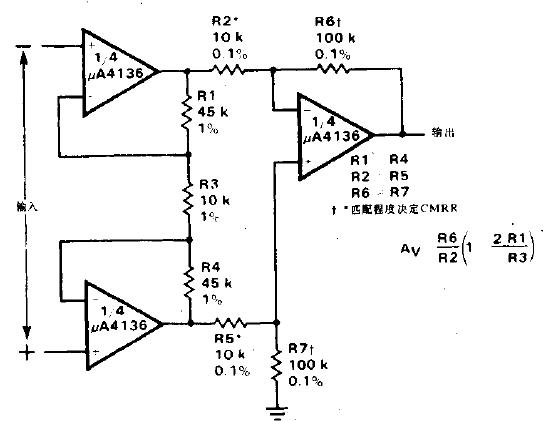

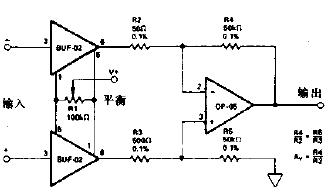

差分放大器和儀表放大器,無非是多個運放和電阻集成在了一起,只是用激光修調過,所以匹配度很好,所以CMRR比較高。如果自己用普通運放和外圍電阻搭建的話,CMRR很難達到集成的效果。

差分放大器和儀表放大器的CMRR主要受集成的差分放大電阻影響。因此掌握Trim電阻精度的工藝是制作儀放,差放的核心技術,可以參考Bruce Trump的博文“差動放大器—良好匹配電阻器不可或缺的器件”。

差分放大電路的CMRR與輸入電阻分析

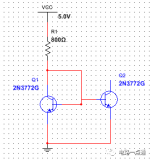

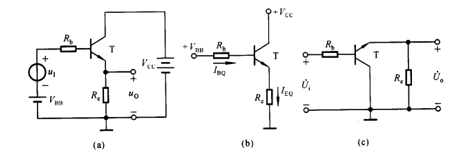

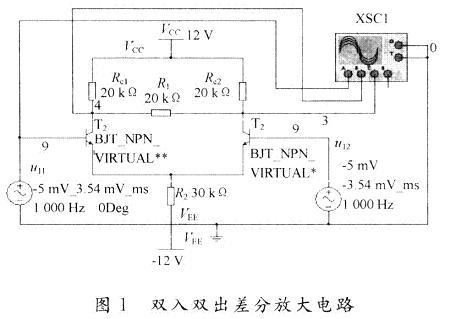

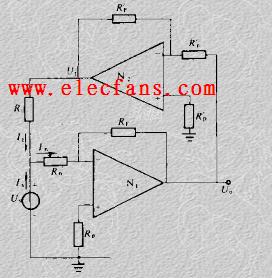

1.經典差分放大電路

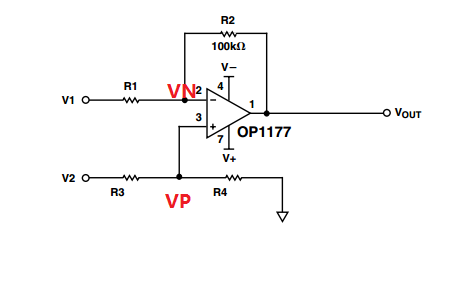

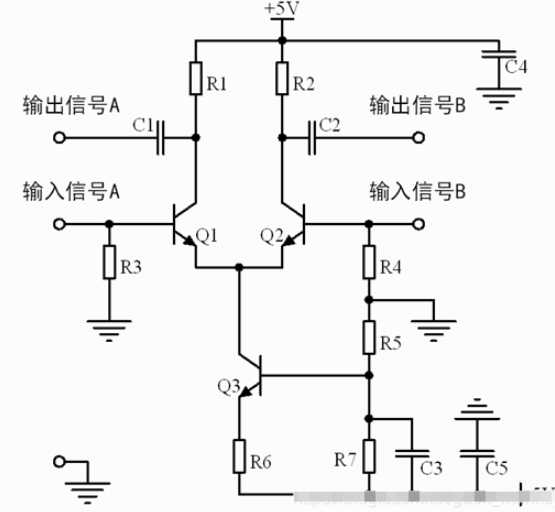

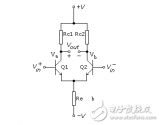

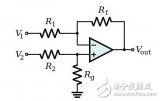

基于運放的經典差分放大電路在各模電教材中均能找到,利用分離電阻和運算放大器實現,如圖1所示為一種差分放大電路:

圖1 經典差分電路

(1)理想狀態下的分析

首先將OP1177看作理想運放,利用虛短、虛斷的原理,可以得到:

VP=V2*R4/(R3+R4)---------------------(1)

(V1-VN)/R1=(VN-VOUT)/R2------------(2)

VN=VP-------------------------------------(3)

整理式(1)~(3),可以得到:

VOUT=(R1+R2)*R4/(R1*(R3+R4))*V2-V1*R2/R1------(4)

當R4/R3=R2/R1的時候:

VOUT=(R2/R1)(V2-V1)------------------(5)

式(5)表示在理想狀態下,VOUT輸出的信號為輸入信號的差模輸出,并能完全抑制共模信號,并能實現差模信號的放大。

(2)實際狀態分析

為了便于分析,對于兩路輸入信號V2、V1,假設:

K1=VDEF=V2-V1------------------------(6)

K2=VCOM=(V2+V1)/2------------------(7)

其中VDEF表示差模輸入信號,VCOM表示共模輸入信號,為了方便計算,用系數K1、K2分別表示。

由式(6)、(7)整理得到:

V2=(2*K2+k1)/2--------------------------(8)

V1=(2*k2-k1)/2---------------------------(9)

將式(8)~(9)代入式(4)中,可以得到:

VOUT={((R1+R2)*R4+R2*(R3+R4))/(2*R1(R3+R4))}*K1+{(R1+R2)*R4-R2*(R3+R4)/(R1*(R3+R4))}*K2

=A_DM*K1+A_CM*K2

=A_DM*(V2-V1)+A_CM*((V2+V1)/2)--------------------------(10)

式(10)表示的含義是VOUT輸出信號中,將差模輸入信號V2-V1放大了A_DM倍,將共模信號(V2+V1)/2)放大了A_CM倍。

差模放大倍數A_DM表示為:

A_DM=(R1+R2)*R4+R2*(R3+R4))/(2*R1(R3+R4))-----------------(11)

共模放大倍數A_CM表示為:

A_CM=(R1+R2)*R4-R2*(R3+R4)/(R1*(R3+R4))--------------------(12)

則共模抑制比CMRR可以表示為:

CMRR=|A_DM/A_CM|=|(R1*R4+2*R2*R4+R2*R3)/(R1*R4-R2*R3)|-----------(13)

式(13)表示當R4/R3=R2/R1的時候,差分電路的共模抑制比CMRR一定會達到無窮大,此時的輸出信號VOUT中將不再包含任何的共模信號。

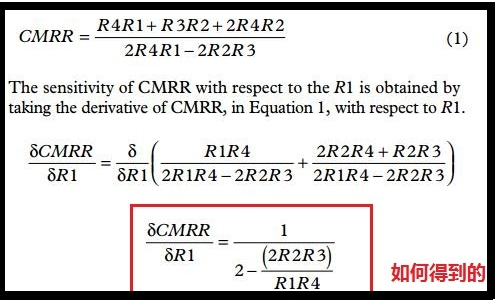

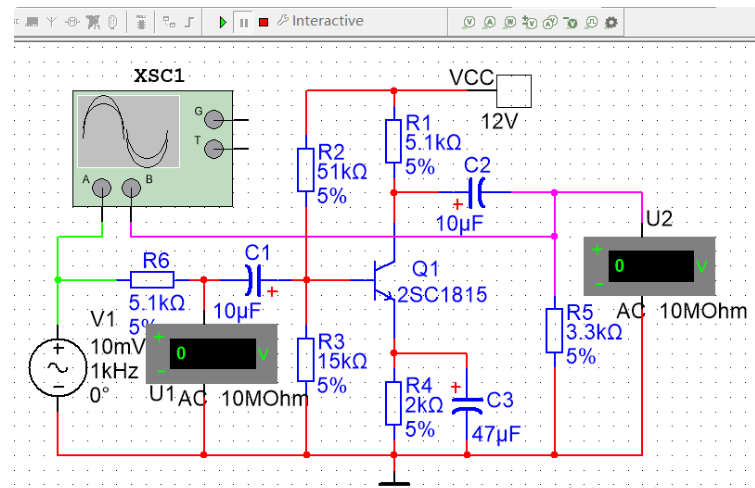

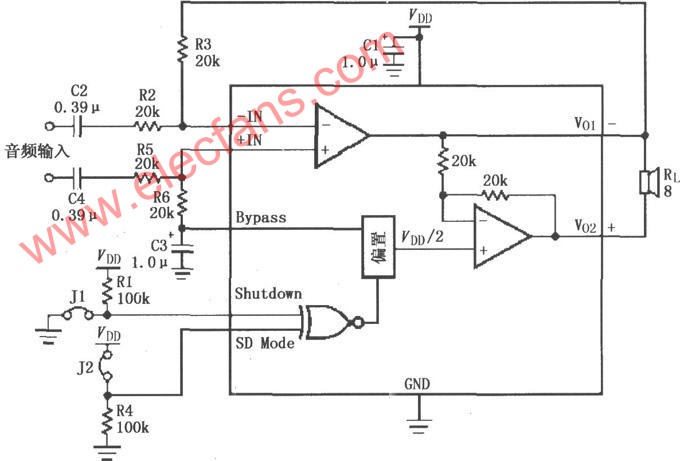

圖2 OP1177的DATASHEET截圖

圖2所示為在OP1177中出現的對CMRR函數對R1求偏導的結果,但我經過了數次推導之后,得到的結果如下:

δCMRR/δR1=-(R2*R3*R4+R2*R4*R4)/(R4R1-R2R3)2 ---------------(14)

式(14)是否成立????

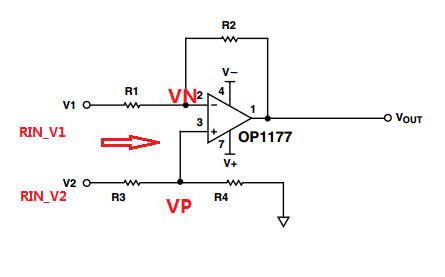

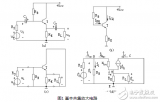

(3)差分放大電路的輸入電阻分析

圖3經典差分電路輸入電阻分析

同時假設以下條件成立:

(1)運放理想

(2)電阻匹配,設R1=R2=R3=R4=10KΩ

設RIN_V2、RIN_V1分別為電路中,從V2端和V1端看進去的輸入電阻。

如圖3所示,V2端的輸入電阻比較簡單,可以直接看出RIN_V2=R3+R4,由于運放的3端沒有電流進入,因此可以得到:

RIN_V2=R3+R4

=20KΩ------------------------------------------------------------------(15)

下面重點分析RIN_V1是如何得到的:

假設在V1端加入信號源V1,在V1的輸入端產生了電流I,則理論上來說,RIN_V1可以表示為:

RIN_V1=U/I---------------------------------------------------------------------(16)

從圖3中可以得到:

I=(U-VN)/R1---------------------------------------------------------------------(17)

而VN=VP=V2*R4/(R3+R4)-----------------------------------------------------(18)

由式(16)~(18)可以得到:

RIN_V1=V1*(R3+R4)*R1/(V1*R3+V1*R4-V2*R4)-------------------------(19)

代入式(8)~(9)并整理,得到:

RIN_V1=(2*K2-K1(R3+R4)*R1)/((2*K2-K1)(R3+R4)-(2*K2+K1)R4)----(20)

K1=V2-V1-------------------VCOM兩組輸入信號之間的差模信號

K2=(V2+V1)/2--------------VDEF表示兩組信號之間的共模信號

從式(20)可以看出,影響RIN_V1取值大小與電阻值、差模信號VDEF、共模信號VCOM的大小相關。

現考慮一種簡單的情況,設共模信號VOCM為零,即K2=0。

帶入式(20)中,可以得到:

RIN_V1=K1*(R3+R4)*R1/(K1(R3+R4)+K1R4)

=(R3+R4)*R1/(R3+2*R4)

=6.666KΩ---------------------------------------------------------------(21)

總結:

(1)由運放和分離電阻組成的差分電路的性能與運放、電阻匹配度等有關,在實際設計的時候需要考慮各方面因素。

(2)差分放大電路的兩個輸入端的輸入電阻值不一致,影響差分放大電路的性能。

正是由于經典差分放大電路的缺點,才有了性能更好的差分放大器、儀表放大器等出現。

電子發燒友App

電子發燒友App

評論