ad7656應(yīng)用電路圖一:外圍電路

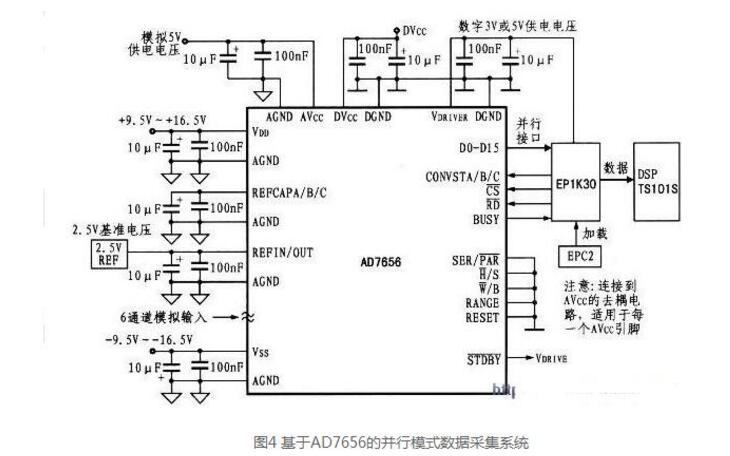

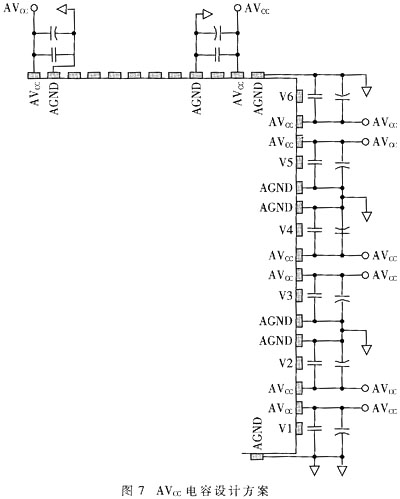

圖4所示是AD7656在并行接口狀態(tài)下的外圍電路連接。其中的DVcc和AVcc分別是數(shù)字電壓端和模擬電壓端,它們在接入前要經(jīng)過1個(gè)去耦電路,如圖4所示,每個(gè)供電電壓輸入引腳都要連接1個(gè)去耦電路,該電路由1只10μF和1只100nF的電容器組成。VDD、Vss和VDRIVE同樣要連接去耦電路。

AD7656的輸出接到FPGA中進(jìn)行數(shù)字信號的濾波處理,然后再送入數(shù)字信號處理器(DSP)進(jìn)行處理。用FPGA控制引腳CONVSTA/B/C、 RD和CS的狀態(tài),可以用編程的方法或硬件連接的方式來實(shí)現(xiàn)。系統(tǒng)中的FPGA是ALTERA公司的EP1K30,DSP選用ADI公司的TS101S。此系統(tǒng)的外圍電路比較簡單,比較容易實(shí)現(xiàn),具有真正的高速、高性能數(shù)字信號采集功能。

ad7656應(yīng)用電路圖二:電能質(zhì)量監(jiān)測

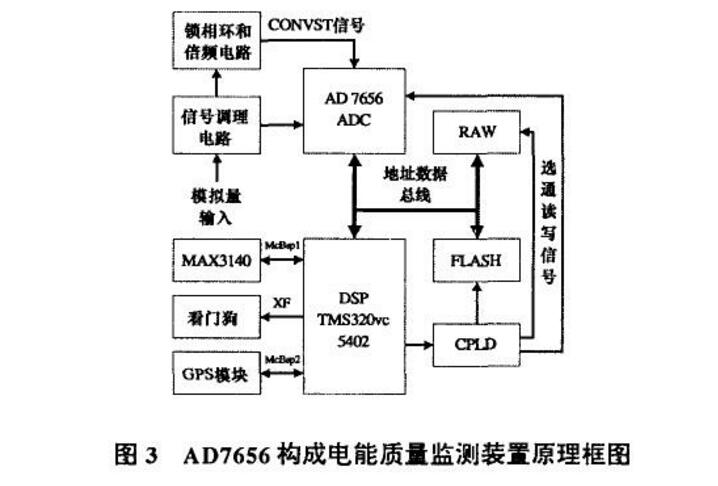

電能質(zhì)量測控系統(tǒng)采用16位高功能、低功耗的DSP芯片TMS320vc5402作為CPU,具有先進(jìn)的多總線結(jié)構(gòu),40位AIU,數(shù)據(jù)/程序?qū)ぶ房臻g1M*16bit,內(nèi)置4K*16bitP/DROM和16K*16bitDARAM,工作頻率可達(dá)到IOOMIPS。該處理器是整個(gè)監(jiān)測系統(tǒng)的控制核心,主要完成系統(tǒng)的通訊接口,負(fù)責(zé)系統(tǒng)中各個(gè)電路的協(xié)調(diào)管理以及計(jì)算結(jié)果的預(yù)處理。其特點(diǎn)是任務(wù)多,各個(gè)任務(wù)之間的協(xié)調(diào)較為復(fù)雜。DSP芯片接收數(shù)據(jù)采集系統(tǒng)送來的數(shù)字信號,并對其進(jìn)行分析和計(jì)算,以實(shí)現(xiàn)各種算法,完成電壓、電流、功率、功率因數(shù)、頻率及各項(xiàng)電能指標(biāo)的計(jì)算和分析。同時(shí)通過開關(guān)量輸入輸出通道實(shí)現(xiàn)各種控制模式。系統(tǒng)擴(kuò)展高精度CPID實(shí)現(xiàn)對外圍各種設(shè)備的控制;擴(kuò)展1片AM28F010作為外部程序存儲器和數(shù)據(jù)存儲器;與上位機(jī)通訊采用RS一485協(xié)議,為此內(nèi)部集成一個(gè)通用的UART和全功能收發(fā)器MAX3140。

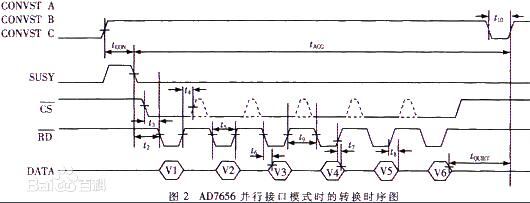

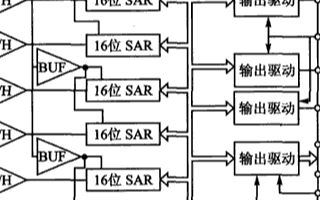

電能質(zhì)量監(jiān)測需要對電壓、電流、有功功率、無功功率、頻率等基本參數(shù)進(jìn)行實(shí)時(shí)監(jiān)測,并對電力系統(tǒng)的諧波、三相電壓不平衡度、電壓閃變等指標(biāo)進(jìn)行分析。為了保證實(shí)時(shí)性,系統(tǒng)采用2片高速6通道同時(shí)轉(zhuǎn)換的A/D轉(zhuǎn)換器AD7656,同步采集三相電壓信號和電流信號,簡化了系統(tǒng)的硬件設(shè)計(jì)和軟件程序設(shè)計(jì),為DSP及時(shí)準(zhǔn)確地完成繁多的系統(tǒng)任務(wù)和復(fù)雜的算法奠定了基礎(chǔ)。A/D轉(zhuǎn)換模塊中,A/D采集要求DSP在接受到指示A/D轉(zhuǎn)換已完成的信號后從A/D中讀取轉(zhuǎn)換結(jié)果,因此需要建立兩個(gè)硬件中斷,一個(gè)是A/D中斷請求,BUSY引腳變低指示所有轉(zhuǎn)換已完成,通知DSP可從片內(nèi)的寄存器讀轉(zhuǎn)換結(jié)果;另一個(gè)是DSP接收A/D數(shù)據(jù)中斷,如CS和RD低脈沖即為DSP從AD7656中讀轉(zhuǎn)換結(jié)果,在RD的上升沿將數(shù)據(jù)讀入DSP,建立兩個(gè)與硬件中斷相對應(yīng)的軟件中斷SWI,建立配置A/D屬性的任務(wù)。系統(tǒng)的硬件結(jié)構(gòu)框圖如圖3。

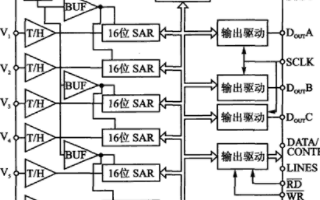

ad7656應(yīng)用電路圖三:級聯(lián)電路

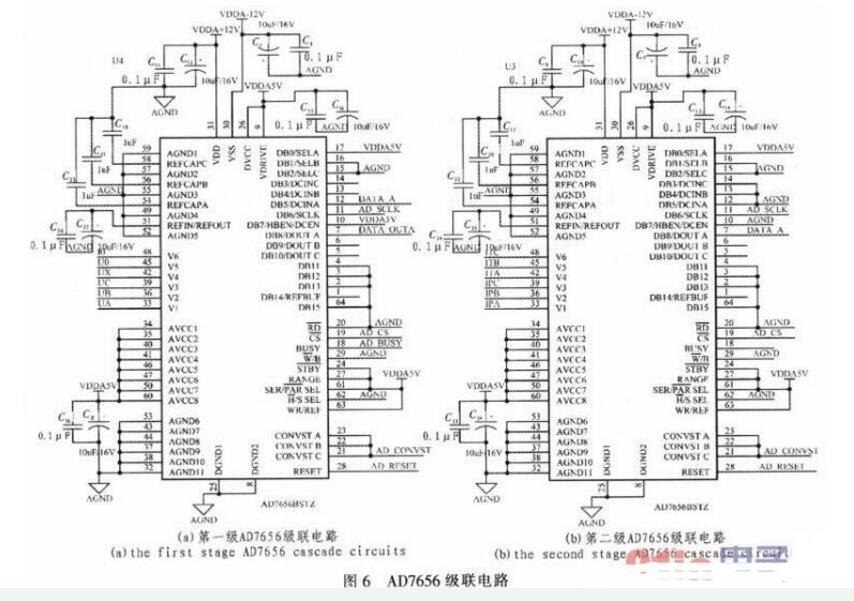

如圖6所示為AD7656級聯(lián)電路圖,鎖相環(huán)的輸出信號PLL-CONVST控制兩塊AD7656的21、22、23管腳,同時(shí)啟動12路采集;CPU作為主機(jī)為AD7656的11管腳(AD—SCLK)提供時(shí)鐘信號。CPU從圖6(a)的管腳7(DATA—OUTA)通過SPI讀取數(shù)據(jù);圖6(a)的12管腳與圖6(b)的管腳7連接,實(shí)現(xiàn)兩塊AD7656的級聯(lián);通過判斷AD7656的18管腳(AD—BUSY)來提醒CPU讀取轉(zhuǎn)換數(shù)據(jù)。

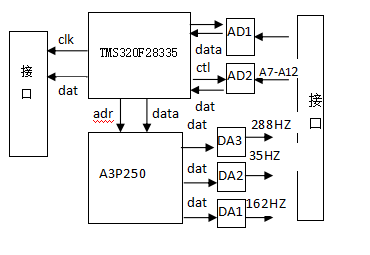

ad7656應(yīng)用電路圖四:菊花鏈電路

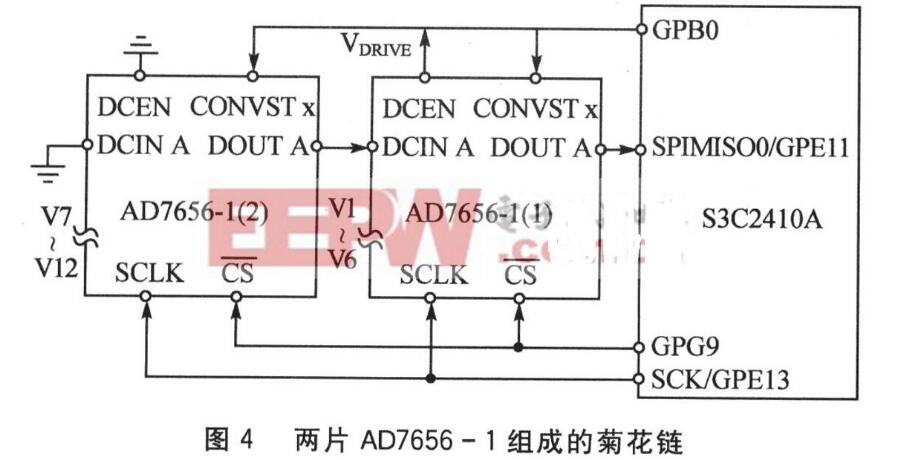

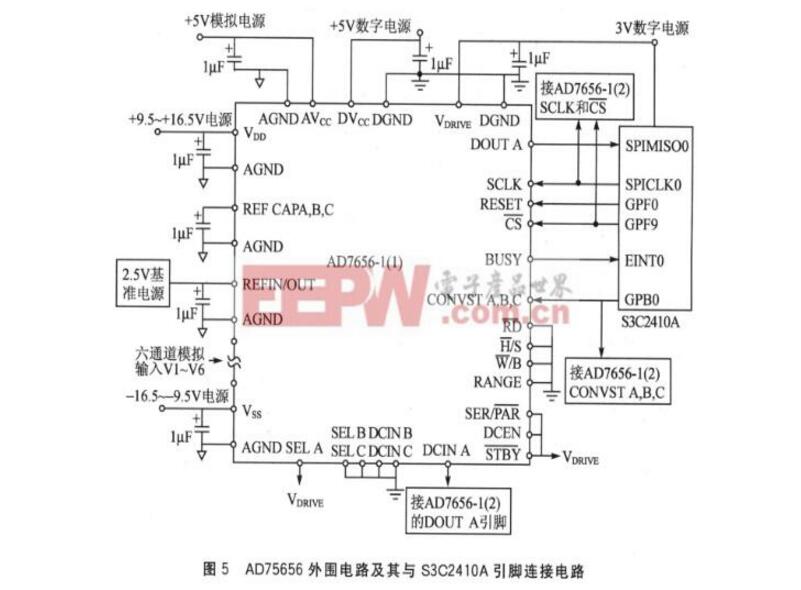

采用2片AD7656-1配置成菊花鏈,可實(shí)現(xiàn)12通道同時(shí)采樣,數(shù)據(jù)通過DOUTA[]輸出,S3C2410A用同步串行接[10(SPIO)接收數(shù)據(jù),如圖4所示。S3C2410A的GPEII弓|腳實(shí)現(xiàn)片上同步串行接[1SPIO的MISO功能,GPEI3(SCK)3|腳實(shí)現(xiàn)SPIO接C的同步時(shí)鐘輸出,GPFO弓|腳配置為中斷EINTO輸入并與AD7656-1(1)的BUSY腳相連;GPBO設(shè)置為PWM輸出,GPG9弓|腳沒置為通用輸出口,分別作為AD7656-1(1)和AD7656-1(2)的CONVST和CS的控制信號輸入。AD7656-1連接外圍電路時(shí),必須對關(guān)鍵弓|腳進(jìn)行必要的設(shè)置:AD7656-1(1)、AD7656-1(2)的DVCC、AVCC、VDRIVE、REFIN/OUT和VSS|腳須并聯(lián)一個(gè)1uF的去耦電容;為了與S3C2410A的3.3V的接[匹配,VDRIVE接+3V電源;STBY接VDRIVE,選擇正常模式;RANGE接地表示選擇輸入范圍士10V;H/s接數(shù)字地選擇為硬件配置;SER/PAR接VDRIVE,RD接數(shù)字地,選擇為串行模式。AD7656-1(1)的DCEN接VDRIVE,配置為菊花鏈模式,且SELA接VDRIVE,SELB、C,DCINA、B、C接數(shù)字地;AD7656-1(2)的DCEN接數(shù)字地,配置為排菊花鏈模式,且SELA接VDRIVE,SELB、C,DCINB、C接數(shù)字地。具體配置如圖所示。

電子發(fā)燒友App

電子發(fā)燒友App

評論