74LS138應當如何和與非門電路設計三人表決器呢?本文將為你詳細介紹基于74LS138下的三人表決器設計過程。

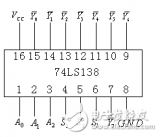

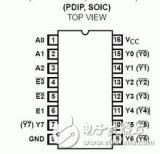

74LS138

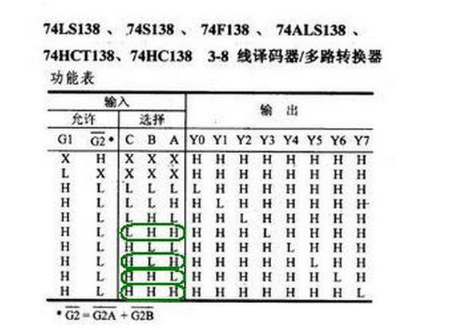

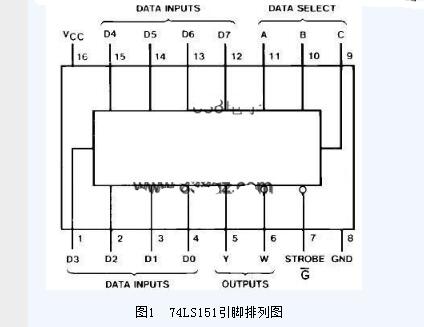

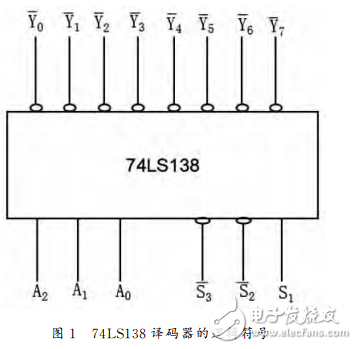

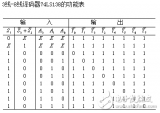

74LS138 為3 線-8線譯碼器,共有 54LS138和 74LS138 兩種線路結構型式。54LS138為軍用,74LS138為民用。

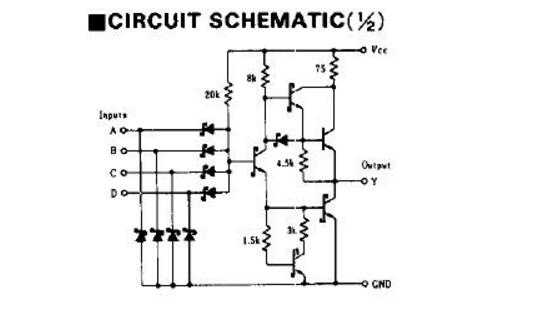

74LS138工作原理

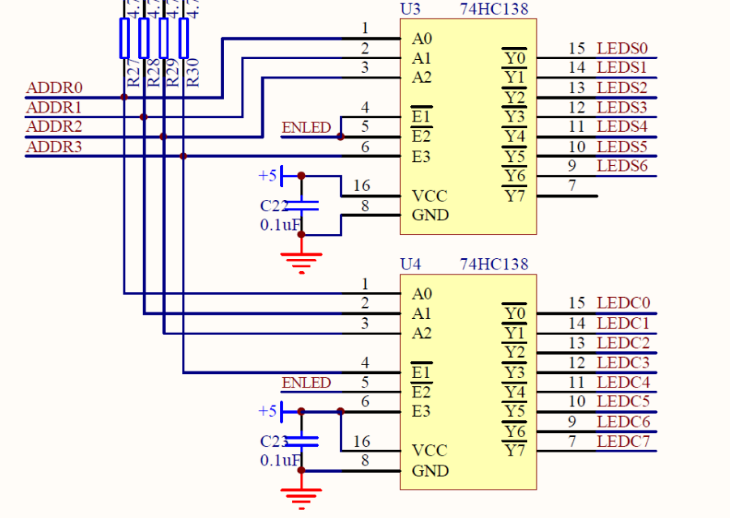

①當一個選通端(E1)為高電平,另兩個選通端((/E2))和(/E3))為低電平時,可將地址端(A0、A1、A2)的二進制編碼在Y0至Y7對應的輸出端以低電平譯出。(即輸出為Y0至Y7的非)比如:A2A1A0=110時,則Y6輸出端輸出低電平信號。

②利用 E1、E2和E3可級聯擴展成 24 線譯碼器;若外接一個反相器還可級聯擴展成 32 線譯碼器。

③若將選通端中的一個作為數據輸入端時,74LS138還可作數據分配器。

④可用在8086的譯碼電路中,擴展內存。

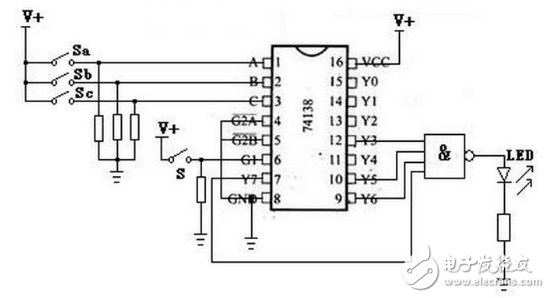

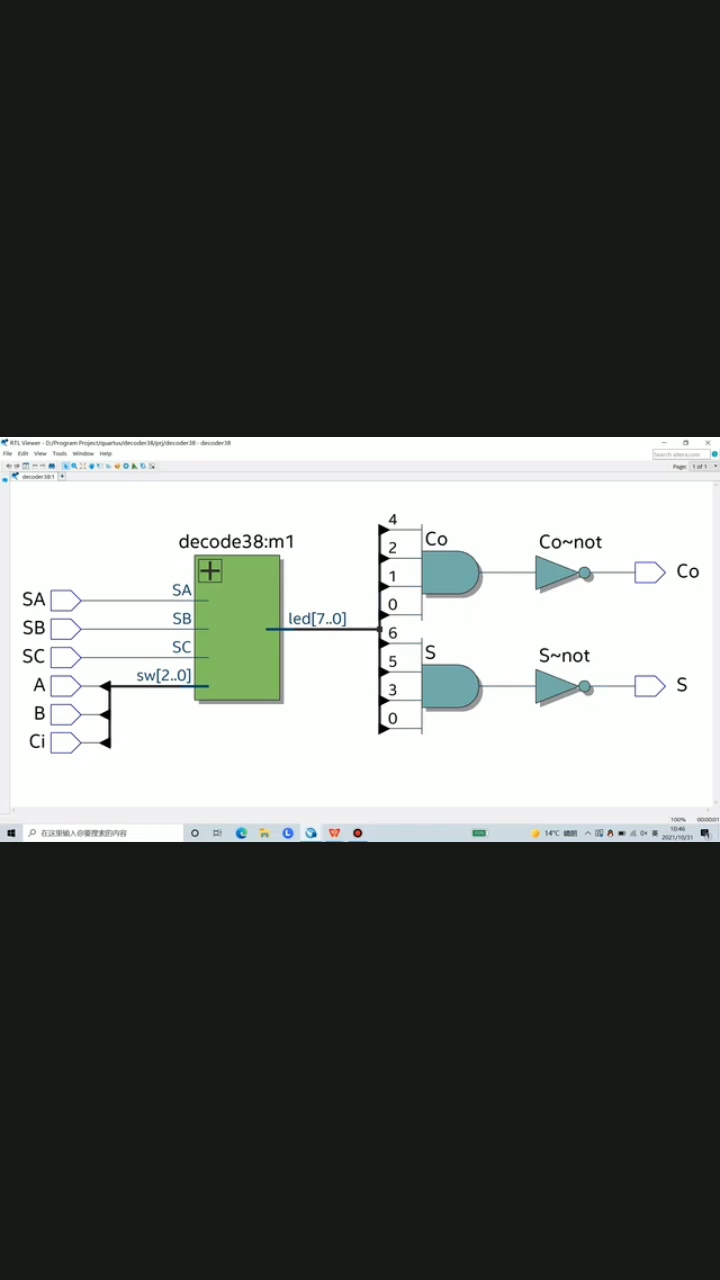

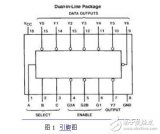

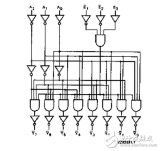

74LS138和與非門設計三人表決器

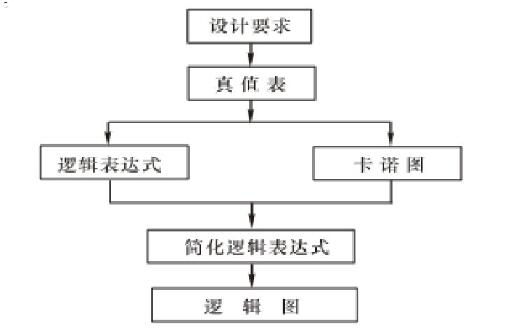

設Sa,Sb,Sc為三裁判按鍵,按下=1通過,S為開始鍵,

真值表中綠色圈為通過組合,通過後LED亮。

74LS138和與非門設計三人表決器工作原理

首先得弄清楚全加器的原理,你這里說的應該是設計1位的全加器。

全加器有3個輸入端:a,b,ci;有2個輸出端:s,co.

與3-8譯碼器比較,3-8譯碼器有3個數據輸入端:A,B,C;3個使能端;8個輸出端,OUT(0-7)。

這里可以把3-8譯碼器的3個數據輸入端當做全加器的3個輸入端,即3-8譯碼器的輸入A、B、C分別對應全加器的輸入a,b,ci;將3-8譯碼器的3個使能端都置為有效電平,保持正常工作;這里關鍵的就是處理3-8譯碼的8個輸出端與全加器的2個輸出的關系。

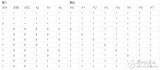

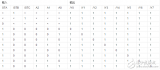

現在寫出全加器和3-8譯碼器的綜合真值表:

(A/a,B/b,C/ci為全加器和譯碼器的輸入,OUT為譯碼器的輸出(0-7),s為加法器的和,co為加法器的進位輸出)PS:假定譯碼器的輸出為高電平有效。

A/a B/b C/ci OUT s co

0 0 0 0 0 0

0 0 1 1 1 0

0 1 0 2 1 0

0 1 1 3 0 1

1 0 0 4 1 0

1 0 1 5 0 1

1 1 0 6 0 1

1 1 1 7 1 1

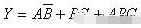

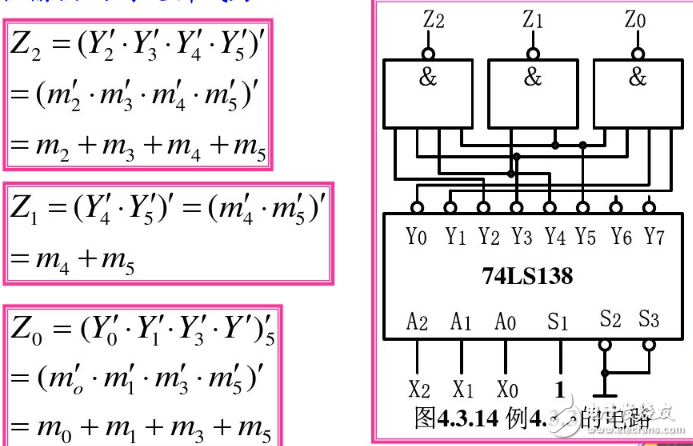

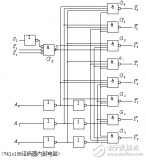

根據上面的真值表,可以設計出電路圖:

將3-8譯碼器的輸出OUT(1、2、4、7)作為一個4輸入的或門的輸入,或門的輸出作為加法器的和;將3-8譯碼器的輸出OUT(3、5、6、7)作為一個4輸入的或門的輸入,或門的輸出作為加法器的進位輸出。即完成了加法器的設計。

回過頭來分析:

當加法器的輸入分別為:a=1,b=0,ci=1時,對應3-8譯碼器的輸入為A=1,B=0,C=1,這是譯碼器對應的輸出為OUT(5)=1,其余的為0,根據上面設計的連接關系,s=0,co=1,滿足全加器的功能,舉其他的例子也一樣,所以,設計全加器的設計正確。

結語

在三人表決器的設計中,如果數字系統簡單,可以采用門電路;如果數字系統復雜,則可以采用譯碼器、數據選擇器和加法器比較好。關于74LS138和與非門設計三人表決器的介紹就到這里了,希望本文能夠幫到你。

電子發燒友App

電子發燒友App

評論