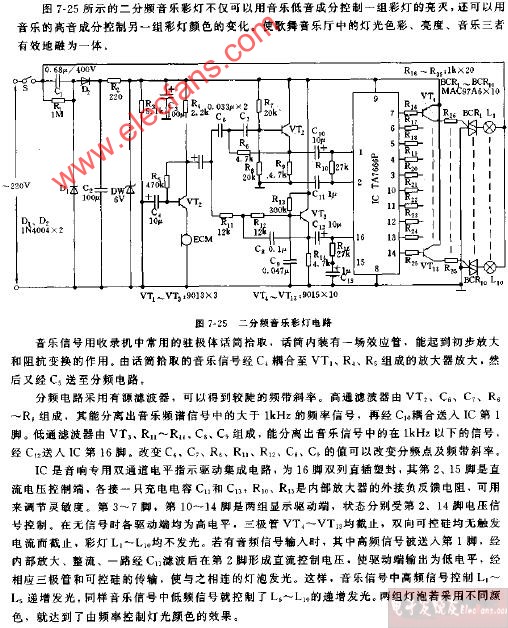

分頻電路的分頻方式

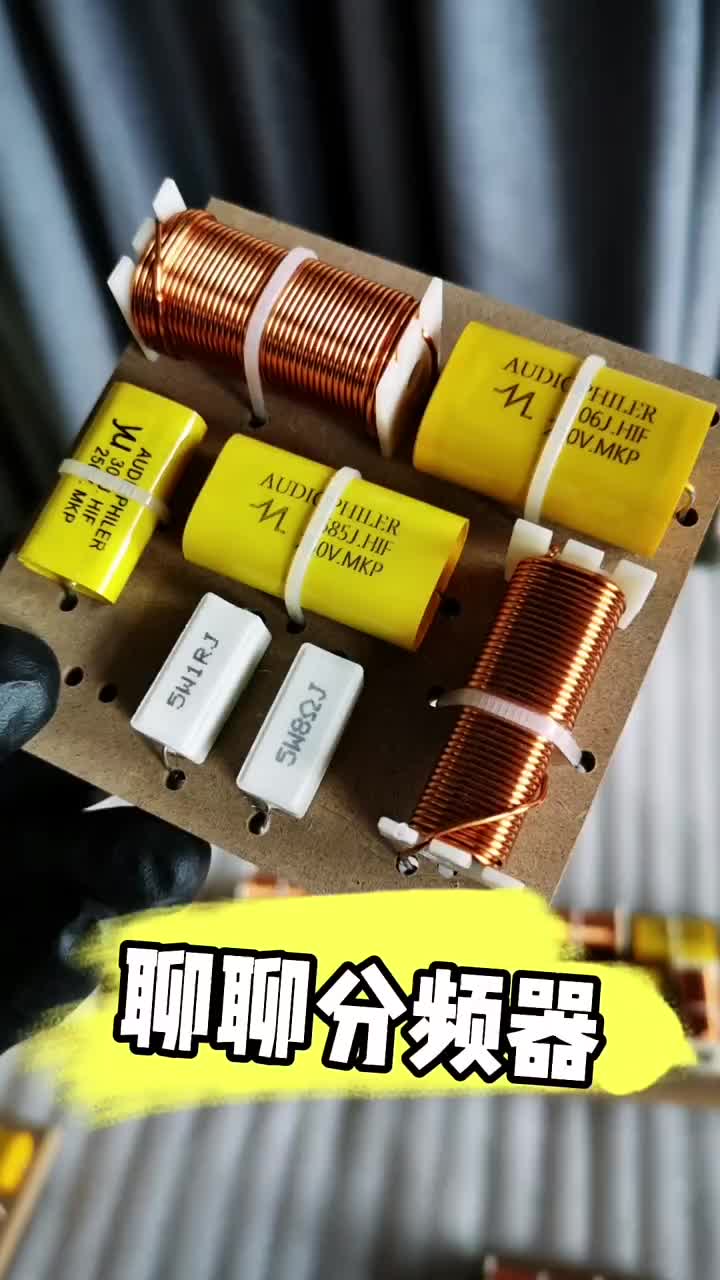

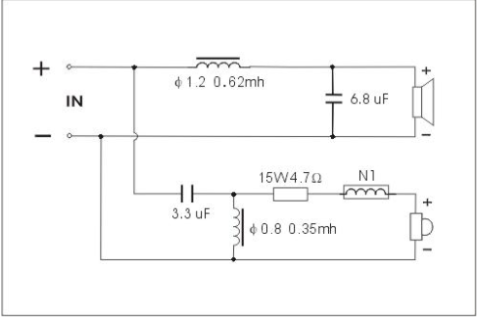

構成簡單的分頻電路人可以聽到的聲音的頻率范 圍是在20Hz—20kHz之間,祈望僅使用一只揚聲器就能夠保證放送20Hz—20kHz這樣寬頻率的聲音是很難做到的,因為這會在技術上存在各種各樣 的問題和困難。所以,在通常情況下,高質量的放音系統為了保證再現聲音的頻率響應和頻帶寬度,在專業范疇內大都采用高低音分離式音箱放音。而采用高低音分 離式音箱放送聲音時,就必然要對聲音按頻段分離,將聲音按頻率分段的個數就是聲音分頻數。

聲音的分頻主要是受揚聲器的控制,因為絕大多數揚聲器都有自己最適合的頻率范圍,真正的高質量全頻揚聲器非常少見并且價格極端昂貴。同時為了克服不同頻率聲音揚聲器引起的切割失真和減少同一音箱中的不同揚聲器之間產生的聲音干涉現象,必須對聲音進行分頻,將不同頻段的聲音送入不同的揚聲器。

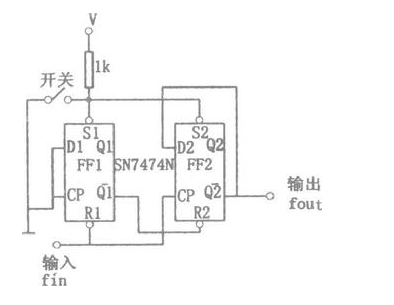

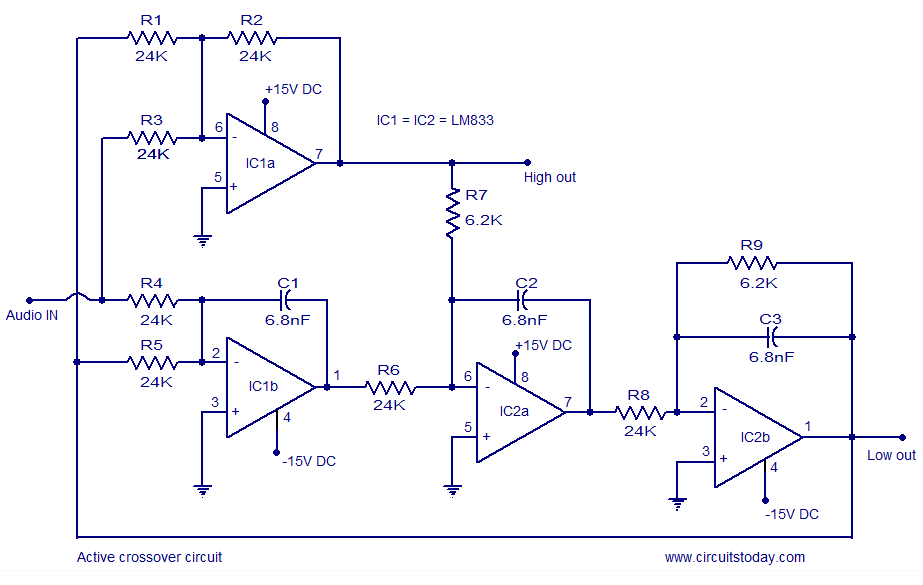

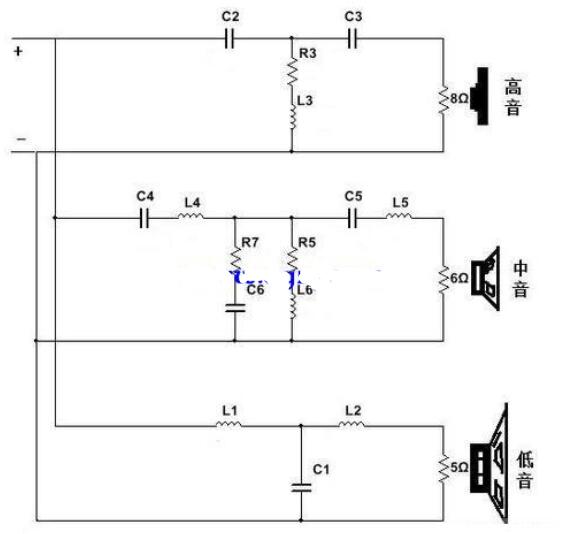

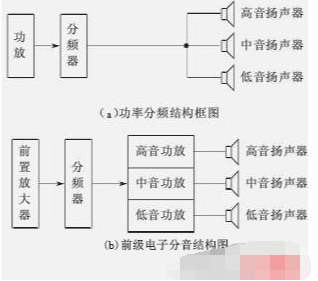

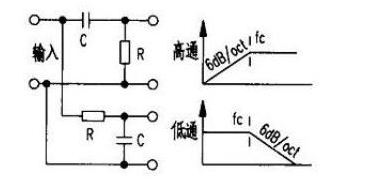

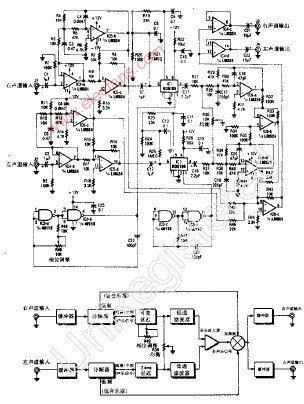

從分頻方式看可以分為兩種,一種是主動分頻(PassiveCrossover),或者叫電子分頻,也可以叫外置分頻、有源分頻;另一種是被動分頻 (ActiveCrossover),或者叫功率分頻,也可以叫內置分頻、無源分頻。主動分頻是指分頻器不在音箱內部,而在功率放大之前,由于此時聲音信 號很弱,因此容易將聲音徹底分頻,缺點是相應的電子線路分頻點較為固定,不容易和不同揚聲器配合,常見于高端和專業音響,隨著多路功放的普及,主動分頻方 式比以前普及很多。被動分頻是指分頻器在音箱內,此時聲音信號已經經過放大,分頻電路會造成一定干擾,但音箱可以適用于不同功放。

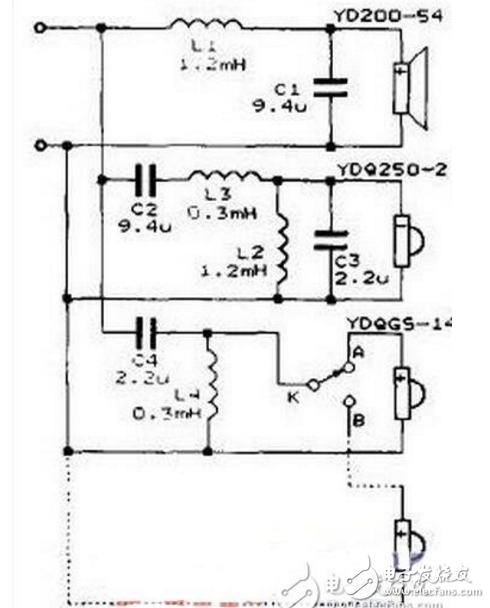

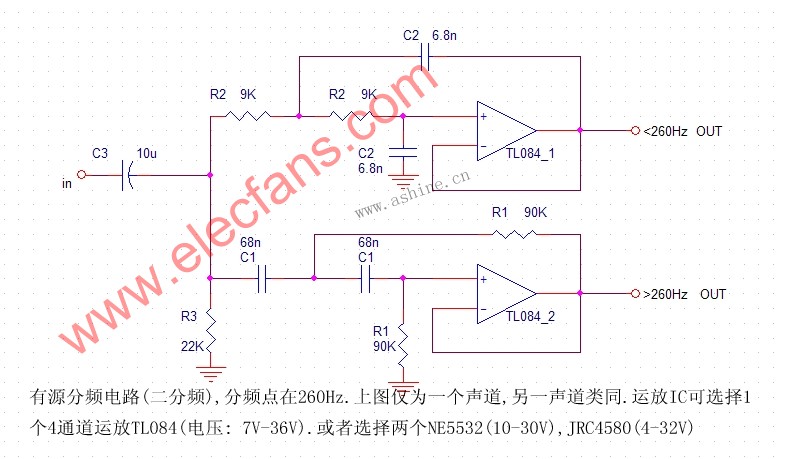

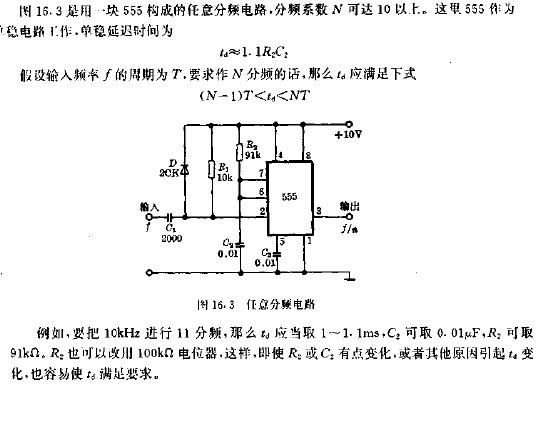

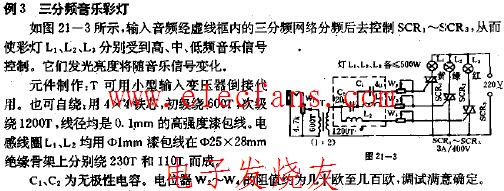

最簡單的分頻就是二分頻,將聲音分為高頻和低頻,分頻點需要高于低音喇叭上限頻率的1/2,低于高音喇叭下限頻率的2倍,一般的分頻點在2K到5K之間。但是這樣分頻對低音照顧仍然不夠完善,因為低音為 了獲得更好效果,往往需要單獨處理,并且揚聲器的切割失真對低音的影響也最大,因此近些年三分頻逐漸流行起來。三分頻是將聲音分為低音、中音和高音,有兩 個分頻點,低音分頻點一般在200Hz以下,或者120Hz,甚至更低,高音分頻點一般為2Hz-6KHz。此外也有少量的四分頻或者多分頻系統。顯然更 多分頻數理論上更有利于聲音的還原,但過多的分頻點會造成整體成本上升,并且實際效果提升有限,因此常見的分頻數仍然是二分頻和三分頻。

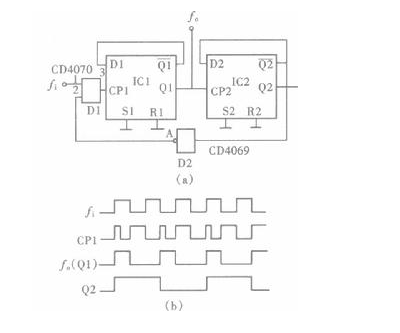

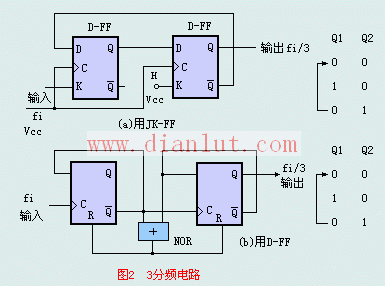

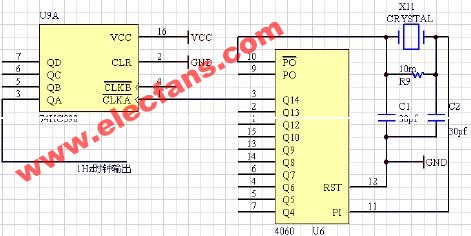

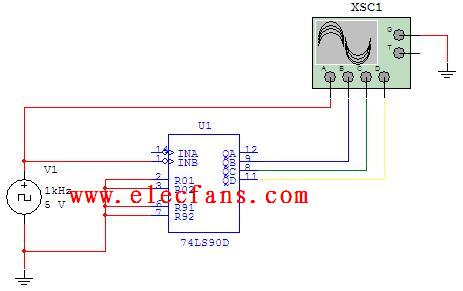

2N分頻電路的實現方法

1 目的

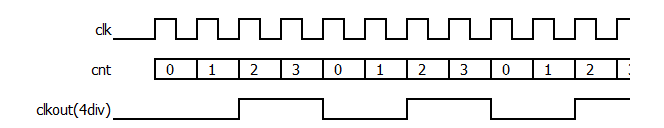

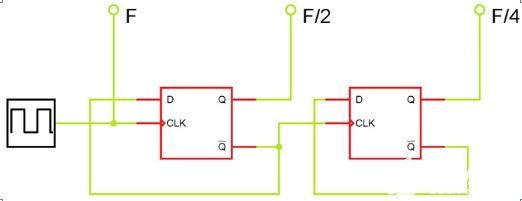

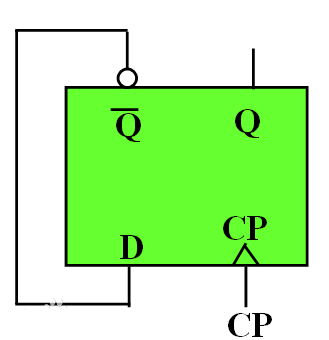

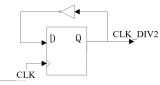

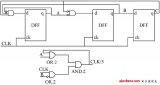

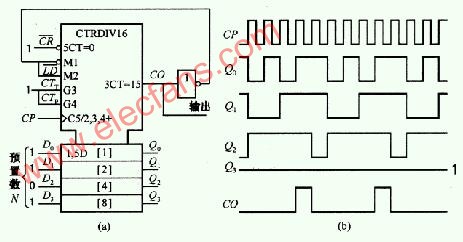

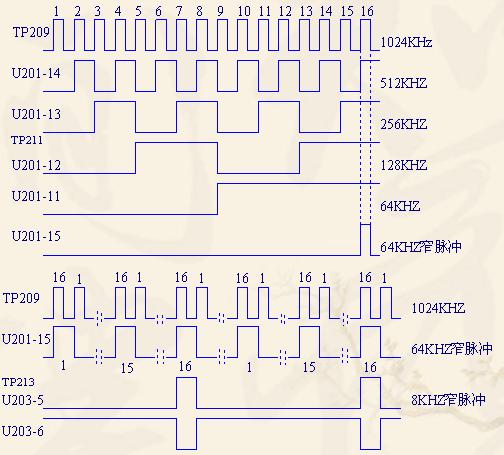

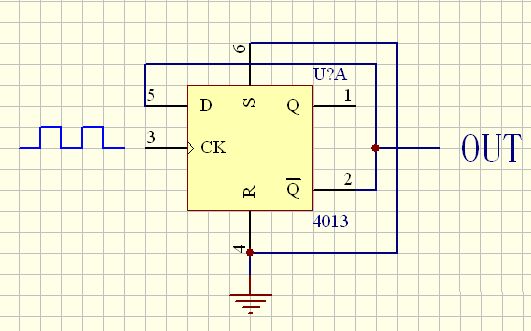

分頻系數較大的2N 分頻電路需要采用標準計數器來實現,此處的方法是直接將計數器的相應位賦給分頻電路的輸出信號即可實現分頻功能。采用這個方法的好處是:一是不需要定義中間信號,設計簡單,節約資源;二是可以避免毛刺現象的發生,從而避免了邏輯錯誤產生的可能性。

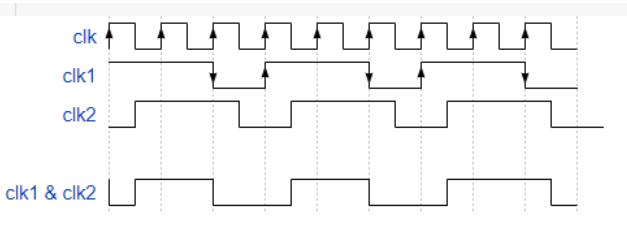

下面采用VHDL 和Verilog 兩種語言實現的2分頻、4分頻和8分頻。

2 VHDL實現(不帶復位信號)

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_arith.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY clk_8div_2 IS

PORT(CLK:IN std_logic;

CLK_DIV2:OUT std_logic;

CLK_DIV4:OUT std_logic;

CLK_DIV8:OUT std_logic);

END clk_8div_2;

ARCHITECTURE rtl OF clk_8div_2 IS

SIGNAL counter:std_logic_vector(2 DOWNTO 0);

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK’event AND CLK=’1’) THEN

IF (counter = “111”) THEN

count’0’);

ELSE

counter

END IF;

END PROCESS;

CLK_DIV2

CLK_DIV4

CLK_DIV8

END rtl;

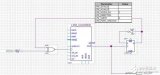

3 Verilog實現(有復位信號)

3.1

module clk_8div_2(

input CLK,

output CLK_DIV2,

output CLK_DIV4,

output CLK_DIV8,

input RESET

);

reg [2:0] clk_counter;

always @ (posedge CLK or posedge RESET) begin

if (RESET)

begin clk_counter

end

begin clk_counter

assign CLK_DIV2 = clk_counter[0]; assign CLK_DIV4 = clk_counter[1]; assign CLK_DIV8 = clk_counter[2];

endmodule

3.2 測試文件

module test_clk;

// Inputs reg CLK; reg RESET; // Outputs wire CLK_DIV2; wire CLK_DIV4; wire CLK_DIV8; // Instantiate the Unit Under Test (UUT) clk_8div_2 uut ( .CLK(CLK),

); .CLK_DIV4(CLK_DIV4), .CLK_DIV8(CLK_DIV8), .RESET(RESET) initial begin // Initialize Inputs CLK = 0; RESET = 1; // Wait 100 ns for global reset to finish #100;

RESET = 0;

end

always #10 CLK

電子發燒友App

電子發燒友App

評論