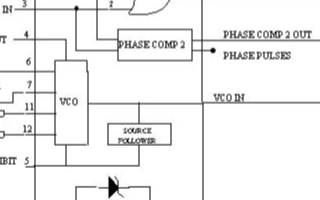

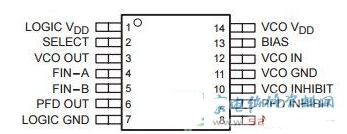

74HC046/74HCT4046A- -帶壓控振蕩器(VCO)的鎖相環電路概述:74HC/HCT4046A 是高速硅門CMOS 器件,與“4000B”系列的“4046”引腳兼容,并且符合JEDEC

2008-10-10 17:31:41

鎖相環是如何實現倍頻的?? 鎖相環(Phase Locked Loop, PLL)是一種電路,用于穩定和恢復輸入信號的相位和頻率。它可以廣泛應用于通信、計算機、音頻等領域中。其中一個重要的應用就是

2023-09-02 14:59:37 386

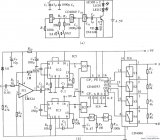

386 硬件鎖相環電路怎么設計?硬件鎖相環電路的設計通常包括以下步驟。

2023-08-08 11:16:46 223

223 鎖相環電路,是調頻電路的重要組成之一,鎖相環電路的原理的認識是DDS學習的一個重點之一。

2023-07-24 15:37:05 791

791

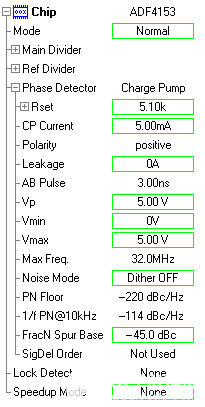

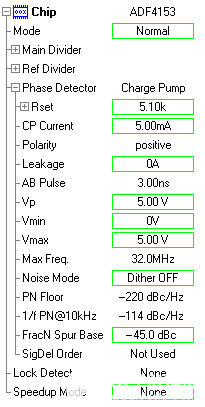

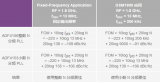

許多工程師對如何選擇參考頻率感到困惑,但參考頻率和輸出頻率階躍之間的關系很簡單。對于整數N分頻PLL,輸出頻率階躍等于鑒頻鑒相器(PFD)輸入端的頻率,即參考頻率除以參考分頻器R。對于小數N分頻PLL,輸出頻率階躍等于PFD輸入頻率除以MOD值,因此您可以使用較高的參考頻率來獲得較小的頻率步進。在決定是使用整數N還是小數N分頻時,頻率階躍可以用相位噪聲換取,PFD頻率越低,輸出頻率分辨率越好,但相位噪聲越差。

2023-01-30 15:25:32 739

739

鎖相環 (PLL) 電路存在于各種高頻應用中,從簡單的時鐘清理電路到用于高性能無線電通信鏈路的本振 (LO),再到矢量網絡分析儀 (VNA) 中的超快速開關頻率合成器。本文解釋了鎖相環電路的一些構建模塊,并參考了每種應用,以幫助指導新手和鎖相環專家導航器件選擇以及每種不同應用固有的權衡取舍。

2022-12-23 14:03:54 2293

2293

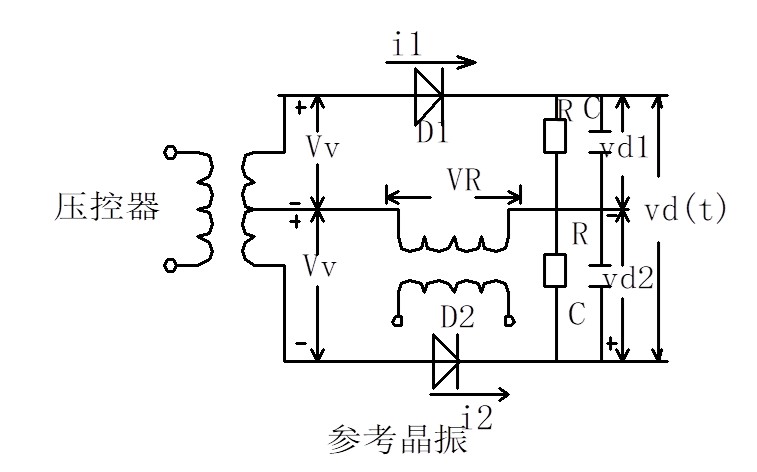

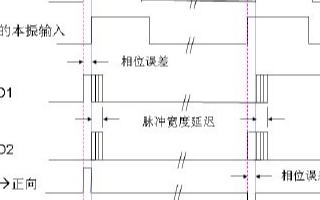

鑒相器是鎖相環路的關鍵部件。在頻率合成器中所采用的鑒相器主要有正弦波相位檢波器與脈沖取樣保持相位比較器兩種。

2022-11-11 16:56:47 2674

2674

晶振通常配合和鎖相環電路配合使用,以提供系統所需要的時鐘頻率,如果不同子系統需要不同頻率的時鐘信號,可以用與同一個晶振相連的不同鎖相環來提供。

2022-08-06 15:40:22 1222

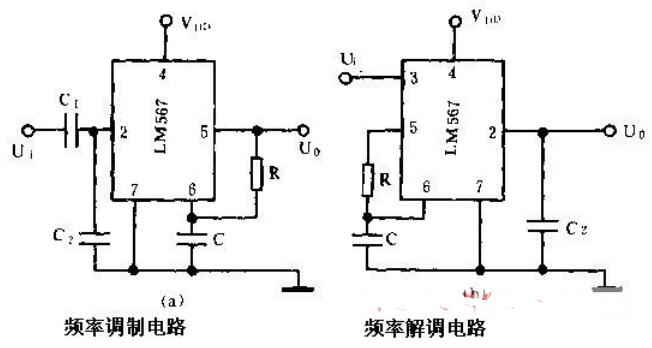

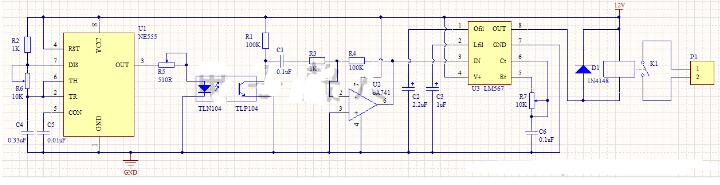

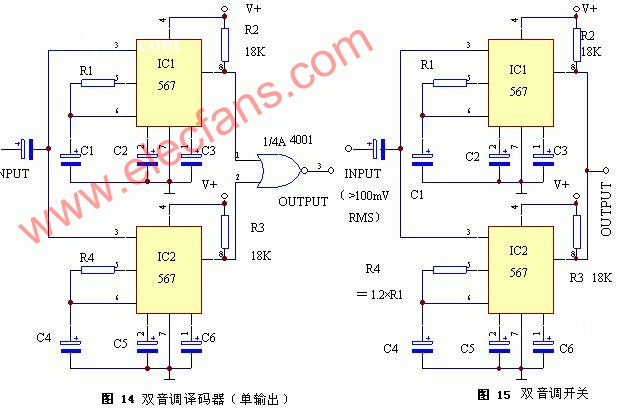

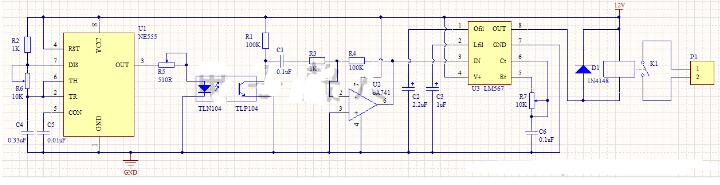

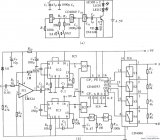

1222 LM567為通用鎖相環電路音調譯碼器,本電路是用LM567組成的調制電路和解調電路。

2021-05-01 16:47:00 3930

3930

有一些網友學不好LM567的鎖相環電路(主要是指我自己),主要是總是跑頻,下面是一個網友發給我的電路,我感覺非常的好,就發上來分享了。

2021-04-05 17:35:00 1609

1609

,已經成為電子設備中常用的基本部件之一。為了便于調整,降低成本和提高可靠性,目前已有多種不同性能的集成鎖相環電路,主要分為模擬和數字兩種。

2021-03-31 11:59:11 3409

3409

如果沒有深入了解 PLL 理論以及邏輯開發過程,可能你在設計并調試鎖相環(PLL)電路時會感到非常棘手。那有沒有比較容易理解或學習妙招呢?小A今日就為大家送上一份妙計錦囊,并提供有效、符合邏輯的方法

2021-02-24 07:35:28 15

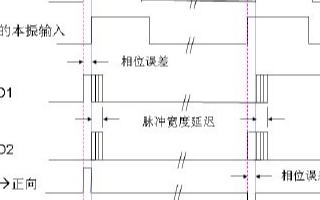

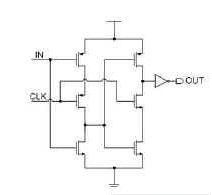

15 電荷泵鎖相環的鎖定檢測電路設計,包括模擬鎖定檢測和數字鎖定檢測兩種方法。其中,模擬檢測電路采用經鑒頻鑒相器PFD 輸出的相位誤差,產生脈沖信號對外部電容進行充電和放電,需要較長的時間以達到穩定的電平

2020-08-24 14:11:38 2743

2743

的相位變換,提出了一種基于鎖相環(PLL)的QPSK調制器。由于采用了三輸入異或門和求和電路,該系統中的鎖相環電路不同于傳統的鎖相環電路。利用這些附加組件,所提出的PLL在QPSK信號中提供連續的相位變化。因此,當使用所述電路時,傳輸QPSK信號所需的帶寬

2020-05-15 08:00:00 3

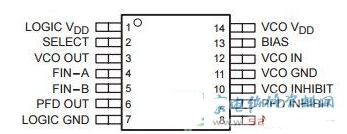

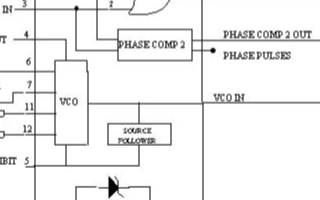

3 TLC2932是德州儀器公司出品的一款鎖相環電路(PLL)芯片,它由壓控振蕩器和以沿觸發方式工作的鑒相器(PFD:phflsefrequencydeteclor)組成。

2020-03-30 15:52:23 2674

2674

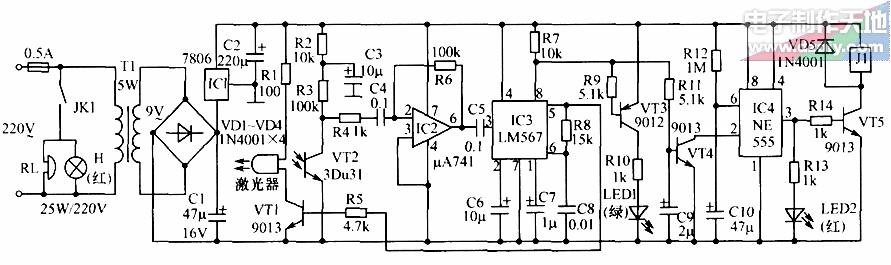

本例電路利用555芯片,LM567通用鎖相環電路音調譯碼器芯片和紅外發射接收管組成的紅外開關控制電路,可用于自動水龍頭的控制。

2019-10-01 15:00:00 5875

5875

如果不在特定條件下進行仿真,則估計一個 PLL 電路的規格將會是十分困難的。因此,進行 PLL 設計的第一步應當是仿真。建議工程師使用ADIsimPLL 軟件運行基于系統要求的仿真,包括參考頻率、步進頻率、相位噪聲(抖動)和頻率雜散限制。

2019-07-24 11:09:04 2630

2630

鎖相環(PLL)是模擬電路中的一個重要模塊,本文研究的是廣泛使用的電荷泵型鎖相環(CPPLL)。鎖相環電路通過比較參考輸入和輸出反饋信號的頻率/相位,并將此特征轉化為電壓,然后通過與壓控振蕩器

2019-06-14 08:03:00 2892

2892

如果不在特定條件下進行仿真,則估計一個 PLL 電路的規格將會是十分困難的。因此,進行 PLL 設計的第一步應當是仿真。

2019-05-08 17:47:19 5071

5071

一。 試驗要求:1. 用systemview設計并仿真一個完整的數字鎖相環電路。2. 試驗條件設定

信號速率 10Hz

系統采樣時鐘設定:100Hz

2019-01-29 11:15:08 69

69 如圖所示為大范圍激光防盜報警器電路。電路的核心是以IC3(LM567)及其外圍阻容元件構成的鎖相環電路。

2019-01-26 07:28:00 3889

3889

鎖相環電路當用作選頻時,它的選頻頻率主要由6、7腳間外接的電容值和11腳外接電阻值決定,只要選定了這幾個元件的參數,鎖相環的壓控振蕩器的中心頻率即被確定,鎖相環的選頻頻率也就被確定。

2018-05-04 10:04:00 1835

1835

本文實現了一種全集成可變帶寬中頻寬帶低通濾波器,討論分析了跨導放大器-電容(OTA—C)連續時間型濾波器的結構、設計和具體實現,使用外部可編程電路對所設計濾波器帶寬進行控制,并利用ADS軟件進行

2017-12-12 07:15:02 2939

2939

本文設計了一種寬頻率范圍的CMOS鎖相環(PLL)電路,通過提高電荷泵電路的電流鏡鏡像精度和增加開關噪聲抵消電路,有效地改善了傳統電路中由于電流失配、電荷共享、時鐘饋通等導致的相位偏差問題。 設計了

2017-11-18 09:52:14 10

10 作為一種間接頻率合成方法,鎖相環應用非常廣泛,包括存儲器、微處理器、硬盤驅動電路、射頻和無線收發器等領域。集成電路的飛速發展使鎖相環電路能夠以較低的成本集成在芯片內部。片上集成鎖相環可以根據一個低頻

2017-11-07 10:33:22 6

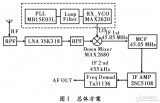

6 講解之前先講下鎖相環電路,由于調頻電路中很多地方用到鎖相環電路,因而這個基礎必須打堅實了。

2017-09-22 10:44:04 6

6 鎖相環是電路功能中最通用的。它們用于時鐘處理器(相當良性的情況),以及在固定和調諧頻率發射機和接收機建立調諧。

2017-05-16 10:42:41 8

8 結合了MEMS和高分辨率鎖相環電路的DCXO,能支持最小量化噪聲設計的高速數字鎖相環路和不受頻率牽引范圍影響的相位噪聲,適合于應用到各種射頻和通信系統中。

2017-04-27 10:35:59 2471

2471

電子芯片手冊,很好的資料,設計師必備資料。

2016-05-30 16:32:11 43

43 有關鎖相環的部分資料,對制作鎖相環有一定的幫助。

2015-10-29 14:16:55 62

62 2015-08-12 13:58:08 29

29 2015-08-10 18:14:16 9

9 2015-04-23 15:20:36 11

11 在傳統LC壓控振蕩器基礎上,通過采用二次諧波濾波技術降低了振蕩器的相位噪聲,并完成了電路的仿真。仿真結果表明,該壓控振蕩器的振蕩頻率在1.9~2.1 GHz,其頻率調節范圍達到

2012-01-13 15:28:55 159

159 鎖相環英文為PLL,即PLL鎖相環。可以分為模擬鎖相環和數字鎖相環。兩種分類的鎖相環原理有較大區別,通過不同的鎖相環電路實現不同的功能。

2011-10-26 12:40:28

頻率跟蹤的 鎖相環電路 由專用鎖相芯片CD4046和分頻芯片CD4040組成,以實現工頻信號的鎖相倍頻,分頻比為1/64。在工頻信號恰好為50 Hz的情況下,該電路的鎖相倍頻頻率為5064=3 200 Hz,相

2011-10-26 11:17:47 8375

8375

電荷泵鎖相環的鎖定指示電路設計,常用的方法是在PFD 電路中通過檢測經分頻后的參考輸入和本振反饋信 號的相位誤差來實現,當相位誤差超過某個鎖定檢測窗口時,鎖相環電路就上報失鎖告警。由于數字鎖定指示電路 設計簡單,易于被監控而被廣泛應用。在實際的

2011-03-16 10:20:51 58

58 本文涉及的鎖相環路是基于相位控制的時鐘恢復系統。目的是用鎖相環電路-PLL和DLL實現USB2.0收發器宏單遠UTM的時鐘恢復木塊。其中PLL環路構成的時鐘發生器獎外部晶振的12MHZ的正弦信號

2011-03-03 14:58:34 50

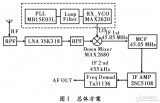

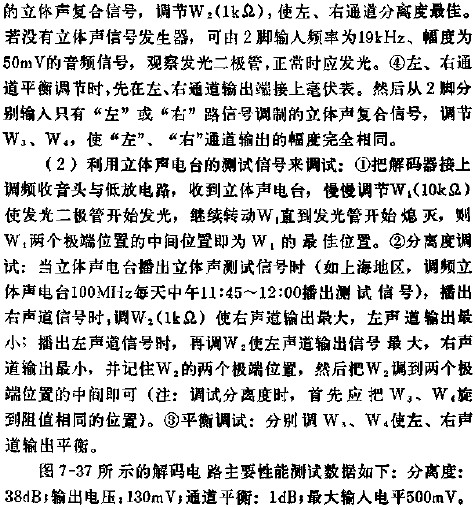

50 D3361調頻立體聲解碼電路,采用鎖相環方式解碼,它比D3301解碼電路多了一個鎖相環電路,因此性能較D3301優越.主要

2010-10-11 13:10:13 2022

2022

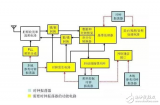

鎖相環的英文全稱是Phase-Locked Loop,簡稱PLL。它是由鑒相器(PD)、環路濾波器(LPF)和壓控振蕩器(VCO)三部分構成的一種信號相差自動調節反饋電路(環)。PLL電路框圖如下,其

2010-09-07 16:33:52 662

662 MC44802A是莫托洛拉采用MOSAIC工藝制成的調諧電路的鎖相環芯片。它和壓控振蕩器MC1648連接可組成調諧電路,其調諧頻率可由微控制器MC68HCllE9的串行接口控制。本文敘述用MC44802A組成的

2010-05-30 09:54:54 42

42 Signet ic畦}司生產的集成塊SE567/NE567,是具有同步調幅鎖定撿測和功率輸出性能的高穩定性鎖相環電路 它的主要功能是一旦輸入信號的額率在它檢測范周時能驅動負載 它的帶寬 中心

2010-04-26 10:44:09 69

69 LM567及NE567原理及應用

音頻解碼器567功能概述 本文討論鎖相環電路

2010-04-14 09:23:26 19131

19131

SC9256是一個數字調諧系統鎖相環電路,內置2個預分頻系數。SC9256的所有功能都是通過3根串行總線控制,適用于高性能的數字調諧系統。主要特點* 優化高保真調諧器

2010-02-25 09:23:56 47

47 SC9257是一個數字調諧系統鎖相環電路,內置2個預分頻系數。SC9257是一個用于數字調諧系統的PLL頻率合成器。適用于高性能的數字調諧系統,例如:收音機和隨身聽。它可

2010-02-25 09:20:12 38

38 本文討論鎖相環電路,介紹NE567單片音調解碼器集成電路。此音調解碼塊包含一個穩定的鎖相環路和一個晶體管開關,當在此集成塊的輸入端加上所先定的音頻時,即可產生一個接地

2009-11-23 15:03:42 22

22 時鐘和低功耗模式片內集成有PLL(鎖相環)電路。外接的基準晶體+PLL(鎖相環)電路共同組成系統時鐘電路。有關引腳:XTAL1/CLKIN:外接的基準晶體到片內振蕩器輸入引腳

2009-09-16 12:37:52 12

12 The CD4046BC micropower phase-locked loop (PLL) consistsof a low power, linear, voltage-controlled oscillator(VCO), a source follower, a zener diode, and two phasecomparators. The two phase comparators have a commonsigna

2009-08-08 10:00:01 132

132 鎖相環電路的設計:

2009-07-25 17:05:36 536

536 This application note is intended as a guide to designing a phaselocked loop based on the Philips UMA1014T frequency synthesizerintegrated circuit. The UMA1014T is a low power single chip solutionto frequency synthesis in the r

2009-06-30 10:53:58 45

45 本文主要設計了基于相位控制技術的時鐘恢復系統的PLL 鎖相環路。分別對各單元電路結構——鑒頻鑒相器、電荷泵、環路濾波器、壓控振蕩器、分頻器進行設計。采用2.5V,0.25μm

2009-06-01 15:51:53 53

53 本文提出了一種基于鎖相技術的組合式三相逆變器控制策略,詳細分析了鎖相技術的基本工作原理及鎖相控制策略,并給出了鎖相環電路的關鍵參數設計及實驗驗證。通過僅遠程采

2009-04-08 15:08:23 38

38

常用鎖相環電路集成電路

2006-06-30 19:20:57 606

606 BA1404對于一般的調頻發射已經夠了,但它卻有一個致命的缺點:沒有鎖相環電路,即PLL,容易跑頻!對

2006-04-15 20:46:26 5414

5414

電子發燒友App

電子發燒友App

硬聲App

硬聲App

386

386 739

739

2293

2293

1222

1222 1609

1609

3409

3409

15

15 2743

2743

3

3 2674

2674

5875

5875

2630

2630

2892

2892

69

69 1835

1835

2939

2939

10

10 6

6 8

8 2471

2471

29

29 9

9 11

11 159

159 8375

8375

58

58 50

50 2022

2022

662

662 42

42 69

69 47

47 38

38 22

22 12

12 132

132 45

45 53

53 38

38

評論