基于FPGA的鎖相環位同步提取電路

- fpga(588988)

- 鎖相環(86948)

相關推薦

鎖相環(PLL)基本原理 當鎖相環無法鎖定時該怎么處理的呢?

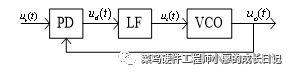

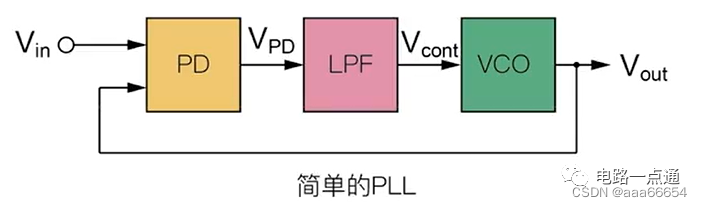

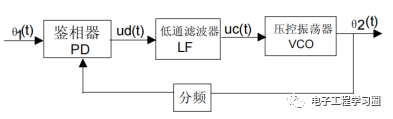

鎖相環(PLL)基本原理 當鎖相環無法鎖定時該怎么處理的呢? 鎖相環(Phase Locked Loop, PLL)是一種電路系統,它可以將輸入信號的相位鎖定到參考信號的相位。在鎖相環中,反饋回路

2023-10-23 10:10:15 47

47

47

47軟件鎖相環在頻率突變時鎖不住 鎖相環無法鎖定怎么辦?

軟件鎖相環在頻率突變時鎖不住 鎖相環無法鎖定怎么辦?? 鎖相環(PLL)是一種用于在電路中生成穩定頻率的技術。它是在1960年代開發的,并被廣泛應用于通信、雷達、衛星技術等領域中。鎖相環的主要作用

2023-10-13 17:39:58 97

97

97

97什么是鎖相環?PLL和DLL都是鎖相環區別在哪里?

比較,通過不斷調整內部振蕩器的頻率,使得輸出信號的相位與參考信號的相位保持一致,從而實現同步。鎖相環廣泛應用于數字通信、音頻解碼、數字信號處理等領域。 在鎖相環的基本結構中,包含一個相位檢測器、一個積分環節、一個低通濾波器和一個控制振蕩器。參考

2023-10-13 17:39:53 106

106

106

106pll鎖相環的作用 pll鎖相環的三種配置模式

pll鎖相環的作用 pll鎖相環的三種配置模式? PLL鎖相環是現代電子技術中廣泛應用的一種電路,它的作用是將一個特定頻率的輸入信號轉換為固定頻率的輸出信號。PLL鎖相環的三種配置模式分別為

2023-10-13 17:39:48 167

167

167

167數字鎖相環設計源程序

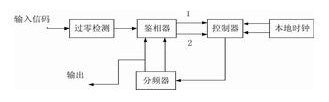

數字鎖相環設計源程序PLL是數字鎖相環設計源程序, 其中, Fi是輸入頻率(接收數據), Fo(Q5)是本地輸出頻率.目的是從輸入數據中提取時鐘信號(Q5), 其頻率與數據速率一致, 時鐘上升沿鎖定在數據的上升和下降沿上;頂層文件是PLL.GDF

2009-12-18 10:37:37

鎖相環是如何實現倍頻的?

鎖相環是如何實現倍頻的?? 鎖相環(Phase Locked Loop, PLL)是一種電路,用于穩定和恢復輸入信號的相位和頻率。它可以廣泛應用于通信、計算機、音頻等領域中。其中一個重要的應用就是

2023-09-02 14:59:37 386

386

386

386pll鎖相環倍頻的原理

以及各種時鐘信號,下面將從這些方面逐一介紹。 一、鎖相環 鎖相環(Phase-Locked Loop, PLL)是一種基于反饋控制的電路,由比較器、低通濾波器、振蕩器和除法器等組成。輸入信號和振蕩器產生的參考信號經過比較器比較,將誤差信號通過低通濾波器進

2023-09-02 14:59:24 444

444

444

444什么是鎖相環 鎖相環的組成 鎖相環選型原則有哪些呢?

大家都知道鎖相環很重要,它是基石,鎖相環決定了收發系統的基礎指標,那么如此重要的鎖相環選型原則有哪些呢?

2023-08-01 09:37:05 672

672

672

672

鎖相環設計與仿真的基本知識

鎖相環:在通信領域中,鎖相環是一種利用反饋控制原理實現的頻率及相位同步技術,其作用是將電路輸出的時鐘與其外部的參考時鐘保持同步。

2023-06-30 15:53:39 1199

1199

1199

1199

模擬鎖相環和數字鎖相環區別

模擬鎖相環和數字鎖相環的主要區別在于它們的控制方式不同。模擬鎖相環是通過模擬電路來控制頻率和相位,而數字鎖相環是通過數字信號處理技術來控制頻率和相位。此外,模擬鎖相環的精度較低,而數字鎖相環的精度較高。

2023-02-15 13:47:53 2765

2765

2765

2765鎖相環PLL的基礎知識

鎖相環 (PLL) 電路存在于各種高頻應用中,從簡單的時鐘清理電路到用于高性能無線電通信鏈路的本振 (LO),再到矢量網絡分析儀 (VNA) 中的超快速開關頻率合成器。本文解釋了鎖相環電路的一些構建模塊,并參考了每種應用,以幫助指導新手和鎖相環專家導航器件選擇以及每種不同應用固有的權衡取舍。

2022-12-23 14:03:54 2293

2293

2293

2293

鎖相環的基本組成和工作原理

因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。鎖相環在工作的過程中,當輸出信號的頻率與輸入信號的頻率相等時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環名稱的由來。

2022-05-10 14:25:19 6544

6544

6544

6544鎖相環(PLL)的工作原理及應用

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。

2022-03-29 09:54:55 10729

10729

10729

10729MCU鎖相環簡述(一)

)控制原理實現的頻率及相位的同步技術,其作用是將電路輸出的時鐘與其外部的參考時鐘保持同步。當參考時鐘的頻率或相位發生改變時,鎖相環會檢測到這種變化,并且通過其內部的反饋系統來調節輸出頻率,直到兩者

2021-11-01 16:24:35 12

12

12

12鎖相環CD4046原理及應用

鎖相的意義是相位同步的自動控制,能夠完成兩個電信號相位同步的自動控制閉環系統叫做鎖相環,簡稱PLL。它廣泛應用于廣播通信、頻率合成、自動控制及時鐘同步等技術領域。鎖相環主要由相位比較器(PC)、壓控振蕩器(VCO)、低通濾波器三部分組成。

2021-06-21 15:13:55 56

56

56

56如何使用FPGA實現高性能全數字鎖相環的設計

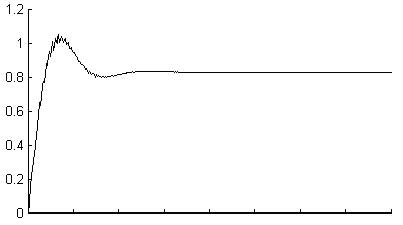

本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 65

65

65

65如何使用FPGA實現高性能全數字鎖相環的設計

本文提出了一種適用范圍廣泛的全數字鎖相環(ADPLL)實現方法.在鎖相環輸入頻率未知的情況下,實現鎖相鎖頻功能。本文從全數字鎖相環的基本實現方式入手.進行改進,并使用VH DL語言建模,使用FPGA進行驗證。

2021-01-26 15:03:00 18

18

18

18鎖相環的基本組成及工作原理

因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。鎖相環在工作的過程中,當輸出信號的頻率與輸入信號的頻率相等時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環名稱的由來。

2020-11-03 14:55:49 14026

14026

14026

14026

使用FPGA實現數字鎖相環的設計資料說明

鎖相環路是一種反饋控制電路,簡稱鎖相環( PLL)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤, 所以鎖相環通常

2020-08-06 17:58:25 24

24

24

24正點原子開拓者FPGA視頻:PLL鎖相環實驗

鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。

2019-09-20 07:05:00 3335

3335

3335

3335

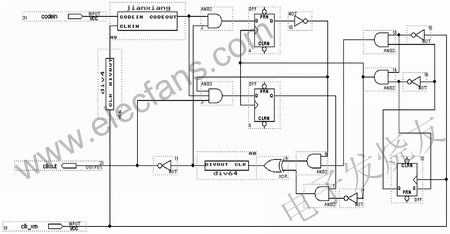

基于FPGA實現電路的同步提取性能設計

一般的位同步電路大多采用標準邏輯器件按傳統數字系統設計方法構成,具有功耗大,可靠性低的缺點。用FPGA設計電路具有很高的靈活性和可靠性,可以提高集成度和設計速度,增強系統的整體性能。本文給出了一種基于fpga的數字鎖相環位同步提取電路。

2019-04-19 08:24:00 2893

2893

2893

2893

用FPGA設計一階全數字鎖相環的方法

的問題進行了討論。 引言 鎖相環(PLL)技術在眾多領域得到了廣泛的應用。如信號處理,調制解調,時鐘同步,倍頻,頻率綜合等都應用到了鎖相環技術。傳統的鎖相環由模擬電路實現,而全數字鎖相環(DPLL)與傳統的模擬電路實現的PLL相比,具有精度高

2018-10-25 09:17:13 7963

7963

7963

7963鎖相環在調制和解調中的應用及概念解析

許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步,利用鎖相環路就可以實現這個目的。鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL)。鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。

2018-01-22 11:18:45 12994

12994

12994

12994

鎖相環CD4046的應用設計分析

于各種各樣的反饋控制系統中,例如,鎖相頻率合成;利用它的調制跟蹤和載波跟蹤特性,可以把它用于調制、解調、鎖相接收、載波恢 復、位同步提取等[1- 3];利用鎖相環的窄帶濾波特性,可以把淹沒在噪聲中的信號提取出來,所以可以把它用于

2017-10-27 17:09:20 13

13

13

13詳解FPGA數字鎖相環平臺

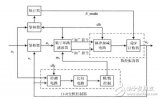

一、設計目標 基于鎖相環的理論,以載波恢復環為依托搭建數字鎖相環平臺,并在FPGA中實現鎖相環的基本功能。 在FPGA中實現鎖相環的自動增益控制,鎖定檢測,鎖定時間、失鎖時間的統計計算,多普勒頻偏

2017-10-16 11:36:45 18

18

18

18鎖相環的作用是什么_鎖相環的主要作用_什么是鎖相環

鎖相環是指一種電路或者模塊,它用于在通信的接收機中,其作用是對接收到的信號進行處理,并從其中提取某個時鐘的相位信息。或者說,對于接收到的信號,仿制一個時鐘信號,使得這兩個信號從某種角度來看是同步的(或者說,相干的)。

2017-07-27 10:01:51 31833

31833

31833

31833

多速率鎖相環相位同步方法的研究

用常規鎖相環技術可以很地的實現擾動較小條件下的交流電網的實時相位同步。為了克服當電網頻率出現較大的波動而且具有凹陷型擾動時常規鎖相環的相位同步誤差,本文提出了一種

2011-12-28 16:17:14 27

27

27

27擴頻通信的數字鎖相環設計

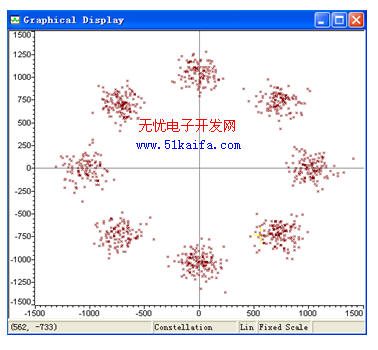

針對擴頻通信系統的載波同步,提出一套完善的數字鎖相環設計方案. 該方案利用新穎的可控根法完成1~3階模擬鎖相環(APLL)環路參數設計,并實現從模擬域到數字域的轉換,得到的數字鎖相

2011-08-26 16:10:38 122

122

122

122基于CORDIC算法的載波同步鎖相環設計

研究了一種利用CORDIC算法的矢量及旋轉模式對載波同步中相位偏移進行估計并校正的方法。設計并實現了基于CORDIC算法的數字鎖相環。通過仿真,驗證了設計的有效性和高效性。

2010-12-15 14:49:43 36

36

36

36基于FPGA的自適應鎖相環設計

利用鎖相環進行載波跟蹤是獲取本地載波的一種重要方法,針對鎖相環的噪聲性能和跟蹤速度不能同時達到最優的限制,在鎖相環PLL中引入自適應模塊,根據環路所處

2010-11-25 17:19:33 29

29

29

29一種基于FPGA實現的全數字鎖相環

鎖相環被廣泛應用于電力系統的測量和控制中。介紹了一種新型的基于比例積分控制邏輯的全數字鎖相環。通過對其數學模型的分析,闡述了該鎖相環的各項性能指標與設計參數的

2010-07-02 16:54:10 29

29

29

29模擬鎖相環,模擬鎖相環原理解析

模擬鎖相環,模擬鎖相環原理解析

背景知識:

鎖相技術是一種相位負反饋控制技術,它利用環路的反饋原理來產生新的頻率點。它的主要

2010-03-23 15:08:20 5716

5716

5716

5716數字鎖相環(DPLL),數字鎖相環(DPLL)是什么?

數字鎖相環(DPLL),數字鎖相環(DPLL)是什么?

背景知識:

隨著數字電路技術的發展,數字鎖相環在調制解調、頻率合成、FM 立體聲解碼、彩色副

2010-03-23 15:06:21 5312

5312

5312

5312寬頻帶數字鎖相環的設計及基于FPGA的實現

寬頻帶數字鎖相環的設計及基于FPGA的實現數字鎖相環(DPLL)技術在數字通信、無線電電子學等眾多領域得到了極為廣泛的應用。與傳統的模擬電路實現的

2009-11-23 21:00:58 1101

1101

1101

1101

智能全數字鎖相環的設計

智能全數字鎖相環的設計:在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智能配

2009-06-25 23:32:57 70

70

70

70智能全數字鎖相環的設計

摘要: 在FPGA片內實現全數字鎖相環用途極廣。本文在集成數字鎖相環74297的基礎上進行改進,設計了鎖相狀態檢測電路,配合CPU對環路濾波參數進行動態智

2009-06-20 12:39:32 1313

1313

1313

1313

基于DSP的高階COSTAS鎖相環的設計

基于DSP的高階COSTAS鎖相環的設計

COSTAS環是一種閉環自適應系統,用于提取相干載波。本文主要介紹了一種用于載波同步的高階COSTAS環路,用于完成MPSK的相干解調中的載

2009-05-25 18:15:36 1110

1110

1110

1110

模擬鎖相環應用實驗

一、實驗目的1、掌握模擬鎖相環的組成及工作原理。2、學習用集成鎖相環構成鎖相解調電路。3、學習用集成鎖相環構成鎖相倍頻電路。

二、鎖相環路的基本原理

2009-03-22 11:44:37 124

124

124

124鎖相環CD4046應用

鎖相環CD4046應用

鎖相的意義是相位同步的自動控制,能夠完成兩個電信號相位同步的自動控制閉環系統叫做鎖相環,簡稱PLL。它廣泛應用于廣播通信、

2009-03-18 15:11:18 1965

1965

1965

1965

鎖相環的研究和頻率合成

鎖相環的研究和頻率合成一、實驗目的:1. 振蕩器(VCO)的V—f 特性的研究2. 對稱波鎖相環基本特性的研究3. 利用鎖相環實現頻率合成二、鎖相環原理:

2009-03-06 20:02:52 1771

1771

1771

1771

應用于鎖相環的脈寬調整電路的設計

應用于鎖相環的脈寬調整電路的設計

前言

在鎖相環PLL、DLL和時鐘數據恢復電路CDR等電路的應用中,人們普遍要求輸出時鐘信號有50%的占空比,以便在時鐘上升及下

2008-10-16 08:59:42 967

967

967

967

軟件鎖相環的設計與應用

根據虛擬無線電技術的特點和鎖相環的基本原理,提出一種適于計算機軟件化實現的鎖相環數學模型,分析不同參數對鎖相環捕獲和跟蹤性能的影響,得出不同情況下參數設定的基

2008-08-15 12:36:19 98

98

98

98鎖相環原理

鎖相環原理

鎖相環路是一種反饋電路,鎖相環的英文全稱是Phase-Locked Loop,簡稱PLL。其作用是使得電路上的時鐘和某一外部時鐘的相位同步。因鎖相環可以

2007-08-21 14:46:04 4689

4689

4689

4689 電子發燒友App

電子發燒友App

評論