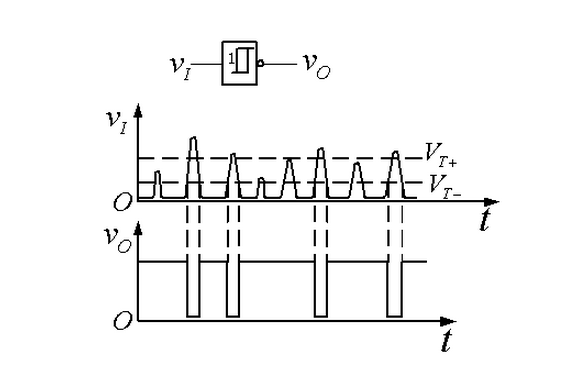

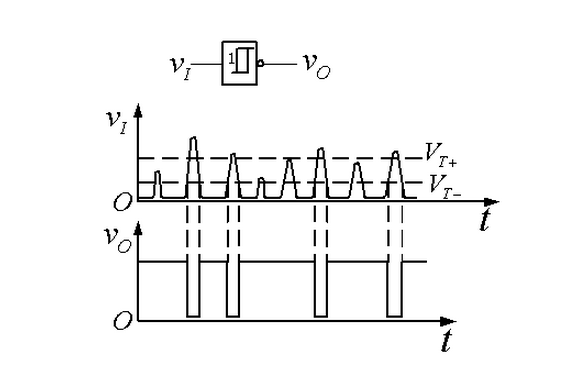

74HC14是施密特觸發(fā)器。正向閾值指輸入端電壓由低變高達(dá)到輸出翻轉(zhuǎn)時(shí)的值。反向閾值指輸入電壓由高到低變化輸出翻轉(zhuǎn)時(shí)的輸入電壓值。正向輸入閾值電壓是輸入大于這個(gè)電壓時(shí),輸出為低電平。反向輸入閾值電壓是輸入低于這個(gè)電壓時(shí),輸出為高電平。

2018-10-24 09:30:36 16607

16607

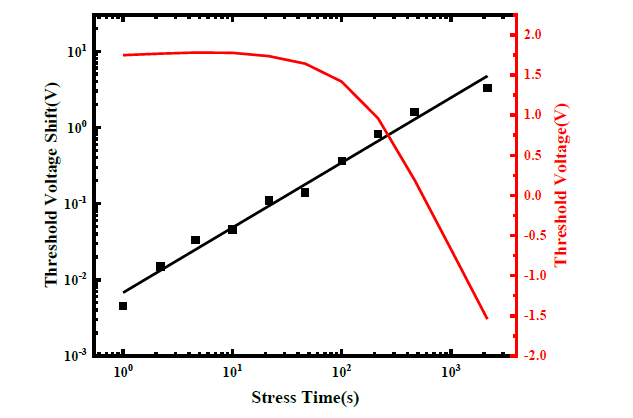

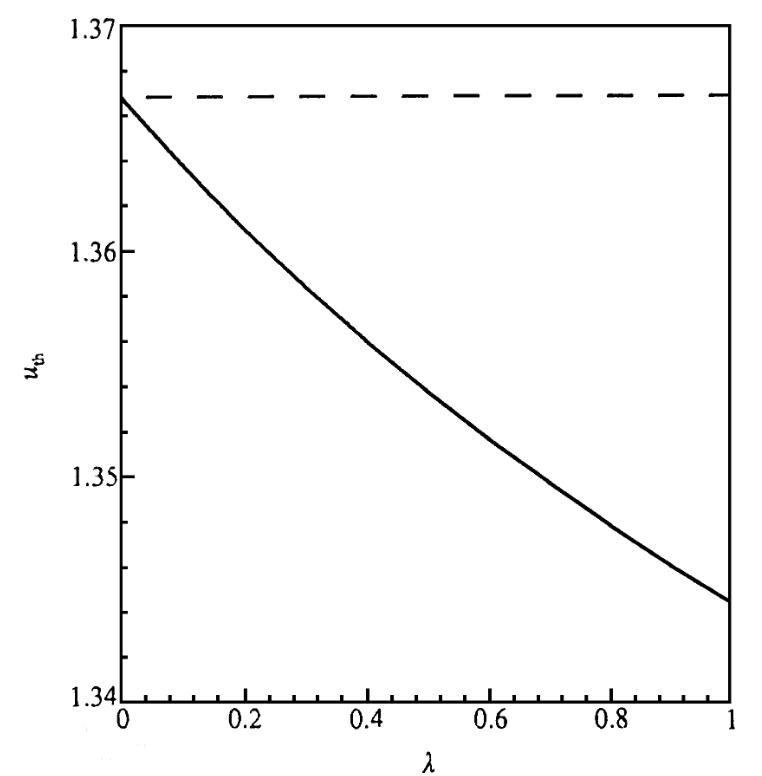

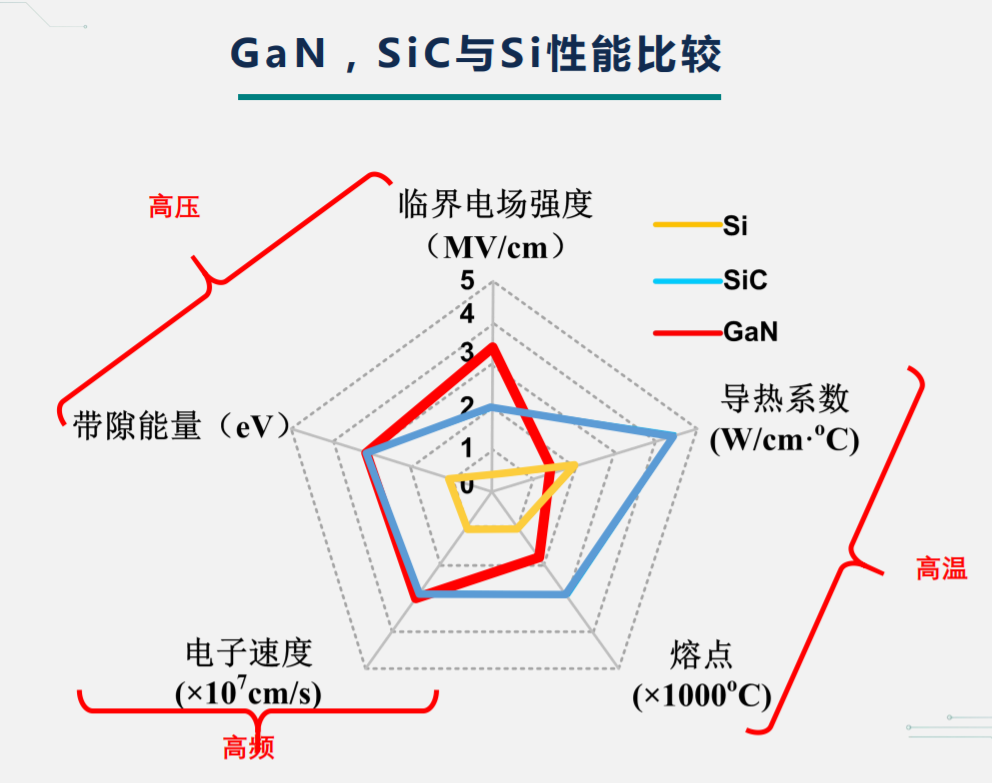

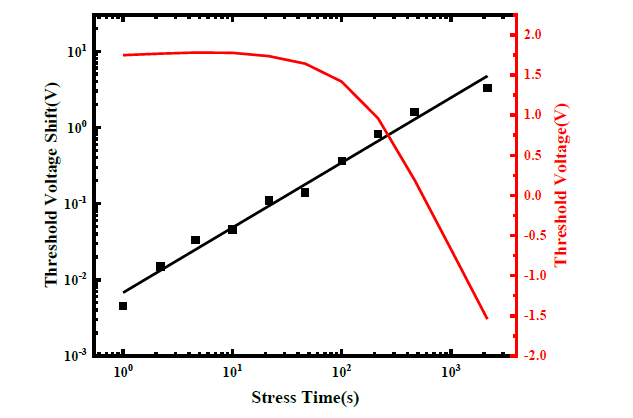

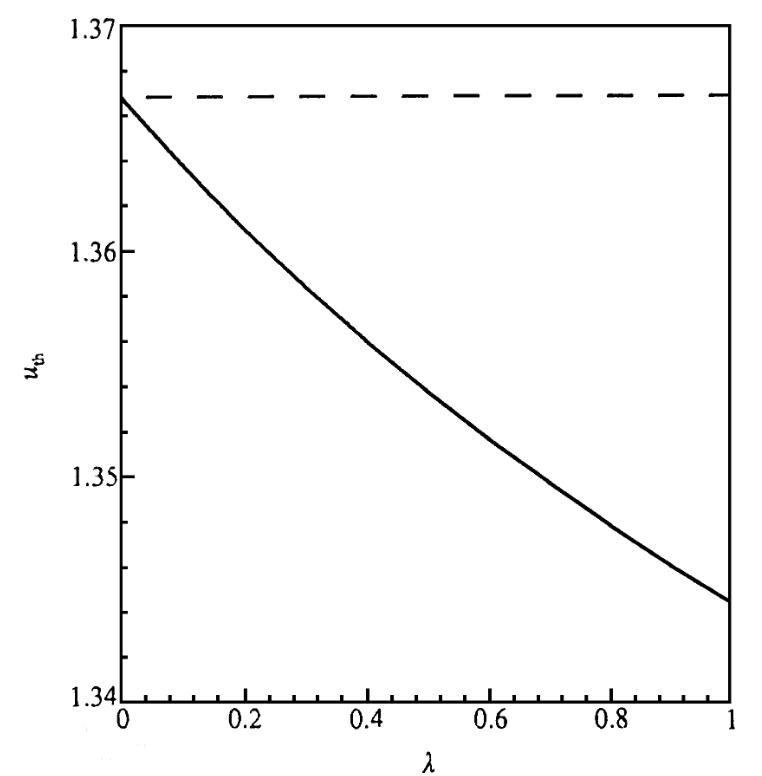

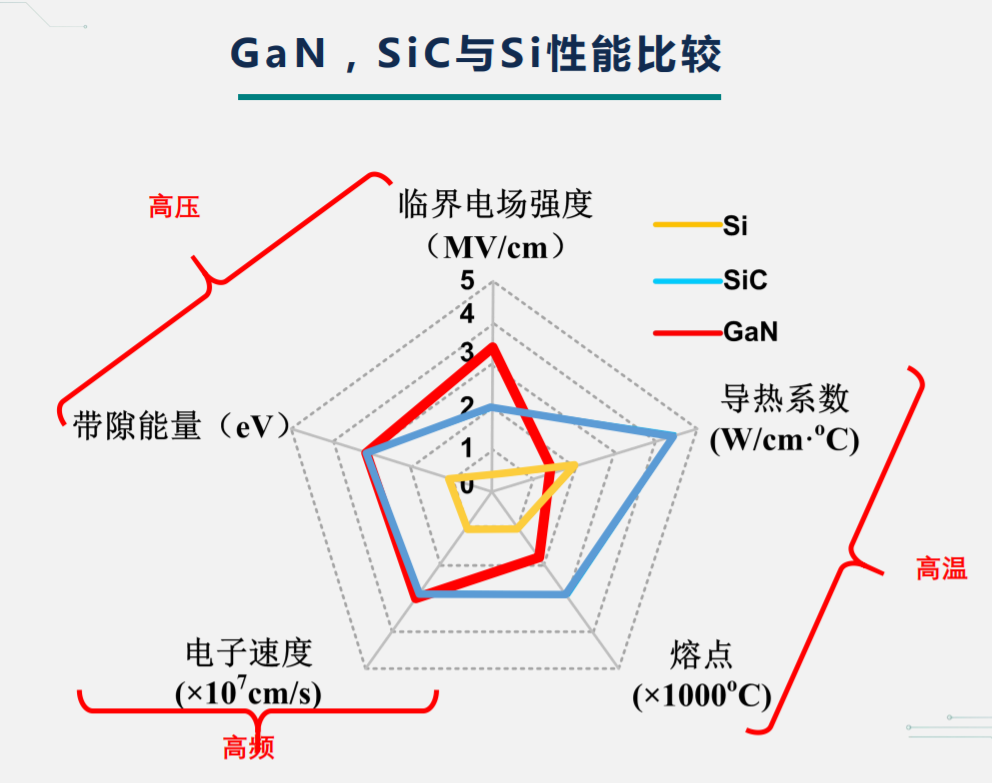

碳化硅SiC MOSFET的閾值電壓穩(wěn)定性相對(duì)Si材料來講,是比較差的,對(duì)應(yīng)用端的影響也很大。

2023-05-30 16:06:18 1173

1173

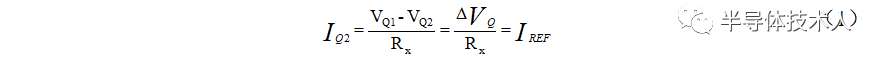

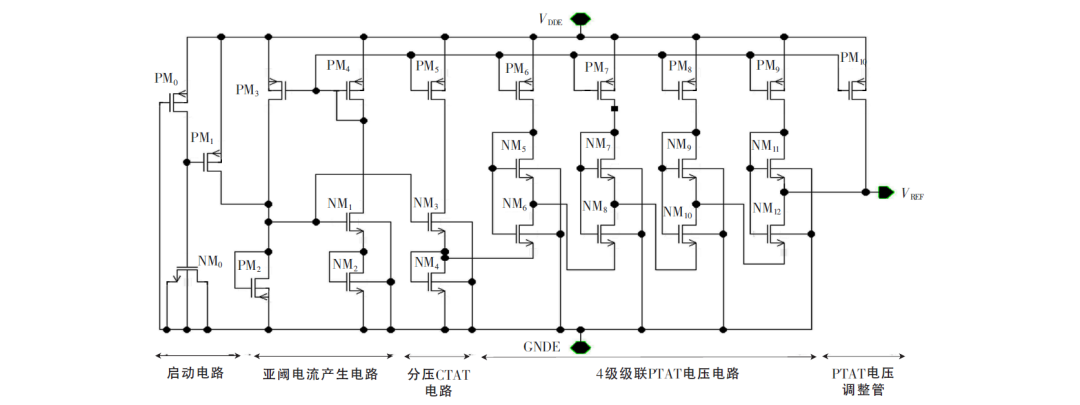

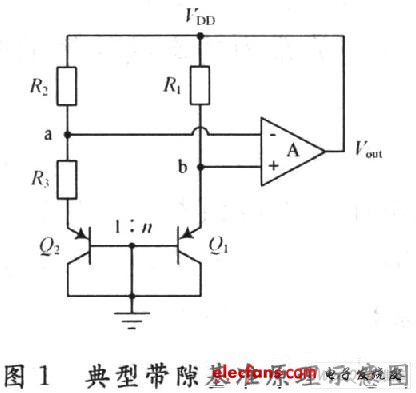

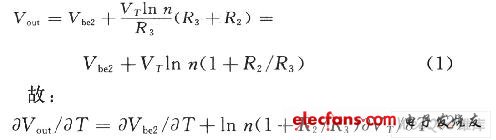

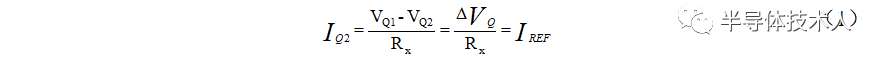

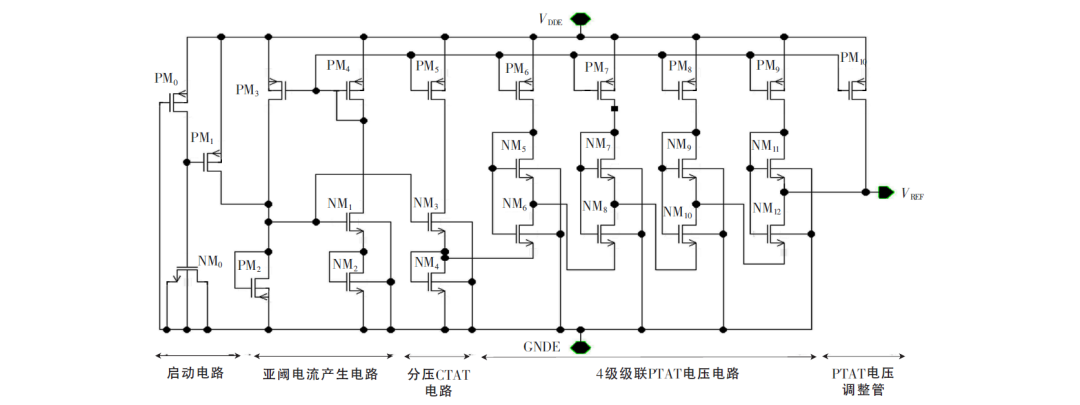

帶隙基準(zhǔn)廣泛應(yīng)用于模擬集成電路中。帶隙基準(zhǔn)電路輸出的基準(zhǔn)電壓可以為模擬集成電路提供穩(wěn)定的參考電壓或參考電流,

2023-07-06 10:42:01 1100

1100

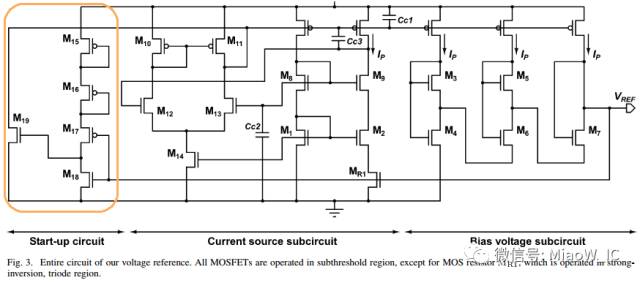

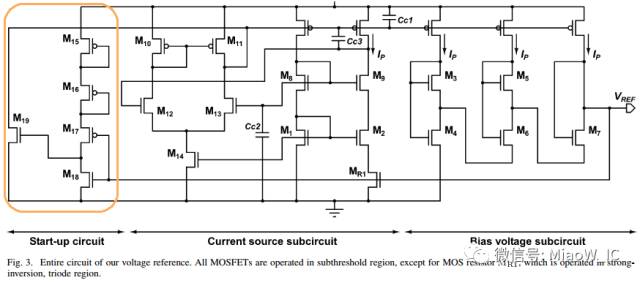

下拉晶體管源極輸出端即為啟動(dòng)電路的啟動(dòng)節(jié)點(diǎn),該啟動(dòng)節(jié)點(diǎn)連接帶隙基準(zhǔn)電路的PMOS電流鏡柵極,啟動(dòng)電路工作時(shí)將帶隙基準(zhǔn)電路中的PMOS電流鏡柵極電平拉低,為三極管充電。用于啟動(dòng)帶隙基準(zhǔn)電路,使帶隙基準(zhǔn)電路脫離錯(cuò)誤工作狀態(tài)。

2023-07-06 16:05:43 2121

2121

電壓源,而是使用何種基準(zhǔn)電壓源。 基準(zhǔn)電壓源只是一個(gè)電路或電路元件,只要電路需要,它就能提供已知電位。基準(zhǔn)電壓源主要有兩類:分流和串聯(lián)。基準(zhǔn)電壓源只是一個(gè)電路或電路元件,只要電路需要,它就能提供已知電位。這可能是幾分鐘、幾小時(shí)或幾年。

2023-07-17 11:40:00 1247

1247

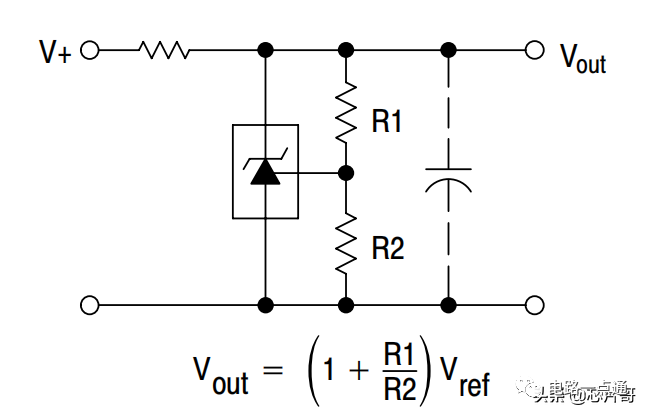

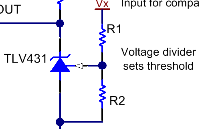

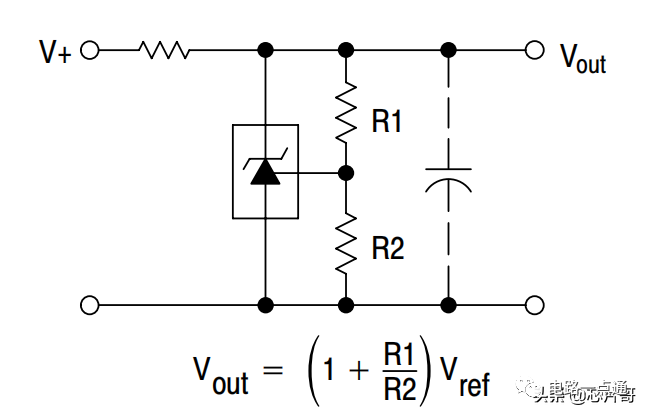

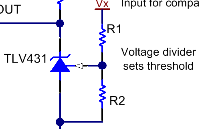

源電路,由于其應(yīng)用較少,因此電壓基準(zhǔn)源電路的設(shè)計(jì)要點(diǎn),并不是所有的工程師都能全部掌握;電路一點(diǎn)通就和小伙伴們一起分享下這些內(nèi)容電壓基準(zhǔn)源電路設(shè)計(jì)要點(diǎn),以TL431為例說明電路板。

2023-07-18 09:12:40 1359

1359

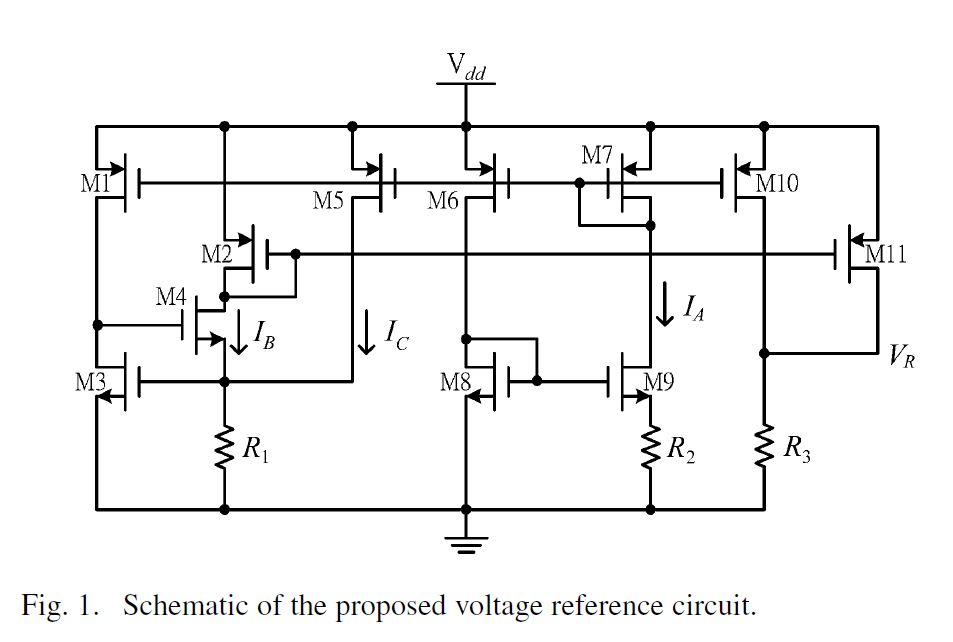

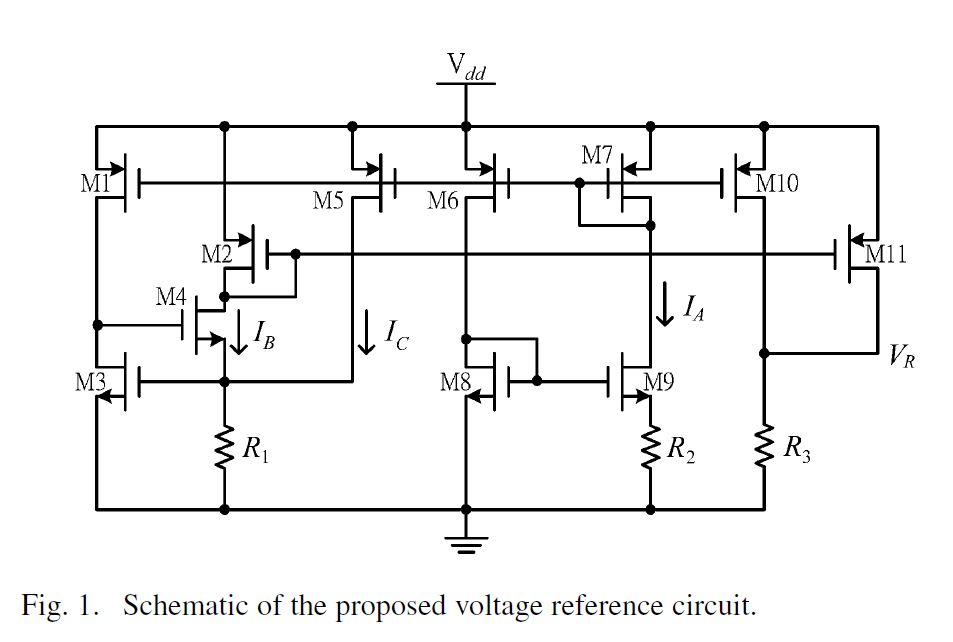

本次仿真的是2006年的論文[1],結(jié)構(gòu)簡(jiǎn)單,無三極管,利用CMOS亞閾值導(dǎo)電指數(shù)特性做溫度補(bǔ)償替代三極管,極大減小了面積和功耗,能在低壓工作,但是溫度特性較差。

2023-11-21 18:19:46 560

560

本次仿真的是2018年的論文[1],無三極管和電阻的,利用CMOS亞閾值導(dǎo)電指數(shù)特性做溫度補(bǔ)償替代三極管,極大減小了面積和功耗,能在低壓工作,溫度特性好,但基準(zhǔn)輸出值不太好調(diào)節(jié)。

2023-11-21 18:25:33 751

751

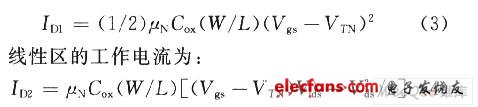

分析完閾值電壓的機(jī)制后,下面我們重點(diǎn)分析一下MOS器件的電壓、電流與閾值電壓之間的關(guān)系。

2023-11-29 14:42:33 998

998

CMOS模擬電路設(shè)計(jì)教材本書共11章大小:22M微電子學(xué)系列1.半導(dǎo)體器件-物理與工藝2.表面安裝技術(shù)手冊(cè)3.多晶硅發(fā)射極晶體管及其集成電路4.超大規(guī)模集成電路設(shè)計(jì)基礎(chǔ)-系統(tǒng)與電路5.SOI技術(shù)—21世紀(jì)的硅集成電路技術(shù)6.CMOS模擬電路設(shè)計(jì)[hide]CMOS模擬電路設(shè)計(jì).pdf[/hide]

2009-11-19 17:04:30

片上集成基準(zhǔn)電壓源和基準(zhǔn)電壓源緩沖器,但這類器件在功耗或性能方面可能并非最佳——通常使用外部基準(zhǔn)電壓源電路才可達(dá)到最佳性能。本文探討基準(zhǔn)電壓源電路設(shè)計(jì)中遇到的挑戰(zhàn)和要求。 基準(zhǔn)電壓輸入逐次逼近型

2020-04-14 07:00:00

片上集成基準(zhǔn)電壓源和基準(zhǔn)電壓源緩沖器,但這類器件在功耗或性能方面可能并非最佳——通常使用外部基準(zhǔn)電壓源電路才可達(dá)到最佳性能。本文探討基準(zhǔn)電壓源電路設(shè)計(jì)中遇到的挑戰(zhàn)和要求。

2021-03-16 12:04:19

MOSFET的VGS(th):柵極閾值電壓MOSFET的VGS(th):柵極閾值電壓是為使MOSFET導(dǎo)通,柵極與源極間必需的電壓。也就是說,VGS如果是閾值以上的電壓,則MOSFET導(dǎo)通。可能有

2019-05-02 09:41:04

為什么PMOS的閾值電壓要高于NMOS呢?下面是我用HSPICE仿真的代碼.opt scale=0.1u * Set lambdamp drainp gatep Vdd Vdd pch l=2 w

2018-11-15 14:00:50

STM32是3.3V供電的芯片,在用AD的時(shí)候,閾值電壓能否接到0-5V上?

2013-02-28 18:18:59

,進(jìn)而使SCR導(dǎo)通。

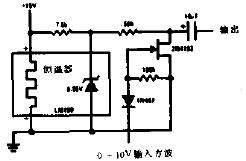

實(shí)驗(yàn)中:穩(wěn)壓管閾值電壓較大時(shí)SCR可正常導(dǎo)通;但是穩(wěn)壓管閾值小的時(shí)候,SCR始終不通,后端電路一直有漏電流。(如圖所示穩(wěn)壓管閾值電壓為42V)

2023-10-10 08:57:00

中的電源保護(hù)。 關(guān)鍵詞: CMOS; 欠壓保護(hù) 1.引言 在電機(jī)驅(qū)動(dòng)、UPS等系統(tǒng)中電壓的穩(wěn)定尤為重要,欠壓、過壓保護(hù)是必不可少的,因此通過在芯片內(nèi)部集成過壓、欠壓保護(hù)電路來提高電源的可靠性

2018-08-27 15:54:31

如何實(shí)現(xiàn)CMOS圖像敏感器驅(qū)動(dòng)電路設(shè)計(jì)?CMOS圖像敏感器STAR250的技術(shù)指標(biāo)是什么?如何實(shí)現(xiàn)Verilog HDL驅(qū)動(dòng)時(shí)序設(shè)計(jì)?

2021-04-20 06:59:27

電壓,低溫)作為最快的一種情況,而把(slow n,slow p,低電壓,高溫)作為最慢的一種情況。但是管子的閾值電壓與溫度成反比,也就是低溫時(shí)管子的閾值電壓會(huì)變高,而使得管子變慢,這就與上面的結(jié)論矛盾

2021-06-24 08:01:38

如果想改變反相滯回比較器的閾值電壓應(yīng)改變哪些參數(shù)呢?

2023-03-24 15:31:42

當(dāng)前固體微光器件以EBCCD 及EMCCD 器件為主,隨著CMOS 工藝及電路設(shè)計(jì)技術(shù)的發(fā)展, 微光CMOS 圖像傳感器的性能在不斷提高,通過采用專項(xiàng)技術(shù),微光CMOS 圖像傳感器的性能已接

2018-11-12 15:37:40

研究經(jīng)歷,使本書也非常適合作為CMOS模擬集成電路設(shè)計(jì)或相關(guān)領(lǐng)域的研究人員和工程技術(shù)人員的參考書。... 本書介紹模擬CMOS集成電路的分析與設(shè)計(jì)。從直觀和嚴(yán)密的角度闡述了各種模擬電路的基本原理和概念

2016-10-07 08:38:30

模擬CMOS集成電路設(shè)計(jì)本書介紹模擬CMOS集成電路的分析與設(shè)計(jì)。從直觀和嚴(yán)密的角度闡述了各種模擬電路的基本原理和概念,同時(shí)還闡述了在SOC中模擬電路設(shè)計(jì)遇到的新問題及電路技術(shù)的新發(fā)展。本書由淺入深

2009-09-25 10:04:03

模擬CMOS集成電路設(shè)計(jì)

2019-03-13 15:34:10

各位大神,請(qǐng)問有沒有做過cadence的CMOS帶隙基準(zhǔn)電路設(shè)計(jì),或者CMOS四運(yùn)算放大器設(shè)計(jì)(LM324),求各位幫幫忙,我快山窮水盡了

2020-05-17 23:32:07

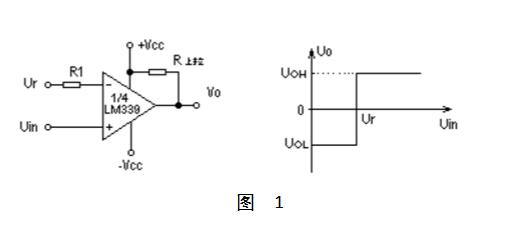

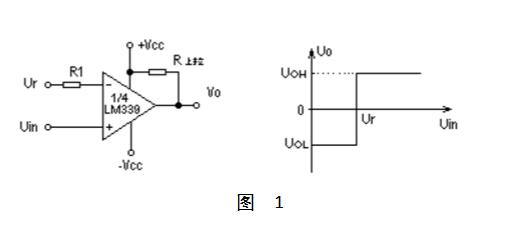

遲滯比較器的閾值電壓除了由我的電阻參數(shù)設(shè)定 還要其他因素嗎?我做的實(shí)驗(yàn)中顯示我的設(shè)定值與實(shí)際值在某些情況下相差挺大的,我采用的是LM339這款比較器芯片。比如 我設(shè)定的值為VTL=1.5V、VTH=2.5V時(shí),通過示波器觀察的到的VTL=2.48V、VTH=3.64V。

2019-04-01 16:51:27

新穎的PTAT電流產(chǎn)生電路結(jié)構(gòu),以對(duì)二極管連接的NMOS晶體管的閾值電壓進(jìn)行補(bǔ)償,得到一個(gè)高精度基準(zhǔn)電壓源。該電路占用芯片面積小,精度高,可移植性強(qiáng),非常適用于當(dāng)今高精度的A/D,D/A和高精度運(yùn)放偏置電路。此電路已成功應(yīng)用于某款高速DAC芯片中。

2018-11-30 16:38:24

cmos射頻集成電路設(shè)計(jì)這本被譽(yù)為射頻集成電路設(shè)計(jì)指南的書全面深入地介紹了設(shè)計(jì)千兆赫(GHz)CMOS射頻集

2008-09-16 15:43:18 312

312 摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問題并作出折衷。本文討論了不同類型的電壓基準(zhǔn)源以及它們的關(guān)鍵

2009-04-27 11:12:06 42

42 介紹了一種簡(jiǎn)單的高性能基準(zhǔn)源電路,該電路利用了工作在飽和區(qū)和亞閾值區(qū)的MOS晶體管遷移率和閾值電壓溫度特性進(jìn)行補(bǔ)償,此外還利用二極管反相偏置電流的溫度特性來改進(jìn)

2009-08-28 11:11:36 29

29 高級(jí)基準(zhǔn)電壓Vbandgap IC設(shè)計(jì):在本文中,主要討論在CMOS 技術(shù)中基準(zhǔn)產(chǎn)生的設(shè)計(jì)著重于公認(rèn)的“帶隙”技術(shù),即是與電壓,溫度變化無關(guān)的基準(zhǔn)電壓。[關(guān)鍵詞]電壓基準(zhǔn),電流基

2009-11-01 14:35:44 34

34 選擇最佳的電壓基準(zhǔn)源摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問題并作出折衷。本文討論了

2009-12-07 14:32:23 45

45 本文設(shè)計(jì)了一種簡(jiǎn)單的一階溫度補(bǔ)償電流基準(zhǔn)源。主要利用電阻的溫度系數(shù)與閾值電壓VTH 溫度系數(shù)相同的特性實(shí)現(xiàn)溫度補(bǔ)償原理。該主體電路采用低壓共源共柵(即CASCODE)結(jié)構(gòu)

2009-12-14 09:39:43 18

18 選擇最佳的電壓基準(zhǔn)源供稿:美信摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問題并作出折衷。本文討

2010-01-08 23:02:30 77

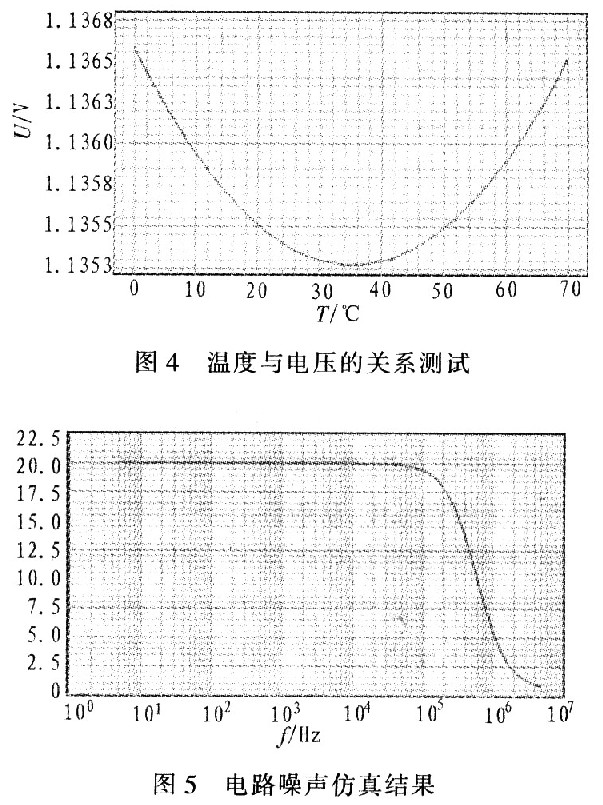

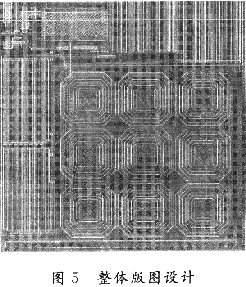

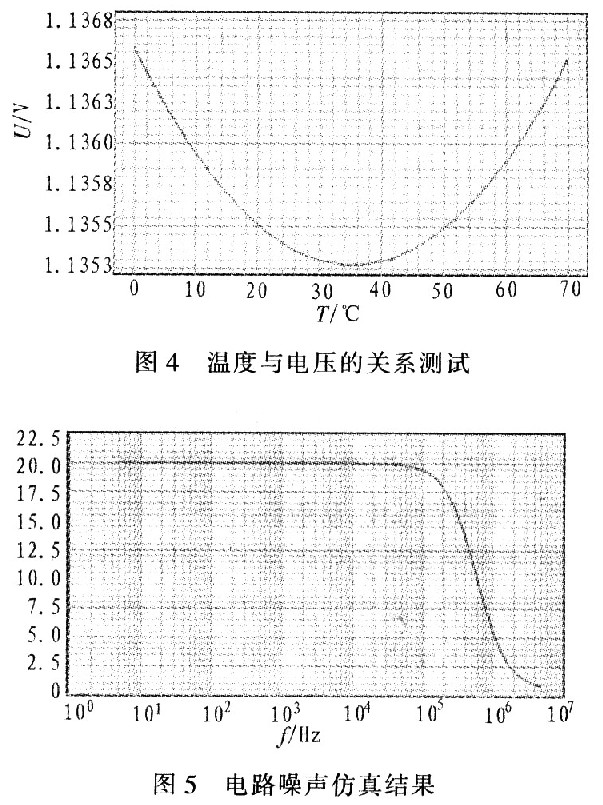

77 本文提出了一種結(jié)構(gòu)簡(jiǎn)單高電源抑制比的CMOS 帶隙基準(zhǔn)電壓源,供電電源3.3V。采用CSMC 0.5um CMOS 工藝。Spectre 仿真結(jié)果表明,基準(zhǔn)輸出電壓在溫度為-40~+80℃時(shí),溫度系數(shù)為45.53×10-6/

2010-01-11 14:20:43 27

27 隨著工藝進(jìn)入深亞微米階段,漏電流帶來的靜態(tài)功耗已經(jīng)成為不可忽視的部分。多閾值CMOS技術(shù)是一種降低電路漏電流功耗的有效方法。本文在延遲不敏感異步電路中應(yīng)用多閾值CMOS技

2010-02-24 15:51:06 12

12 介紹了一種低壓電流模帶隙電壓基準(zhǔn)電路,并提出了一種新穎的啟動(dòng)電路結(jié)構(gòu).電路采用預(yù)先設(shè)置電路工作點(diǎn)和反饋控

2010-04-13 08:58:44 53

53 本文提出了一種結(jié)構(gòu)簡(jiǎn)單高電源抑制比的CMOS帶隙基準(zhǔn)電壓源,供電電源3.3V。采用CSMC 0.5um CMOS工藝。Spectre仿真結(jié)果表明,基準(zhǔn)輸出電壓在溫度為-40~+80℃時(shí),溫度系數(shù)為45.53×10-6/℃

2010-07-14 16:14:36 41

41 在對(duì)傳統(tǒng)典型CMOS帶隙電壓基準(zhǔn)源電路分析基礎(chǔ)上提出了一種高精度,高電源抑制帶隙電壓基準(zhǔn)源。電路運(yùn)用帶隙溫度補(bǔ)償技術(shù),采用共源共柵電流鏡,兩級(jí)運(yùn)放輸出用于自身偏置電路

2010-08-03 10:51:34 0

0 復(fù)位監(jiān)控器件內(nèi)部集成精確的電壓監(jiān)控電路,可通過確定的閾值電壓啟動(dòng)復(fù)位操作,同時(shí)排除瞬間干擾的影響,又可以防止MCU在電源啟動(dòng)和關(guān)閉期間的誤操作,保證數(shù)據(jù)安全。通常

2010-11-17 17:43:05 39

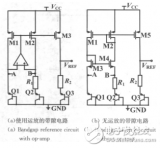

39 基于工作在亞閾值區(qū)的MOS器件,運(yùn)用CMOS電流模基準(zhǔn)對(duì)CATA和PTAT電流求和的思想,提出一種具有低溫漂系數(shù)、高電源抑制比(PSRR)的CMOS電壓基準(zhǔn)源,該電路可同時(shí)提供多個(gè)輸出基準(zhǔn)電

2010-12-30 10:25:53 26

26 結(jié)合工作在亞閾值區(qū)、飽和區(qū)和線性區(qū)的MOS管,提出一種純MOS結(jié)構(gòu)的基準(zhǔn)電壓源,其結(jié)構(gòu)能有效補(bǔ)償MOS管的載流子遷移率和亞閾值斜率的溫度系數(shù)。基于SMIC0.13μm的CMOS工藝的仿真結(jié)

2011-01-04 16:17:31 27

27 選擇最佳的電壓基準(zhǔn)源

摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問題并作出

2009-01-23 22:03:12 1804

1804

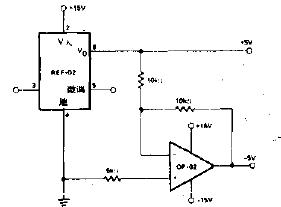

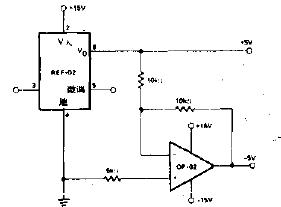

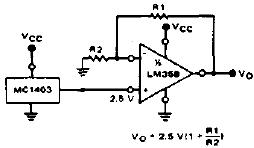

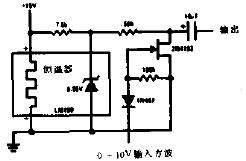

±5V基準(zhǔn)電壓源電路圖

2009-04-15 08:53:36 4307

4307

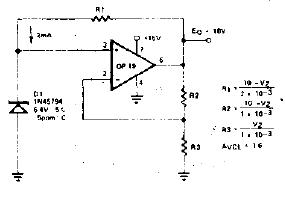

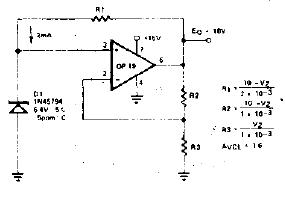

高穩(wěn)定基準(zhǔn)電壓源電路圖

2009-04-15 08:57:11 908

908

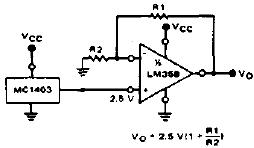

基準(zhǔn)電壓電路圖1

2009-04-15 08:57:58 1618

1618

精密基準(zhǔn)方波基準(zhǔn)電壓源電路圖

2009-04-15 09:00:27 1216

1216

摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問題并作出折衷。本文討論了不同類型的電壓基準(zhǔn)源以及它們的關(guān)鍵

2009-04-29 11:30:23 595

595

摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問題并作出折衷。本文討論了不同類型的電壓基準(zhǔn)源以及它們的關(guān)鍵

2009-05-03 14:42:34 474

474

摘要:電壓基準(zhǔn)源簡(jiǎn)單、穩(wěn)定的基準(zhǔn)電壓,作為電路設(shè)計(jì)的一個(gè)關(guān)鍵因素,電壓基準(zhǔn)源的選擇需要考慮多方面的問題并作出折衷。本文討論了不同類型的電壓基準(zhǔn)源以及它們的關(guān)鍵

2009-05-06 09:29:30 535

535

模擬電路設(shè)計(jì)常常用到電壓基準(zhǔn)和電流基準(zhǔn)。這些基準(zhǔn)受電源、溫度或者工藝參數(shù)的影響很小,為電路提供一個(gè)相對(duì)穩(wěn)定的參考電壓或者電流,從而保證整個(gè)模擬電路穩(wěn)定工作。

2010-07-08 09:45:00 2331

2331

引言

模擬電路中廣泛地包含電壓基準(zhǔn)(reference voltage)和電流基準(zhǔn)(current reference)。在數(shù)/模轉(zhuǎn)換器、模/數(shù)轉(zhuǎn)換器等電路中,基準(zhǔn)電壓的精度直接決定著這些電路的

2010-09-30 10:11:55 3772

3772

在模擬及數(shù)/模混合集成電路設(shè)計(jì)中,電壓基準(zhǔn)是非常重要的電路模塊之一,而通過巧妙設(shè)計(jì)的帶隙電壓基準(zhǔn)更是以其與電源電壓、工藝、溫度變化幾乎無關(guān)的特點(diǎn),廣泛應(yīng)用

2010-11-02 09:40:44 1729

1729

低電壓高精度CMOS基準(zhǔn)電流源設(shè)計(jì)

2011-01-24 15:10:17 95

95 基準(zhǔn)電壓源是集成電路系統(tǒng)中一個(gè)非常重要的構(gòu)成單元。結(jié)合近年來的設(shè)計(jì)經(jīng)驗(yàn),首先給出了帶隙基準(zhǔn)源曲率產(chǎn)生的主要原因,而后介紹了在高性能CMOS 帶隙基準(zhǔn)電壓源中所廣泛采用的幾種

2011-05-25 14:52:44 34

34 本文利用高電源抑制比電路設(shè)計(jì)的和式偏置電流源進(jìn)一步提高了電源抑制比,并利用NMOS和PMOS管的兩個(gè)閾值電壓VTHN和VTHP具有相同方向但不同數(shù)量的溫度系數(shù),設(shè)計(jì)了一種基于不同VTH值的

2011-08-18 11:29:32 2399

2399 基準(zhǔn)電壓源是集成電路系統(tǒng)中一個(gè)非常重要的構(gòu)成單元。結(jié)合近年來的設(shè)計(jì)經(jīng)驗(yàn),首先給出了帶隙基準(zhǔn)源曲率產(chǎn)生的主要原因,而后介紹了在高性能CMOS 帶隙基準(zhǔn)電壓源中所廣泛采用的幾種

2011-09-27 14:30:52 58

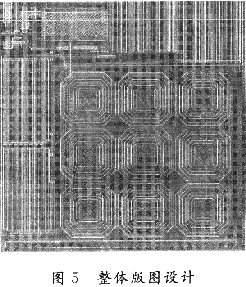

58 在傳統(tǒng)帶隙基準(zhǔn)電壓源電路結(jié)構(gòu)的基礎(chǔ)上,通過在運(yùn)放中引入增益提高級(jí),實(shí)現(xiàn)了一種用于音頻-A/D轉(zhuǎn)換器的CMOS帶隙電壓基準(zhǔn)源。在一階溫度補(bǔ)償下實(shí)現(xiàn)了較高的電源抑制比(PSRR)和較

2012-10-10 14:49:50 43

43 根據(jù)汽車發(fā)動(dòng)機(jī)控制芯片的工作環(huán)境,針對(duì)常見的溫度失效問題,提出了一種應(yīng)用在發(fā)動(dòng)機(jī)控制芯片中的帶隙基準(zhǔn)電壓源電路。該電路采用0.18 m CMOS工藝,采用電流型帶隙基準(zhǔn)電壓源結(jié)構(gòu)

2013-09-26 17:06:12 33

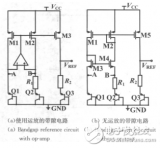

33 。本電路采用TSMC 0.18 μm混合信號(hào)CMOS工藝,仿真結(jié)果顯示,輸出基準(zhǔn)電壓為1.213 V,靜態(tài)電流為538 nA,在-55~125 ℃溫度范圍內(nèi),溫度系數(shù)僅為10.58 ppm/℃,低頻時(shí)的電源抑

2015-12-08 11:40:25 17

17 一種高電源抑制低溫漂帶隙基準(zhǔn)電路設(shè)計(jì)_于全東

2017-01-03 15:24:45 1

1 低溫漂系數(shù)共源共柵CMOS帶隙基準(zhǔn)電壓源_鄧玉斌

2017-01-08 10:24:07 5

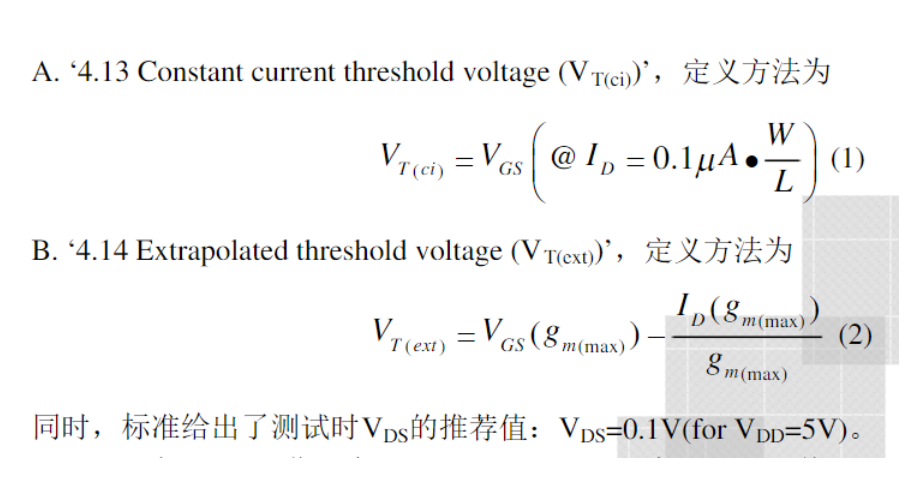

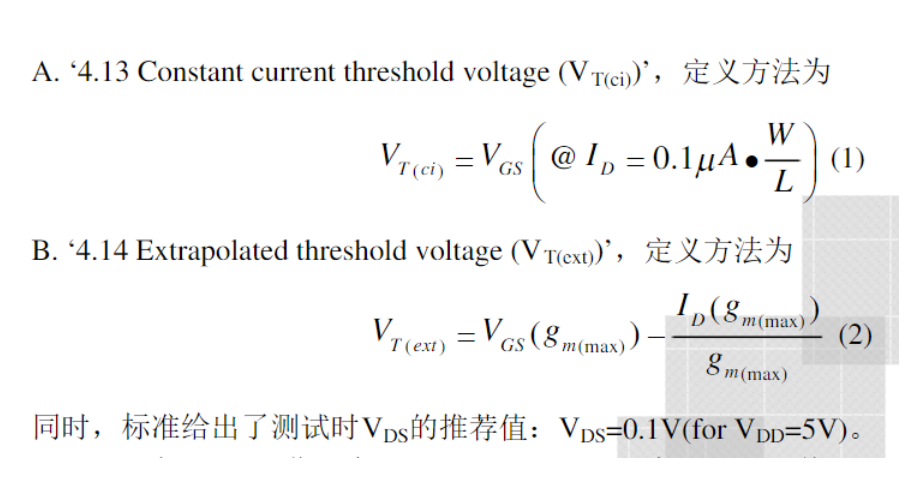

5 面向BTI特征分析的在運(yùn)行中閾值電壓測(cè)量

2017-01-22 13:38:08 7

7 高分辨率、逐次逼近型ADC的整體精度取決于精度、穩(wěn)定性和其基準(zhǔn)電壓源的驅(qū)動(dòng)能力。本文探討基準(zhǔn)電壓源電路設(shè)計(jì)中遇到的挑戰(zhàn)和要求。

2017-09-15 15:45:17 17

17 帶隙是導(dǎo)帶的最低點(diǎn)和價(jià)帶的最高點(diǎn)的能量之差。也稱能隙。帶隙越大,電子由價(jià)帶被激發(fā)到導(dǎo)帶越難,本征載流子濃度就越低,電導(dǎo)率也就越低帶隙主要作為帶隙基準(zhǔn)的簡(jiǎn)稱,帶隙基準(zhǔn)是所有基準(zhǔn)電壓中最受歡迎的一種

2017-11-24 15:45:20 22131

22131

閾值電壓 (Threshold voltage):通常將傳輸特性曲線中輸出電壓隨輸入電壓改變而急劇變化轉(zhuǎn)折區(qū)的中點(diǎn)對(duì)應(yīng)的輸入電壓稱為閾值電壓。在描述不同的器件時(shí)具有不同的參數(shù)。如描述場(chǎng)發(fā)射的特性時(shí),電流達(dá)到10mA時(shí)的電壓被稱為閾值電壓。

2017-11-27 17:18:43 67568

67568

本文為大家介紹一個(gè)cmos無運(yùn)放帶隙基準(zhǔn)源電路。

2018-01-11 16:52:50 14756

14756

本文開始介紹了單限比較器的電路和單限比較器的理論分析及計(jì)算,其次介紹了單限電壓比較器的工作原理,最后介紹了單限比較器閾值的電壓計(jì)算。

2018-02-26 15:58:02 64100

64100

關(guān)于 MOSFET 的 W 和 L 對(duì)其閾值電壓 Vth 的影響,實(shí)際在考慮工藝相關(guān)因素后都是比較復(fù)雜,但是也可以有一些簡(jiǎn)化的分析,這里主要還是分析當(dāng)晶體管處在窄溝道和短溝道情況下,MOSFET 耗盡區(qū)的電荷的變化,從而分析其對(duì)晶體管的閾值電壓的作用。

2019-06-18 17:19:46 35146

35146

介紹了一種采用亞閾值mos晶體管和單bjt的低溫系數(shù)(tc)和大功率電源紋波抑制(psrr)cmos子帶隙基準(zhǔn)電壓源(sub-bgr)電路。所提出的子bgr包括一種基于bjt的標(biāo)度發(fā)射極基極電壓

2019-09-30 08:00:00 2

2 本文報(bào)道了一個(gè)深入研究的負(fù)閾值電壓不穩(wěn)定性的gan-on-si金屬絕緣體半導(dǎo)體高電子遷移率晶體管部分凹陷algan。基于一組在不同溫度下進(jìn)行的應(yīng)力/恢復(fù)實(shí)驗(yàn),我們證明:1)在高溫和負(fù)柵偏壓(-10v

2019-10-09 08:00:00 2

2 本文報(bào)道了algan/gan高電子遷移率晶體管(hemt)在反向柵偏壓作用下閾值電壓的負(fù)漂移。該器件在強(qiáng)pinch-off和低漏源電壓條件下偏置一定時(shí)間(反向柵極偏置應(yīng)力),然后測(cè)量傳輸特性。施加

2019-10-09 08:00:00 10

10 ADC 片上集成基準(zhǔn)電壓源和基準(zhǔn)電壓源緩沖器,但這類器件在功耗或性能方面可能并非最佳——通常使用外部基準(zhǔn)電壓源電路才可達(dá)到最佳性能。本文探討基準(zhǔn)電壓源電路設(shè)計(jì)中遇到的挑戰(zhàn)和要求。

2021-01-07 23:55:00 21

21 AN-680: ADG451/ADG452/ADG453閾值電壓與數(shù)字電壓 VL

2021-03-18 20:33:08 2

2 些則需要外部基準(zhǔn)。知道了這一點(diǎn),那么我們就需要考慮,如何在應(yīng)用中選擇合適的ADC或DAC基準(zhǔn)類型呢? 一般來說,有3種主要的基準(zhǔn)類型可供選擇:內(nèi)部、外部和電源。 1.內(nèi)部基準(zhǔn) 轉(zhuǎn)換器內(nèi)置的一些基準(zhǔn)電壓。在下面的典型電路中,內(nèi)部基準(zhǔn)類型有助于減少電路設(shè)計(jì)中

2021-12-10 09:41:27 4431

4431 CMOS集成電路設(shè)計(jì)基礎(chǔ)免費(fèi)下載。

2022-03-03 10:06:12 0

0 Vt roll-off核心是(同一個(gè)工藝節(jié)點(diǎn)下面)閾值電壓與柵長之間的關(guān)系。當(dāng)溝道長度比較長的時(shí)候,Vt值是比較穩(wěn)定的。隨著溝道長度的減小,閾值電壓會(huì)下降(對(duì)于PMOS而言是絕對(duì)值的下降)。

2022-12-30 15:14:41 1332

1332 精確控制集成電路中MOSFET的閾值電壓對(duì)電路的可靠性至關(guān)重要。通常情況下,閾值電壓是通過向溝道區(qū)的離子注入來調(diào)整的。

2023-02-09 14:26:36 1147

1147 此外,襯底偏壓也能影響閾值電壓。當(dāng)在襯底和源極之間施加反向偏壓時(shí),耗盡區(qū)被加寬,實(shí)現(xiàn)反轉(zhuǎn)所需的閾值電壓也必須增加,以適應(yīng)更大的Qsc。

2023-02-09 14:26:38 1660

1660 nmos晶體管的閾值電壓公式為Vt=Vt0-γ(2φF/Cox),其中Vt0為晶體管的基礎(chǔ)閾值電壓,γ為晶體管的偏置系數(shù),φF為晶體管的反向偏置電勢(shì),Cox為晶體管的歐姆容量。

2023-02-11 16:30:14 9781

9781

Vt指的是MOS管的閾值電壓(threshold voltage)。具體定義(以下圖NMOS為例):當(dāng)柵源電壓(Vgs)由0逐漸增大,直到MOS管溝道形成反型層(圖中的三角形)所需要的電壓為閾值電壓。

2023-03-10 17:43:11 4539

4539 在圖 1 所示的原理圖中,TLV431 可調(diào)分流基準(zhǔn)配置為開環(huán)操作,這意味著輸出未連接到反饋引腳。 相反,信號(hào)VX通過電阻分壓器驅(qū)動(dòng)反饋引腳。 電阻分壓器的設(shè)置使得當(dāng)VX處于閾值電壓VTH時(shí),反饋引腳上的值等于內(nèi)部基準(zhǔn)電壓。

2023-04-11 09:17:28 1518

1518

由于SiC MOSFET與Si MOSFET特性的不同,SiC MOSFET的閾值電壓具有不穩(wěn)定性,在器件測(cè)試過程中閾值電壓會(huì)有明顯漂移,導(dǎo)致其電性能測(cè)試以及高溫柵偏試驗(yàn)后的電測(cè)試結(jié)果嚴(yán)重依賴于測(cè)試

2023-05-09 14:59:06 853

853

與溫度關(guān)系很小的電壓或者電流基準(zhǔn),在實(shí)際電路設(shè)計(jì)中具有重要的應(yīng)用,比如在電流鏡結(jié)構(gòu)中,需要對(duì)一“理想的”基準(zhǔn)電流進(jìn)行精確復(fù)制,這一“理想的”基準(zhǔn)電流,一般由帶隙基準(zhǔn)電路產(chǎn)生。

2023-07-06 11:32:14 2369

2369

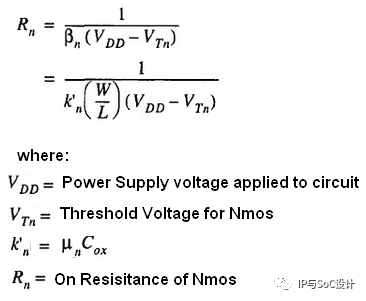

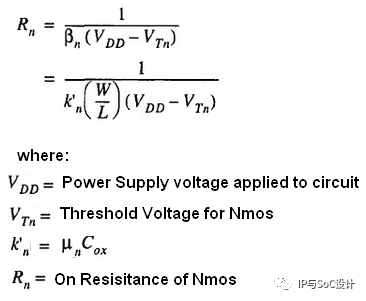

如果你能看到下面的方程式-我相信你可以很容易地弄清楚閾值電壓對(duì)電池延遲的影響。(注:以下電阻公式是關(guān)于NMOS的。您也可以為PMOS導(dǎo)出類似的公式(只需將下標(biāo)“n”替換為“p”)。

2023-09-07 10:03:59 649

649

影響MOSFET閾值電壓的因素? MOSFET(金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)管)是一種常用的半導(dǎo)體器件,具有高輸入阻抗、低輸出阻抗、高增益等特點(diǎn)。MOSFET的閾值電壓是決定其工作狀態(tài)的重要參數(shù),影響著

2023-09-17 10:39:44 6670

6670 高、速度快等優(yōu)點(diǎn),在眾多電子設(shè)備中應(yīng)用廣泛。其中,基準(zhǔn)電壓就是一個(gè)比較重要的參數(shù),而基準(zhǔn)電壓的溫度系數(shù)是指在不同溫度下電路帶來的基準(zhǔn)電壓變化情況。 通常來說,CMOS電路中使用的帶隙基準(zhǔn)技術(shù),具有多晶硅、硅谷能帶、亞穩(wěn)態(tài)等技術(shù),但是這些技術(shù)都存在著一定的溫度漂移問題。而在實(shí)際

2023-10-23 10:29:11 318

318

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論