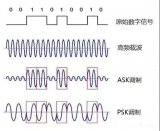

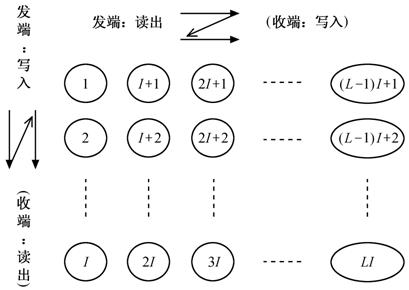

交織是一種極復雜的過程,是對糾錯過程的補充,交織的基本原理是將數字基帶信號按已定義了的規則進行“攪亂”,在接收端解調后再將這些“攪亂”的數據信號按相反的規則重新排列,使之恢復出原始的次序。

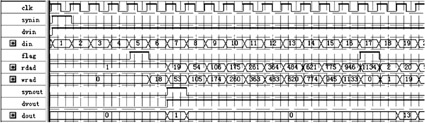

交織的過程是通過一組延時器來實現的,延時量是取樣周期的整數倍。延時器由隨機存儲器(RAM)構成。交織時將數據按嚴格的規定順序寫入RAM中;去交織時再按相反的順序從RAM中讀出。

- 數據信號(11834)

- 交織處理(5891)

相關推薦

Matlab和labview聯合做信號采集信號處理

有沒有人做過Matlab和labview聯合做信號采集信號處理的,例如labview把采集的信號存成txt,matlab讀txt并進行數據處理的,跪求指導

2019-05-09 16:53:51

基站側信號處理,比如交織、復用后同原來相比什么區別

基站側信號處理,比如交織、復用后同原來相比什么區別

基站信號處理,發射方向的信號處理過程有編碼、擴頻和調制。編碼包括:對M

2009-06-15 09:48:12 1263

1263

1263

1263FPGA無限通信技巧—位交織

,提高通信的可靠性。交織的越深,抗突發錯誤的能力也越強。位交織的本質是做矩陣的轉置運算,需要轉置的數據包括信息位和校驗位,在交織的過程中分兩步完成,步為檢驗位交織,第二步為列旋轉交織。

2023-05-06 10:02:09 260

260

260

260

一種交織器和解交織器的FPGA電路實現

一種交織器和解交織器的FPGA電路實現

交織和解交織是組合信道糾錯系統的一個重要環節,交織器和解交織器的實現方法有多種。本文利用Altera公司開發的Quartus軟

2009-02-08 23:21:59 1364

1364

1364

1364

根據MATLAB中的偽隨機交織器產生的交織圖案初始化到ROM的實驗

根據MATLAB中的偽隨機交織器產生的交織圖案初始化到ROM的實驗(嵌入式開發工程師報名)-根據MATLAB中的偽隨機交織器產生的交織圖案初始化到ROM

2021-07-30 16:19:57 13

13

13

13TURBO碼實時交織器的FPGA實現

介紹交織技術在Turbo碼中的作用及原理,按照螺旋交織器設計的要求,提出了一種交織器電路的設計方案。根據此設計思路得出交織器系統框圖,用硬件描述語言進行編程設計了交織

2010-08-06 15:01:09 27

27

27

27地面數字視頻廣播中內交織器與解內交織器設計

地面數字視頻廣播中內交織器與解內交織器設計同濟大學通信軟件及專用集成電路設計中心 200092 周加銃摘要:本文介紹了交織解交織的基本原理,針對地面數字視頻廣播系統

2009-12-14 11:11:25 41

41

41

41基于FPGA的改進型分組交織器的設計與實現

本文分析了交織器在Turbo碼中的重要作用,以及分組交織器存在的缺陷,提出了一種改進型分組交織器的設計與實現方法。該交織器具有算法簡單、易于實現、可適應不同數據幀長度傳

2010-07-28 17:26:27 15

15

15

15基于WCDMA的Turbo Codes交織器的設計與實現

介紹了Turbo碼和交織技術以及交織技術在Turbo碼中的重要作用,提出了一種交織器電路的設計思路, 進行了信道的性能仿真,并比較了其性能。根據此設計思路,用Verilog HDL語言設計了交

2010-07-02 17:02:16 22

22

22

22基于CPLD的短幀交織器設計實現

短幀數字通信系統適合采用矩陣式分組交織,本文以CDMA2000 語音傳輸標準下短幀為例,給出了具體的1216 的A 型分組比特交織器和解交織器。在實際中,該設計方案在不增加系統復雜度的

2011-05-14 15:28:53 27

27

27

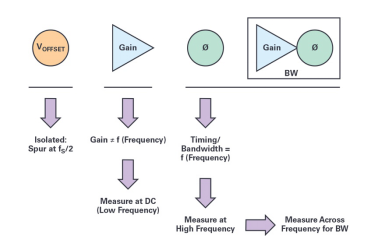

27交織型采樣ADC的基本原理

交織結構的優勢可惠及多個細分市場。交織型ADC最大好處是增加了帶寬,因為ADC的奈奎斯特帶寬更寬了。同樣,我們舉兩個100 MSPS ADC交織以實現200 MSPS采樣速率的例子。

2020-06-09 09:54:49 6095

6095

6095

6095

Turbo編碼中交織器的設計應用

Turbo 碼編譯碼技術是近年來新興的信道編碼技術,在其編解碼過程中,交織器起著很重要的作用,它是實現隨機,降低編碼相關性的核心。本文主要介紹了三種分組交織器的設計方

2009-09-18 10:23:25 31

31

31

31FPGA如何使用RAM分區循環移位法實現解交織器

本文分析了卷積交織和解交織的基本原理,然后采用Altera 的FPGA器件,用RAM分區循環移位法來實現解交織器。無論從理論上,還是從計算機仿真和綜合結果上來分析,都可以看出用這種方法來實現

2021-09-28 17:53:42 2120

2120

2120

2120交織多址接入系統信道容量證明

交織多址接入系統信道容量證明:交織多址接入系統(IDMA)是使用低速率碼并利用交織器區分用戶的多址接入系統,被認為是碼分多址(CDMA)的特例。IDMA省去專門的擴頻序列,通過迭代檢

2009-10-20 17:48:35 5

5

5

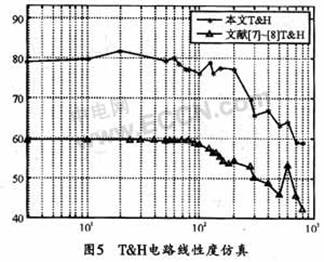

5用于時間交織ADC的高精度開環跟蹤保持電路設計

用于時間交織ADC的高精度開環跟蹤保持電路設計0 概述隨著數字通信系統的發展,高速數字處理系統對模擬信號和數字信號之間的轉換要求越來越高。目前高性

2010-04-09 10:43:08 762

762

762

762

利用FPGA技術實現數字通信中的交織器和解交織器

摘要:介紹用FPGA實現數字通信中的交、解交織器的一種比較通用的方案,詳細說明了設計中的一些問題及解決辦法。還介紹了一種實現FPGA中信號延時的方法。

2009-06-20 13:58:22 1000

1000

1000

1000

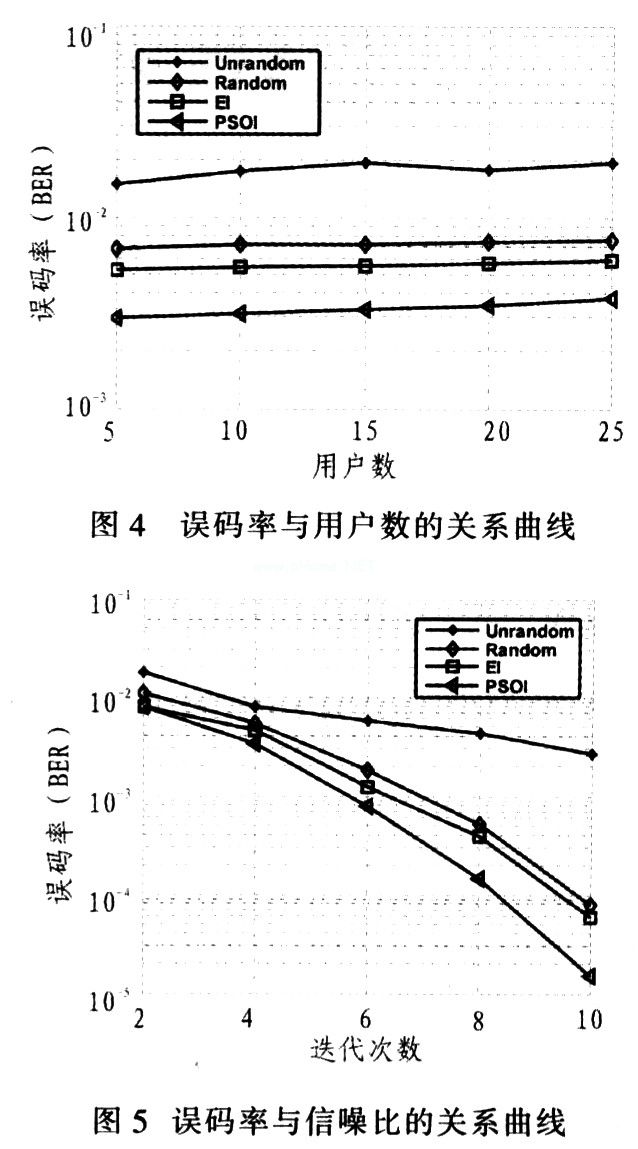

IDMA通信系統中的粒子群交織算法

在IDMA系統中,交織序列區分不同用戶,其產生是隨機且獨立的。但一些交織序列互相關系數接近1,這嚴重影響通信性能。因此提 出一種應用于IDMA通信系統中的粒子群交織算法。該

2010-12-29 16:49:56 11

11

11

11《數字信號處理》教學大綱

《數字信號處理》課屬于通信專業的專業基礎課,是通信專業學生在信號與系統基礎上必修的一門課程。本課主要講授數據信號處理的基本理念、基本算法和基本應用。數據信號處理理

2011-04-01 12:14:41 42

42

42

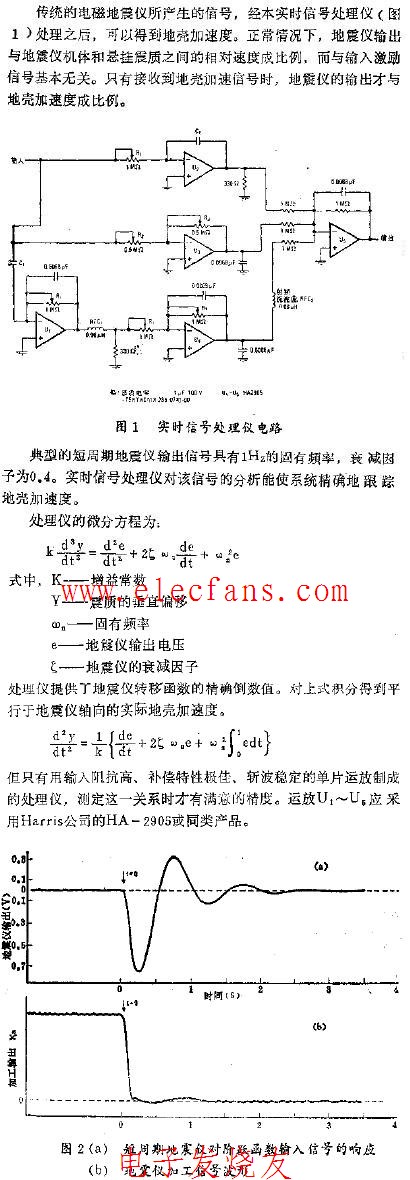

42數字信號處理概述說明

數字信號處理(DSP)是由一系列的數字或符號來表示這些信號的處理的過程的。數字信號處理與模擬信號處理屬于信號處理領域。DSP包括子域的音頻和語音信號處理,雷達和聲納信號處理,傳感器陣列處理,譜估計,統計信號處理,數字圖像處理,通信信號處理,生物醫學信號處理,地震數據處理等。

2021-04-06 11:05:26 27

27

27

27可變參數交織編碼器的FPGA實現

本文介紹了可變參數交織編碼器FPGA實現的圖形設計過程,給出了完整的設計思路和設計電路,并對設計進行了仿真實驗,從仿真圖中可以清楚的看出不同交織深度下的性能指標

2010-07-28 17:59:27 10

10

10

10IDMA通信系統中的粒子群交織算法

IDMA通信系統中的粒子群交織算法

引言 先進的接入技術碼分多址(CDMA)能夠有效利用帶寬,提高系統容量,應用廣泛。IDMA交織多址是一種特殊的CDMA

2009-12-19 10:25:43 1195

1195

1195

1195

ADSD3500: 淺色深度時間圖像信號處理器初步數據表 ADI

電子發燒友網為你提供ADI(ADI)ADSD3500: 淺色深度時間圖像信號處理器初步數據表相關產品參數、數據手冊,更有ADSD3500: 淺色深度時間圖像信號處理器初步數據表的引腳圖、接線圖、封裝

2023-10-11 18:53:26

RS編碼交織深度對氣象衛星數據傳輸的影響

S 編碼和交織技術是當前氣象衛星在數據傳輸過程中通常采取的、用來對抗信道深度衰落的措施,本文通過提取實際接收到的EOS 衛星數據,根據數據在RS 糾錯前、后的差異,從實際

2009-09-26 08:15:09 18

18

18

18信號處理的概念分析 數字信號處理三大基本步驟

信號處理的目的是:削弱信號中的多余內容;濾出混雜的噪聲和干擾;或者將信號變換成容易處理、傳輸、分析與識別的形式,以便后續的其它處理。

2018-09-07 08:54:00 22570

22570

22570

22570圖像交織RS碼設計及其C語言實現

針對圖像在打印傳輸或者掃描過程中,存在大量誤差,圖像發生失真。該文提出一種專門應用于圖像的交織里德所羅門碼設計方法,該方法是通過用交織編碼將圖像中突發錯誤離

2010-01-15 11:30:45 43

43

43

43基于Labview的信號處理編寫

使用Labview編寫程序完成信號分析處理,通過USB采集卡一端模擬信號,另一端采集信號,針對采集到的數據存儲,分析(加入濾波器)等!

2019-04-09 17:29:34 7192

7192

7192

7192信號處理器(DSP),信號處理器(DSP)是什么意思

信號處理器(DSP),信號處理器(DSP)是什么意思

DSP是(digital signal processor)的簡稱,是一種專門用來實現信號處理算法的微處理器芯片

2010-03-26 14:53:54 15277

15277

15277

15277基于DSP+FPGA的并行信號處理模塊設計

針對信號處理數據量大、實時性要求高的特點,從實際應用出發,設計了以雙DSP+FPGA為核心的并行信號處理模塊。為了滿足不同的信號處理任務需求,FPGA可以靈活地選擇與不同的DSP組成不同的信號處理

2017-11-17 06:11:40 2237

2237

2237

2237基于FPGA的信號調制系統的設計

對輸入的基帶碼流進行數字調制、頻域交織、差分調制以及正交頻分復用等一系列處理。所設計的信號調制系統能夠對輸入的基帶碼流進行實時處理,完成上述信號處理算法,并輸出數字音頻廣播的基帶信號。

2017-11-22 15:25:01 3674

3674

3674

3674LabVIEW教程之信號處理與分析

數字信號在我們周圍無所不在。因為數字信號具有高保真、低噪聲和便于信號處理的優點,所以得到了廣泛的應用,例如電話公司使用數字信號傳輸語音,廣播、電視和高保真音響系統也都在逐漸數字化。太空中的衛星將測得數據

2019-12-06 14:02:19 170

170

170

170探究FPGA的多速率信號處理技術

信號處理 多速率信號處理,是指對同時存在兩個以上數據速率的系統進行信號處理。在軟件無線電(SDR)中,多速率技術得到普遍應用。在實際系統中,需要處理的數據量越來越大,并且對處理速度的要求越來越高,經常是Gb/s級別。多速率技

2021-06-01 11:02:19 2537

2537

2537

2537

基于FPGA的數字磁通門信號處理

本文針對磁通門信號采集與處理的具體特點,對基于FPGA的磁通門數字信號處理系統進行了研究。該系統采用A/D轉換器對磁通門輸出信號進行采樣,采樣后的數據通過FPGA進行數據處理,再

2010-07-21 17:24:58 25

25

25

25數字信號處理簡介

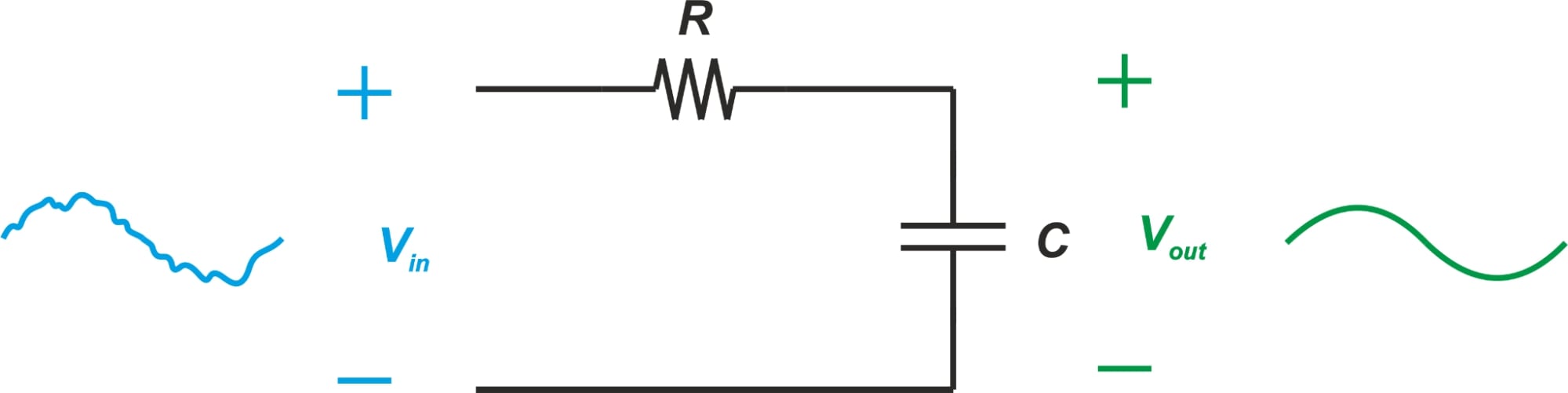

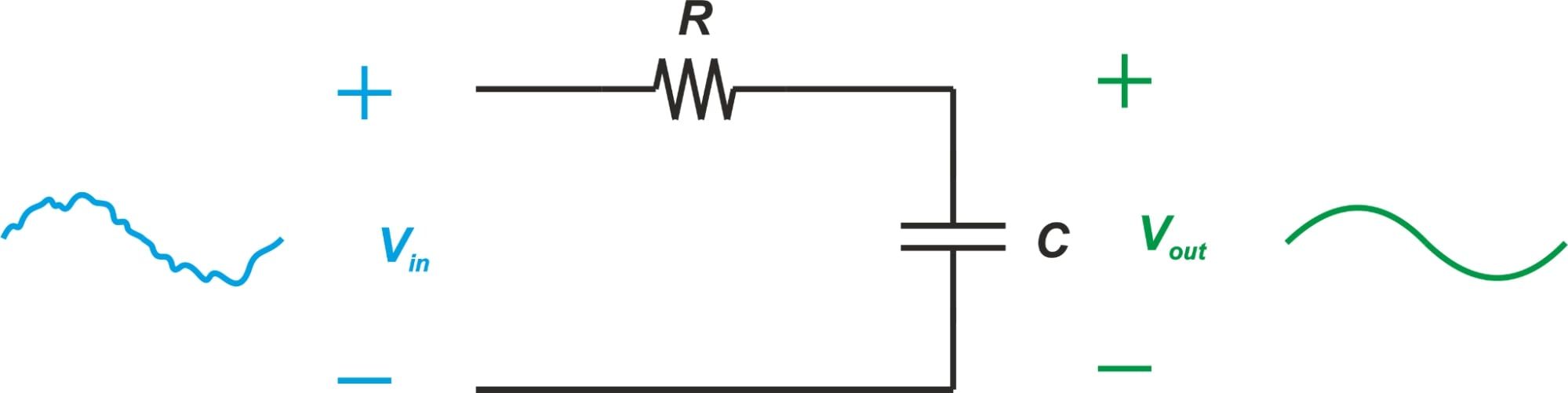

本文概述了什么是 DSP、它是如何工作的以及它可以提供哪些優勢。 為了了解DSP的優勢,我們首先看一下傳統的信號處理方法,即模擬信號處理。 數字信號處理(DSP)涉及開發可用于以特定方式增強信號或

2023-05-03 14:13:00 1416

1416

1416

1416

數字信號處理的簡介

本文概述了什么是 DSP、它是如何工作的以及它可以提供哪些優勢。 為了了解DSP的優勢,我們首先看一下傳統的信號處理方法,即模擬信號處理。 數字信號處理(DSP)涉及開發可用于以特定方式增強信號或

2023-01-27 17:27:00 674

674

674

674

什么是信號處理?如何進行數字信號處理呢?

什么是信號處理?如何進行數字信號處理呢?

在我們的周圍存在著為數眾多的"信號"。如:從茫茫宇宙中的天體發出的微弱電波信號,移動電話發出

2010-03-06 10:13:51 2919

2919

2919

2919汽車電子元件的電磁兼容線路交織干擾

面對供電線路以及信號線路和敏感元件線路上由電子元件和電氣設備構件引起的供電網的交織干擾,并考慮到這些直接的或間接的(例如開關觸點、繼電器觸點或整流器執行元件/敏感元件

2011-12-08 16:42:14 52

52

52

52基于FPGA的振動信號采集處理系統設計并實際驗證

為數字信號送入FPGA,在FPGA處理設計中利用數據流控制方法并行實現了信號的采樣和處理,并在數據存儲和訪問過程中采用時鐘時標方法判斷信號采樣過程中的數據丟失情況,有效提高了振動信號處理的實時性及可靠性。

2017-11-18 05:26:02 2849

2849

2849

2849

信號處理系統實現數據轉換器的接地

目前的信號處理系統一般需要混合信號器件, 例如模數轉換器(ADC)、數模轉換器(DAC)和快速數字信號處理器(DSP)。由于需要處理寬動態范圍的模擬信號, 因此擁有高性能ADC和DAC顯得更加

2021-05-29 11:19:14 1

1

1

1基于FPGA的數字磁通門信號處理

本文針對磁通門信號采集與處理的具體特點,對基于FPGA的磁通門數字信號處理系統進行了研究。該系統采用A/D轉換器對磁通門輸出信號進行采樣,采樣后的數據通過FPGA進行數據

2009-12-23 15:09:09 14

14

14

14振弦信號轉無線485步驟信號采集、處理、轉換和發送

。 數模轉換:將處理后的信號轉換為數字信號。 通信協議轉換:將數字信號通過轉換模塊轉換為無線485通信所需的協議,例如Modbus RTU協議。 信號發送:將轉換后的信號通過無線485模塊發送到接收端。 數據接收:接收端使用相應的無線485模塊接收數

2023-08-08 17:46:49 183

183

183

183數字信號處理器概論

作為數字信號處理的一個實際任務就是要求能夠快速、高效、實時完成處理任務,這就要通過通用或專用的數字信號處理器來完成。因此,數字信號處理器是用來完成數字信號處理任務的一個軟、硬件環境和硬件平臺。

2023-08-07 16:58:08 318

318

318

318隨機信號處理初步

隨機信號處理初步:本章介紹隨機信號處理的一些基本概念,并且借助Matlab,給出了一些譜估計的方法。在許多信號處理的場合,信號是確定性的,例如電力系統里面的正弦波,

2009-11-24 09:10:30 33

33

33

33FPGA同步轉換FPGA對輸入信號的處理

的verilog異步fifo設計,仿真(代碼供參考)異步fifo適合處理不同時鐘域之間傳輸的數據組,但有時不同時鐘域之間僅僅傳遞脈沖,異步fifo就顯的有點大材小用的,因此單信號的跨時鐘域處理通常有, ? ? ? ? 兩級寄存器串聯。 ? ? ? ? 脈沖同步器。

2023-02-17 11:10:08 330

330

330

330 電子發燒友App

電子發燒友App

評論