幾種常用邏輯電平電路的特點及應用

幾種常用邏輯電平電路的特點及應用

標簽/分類:

在通用的電子器件設備中,TTL和CMOS電路的應用非常廣泛。但是面對現在系統日益復雜,傳輸的數據量越來越大,實時性要求越來越高,傳輸距離越來越長的發展趨勢,掌握高速數據傳輸的邏輯電平知識和設計能力就顯得更加迫切了。

1 幾種常用高速邏輯電平

1.1LVDS電平

LVDS(Low Voltage Differential Signal)即低電壓差分信號,LVDS接口又稱RS644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。

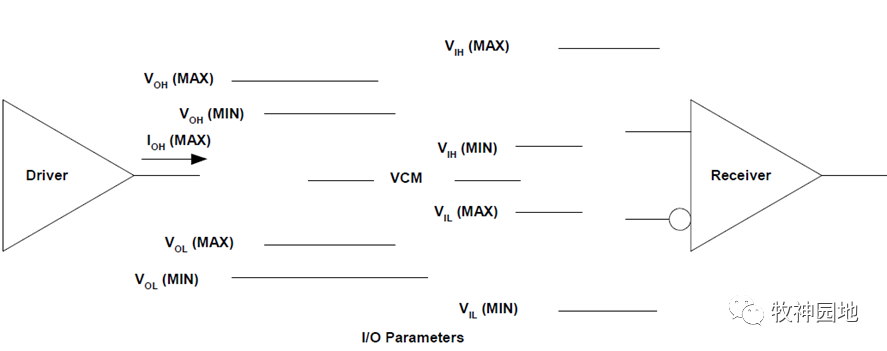

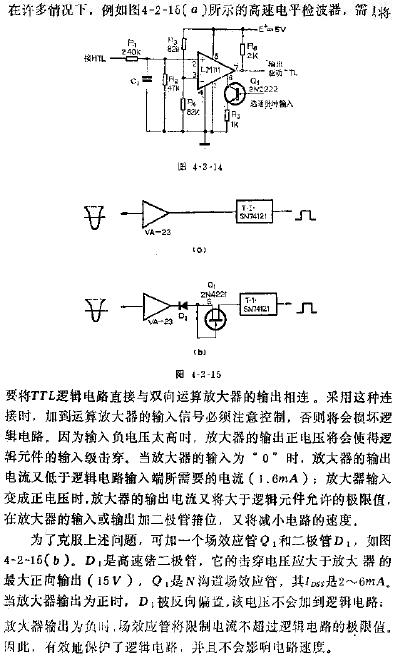

LVDS的典型工作原理如圖1所示。最基本的LVDS器件就是LVDS驅動器和接收器。LVDS的驅動器由驅動差分線對的電流源組成,電流通常為3.5 mA。LVDS接收器具有很高的輸入阻抗,因此驅動器輸出的大部分電流都流過100 Ω的匹配電阻,并在接收器的輸入端產生大約350 mV的電壓。當驅動器翻轉時,它改變流經電阻的電流方向,因此產生有效的邏輯“1”和邏輯“0”狀態。

圖1LVDS驅動器與接收器互連示意

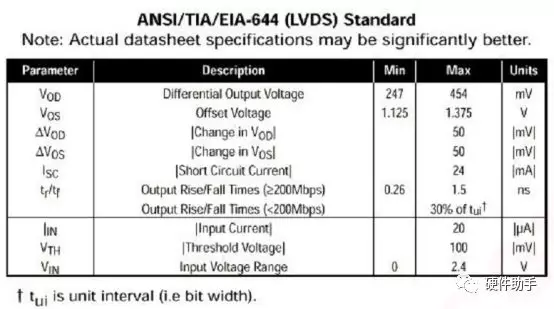

LVDS技術在兩個標準中被定義:ANSI/TIA/EIA644 (1995年11月通過)和IEEE P1596.3 (1996年3月通過)。這兩個標準中都著重定義了LVDS的電特性,包括:

① 低擺幅(約為350 mV)。低電流驅動模式意味著可實現高速傳輸。ANSI/TIA/EIA644建議了655 Mb/s的最大速率和1.923 Gb/s的無失真通道上的理論極限速率。

② 低壓擺幅。恒流源電流驅動,把輸出電流限制到約為3.5 mA左右,使跳變期間的尖峰干擾最小,因而產生的功耗非常小。這允許集成電路密度的進一步提高,即提高了PCB板的效能,減少了成本。

③ 具有相對較慢的邊緣速率(dV/dt約為0.300 V/0.3 ns,即為1 V/ns),同時采用差分傳輸形式,使其信號噪聲和EMI都大為減少,同時也具有較強的抗干擾能力。

所以,LVDS具有高速、超低功耗、低噪聲和低成本的優良特性。

LVDS的應用模式可以有四種形式:

① 單向點對點(pointtopoint),這是典型的應用模式。

② 雙向點對點(pointtopoint),能通過一對雙絞線實現雙向的半雙工通信。可以由標準的LVDS的驅動器和接收器構成;但更好的辦法是采用總線LVDS驅動器,即BLVDS,這是為總線兩端都接負載而設計的。

③ 多分支形式(multidrop),即一個驅動器連接多個接收器。當有相同的數據要傳給多個負載時,可以采用這種應用形式。

④ 多點結構(multipoint)。此時多點總線支持多個驅動器,也可以采用BLVDS驅動器。它可以提供雙向的半雙工通信,但是在任一時刻,只能有一個驅動器工作。因而發送的優先權和總線的仲裁協議都需要依據不同的應用場合,選用不同的軟件協議和硬件方案。

為了支持LVDS的多點應用,即多分支結構和多點結構,2001年新推出的多點低壓差分信號(MLVDS)國際標準ANSI/TIA/EIA 8992001,規定了用于多分支結構和多點結構的MLVDS器件的標準,目前已有一些MLVDS器件面世。

LVDS技術的應用領域也日漸普遍。在高速系統內部、系統背板互連和電纜傳輸應用中,驅動器、接收器、收發器、并串轉換器/串并轉換器以及其他LVDS 器件的應用正日益廣泛。接口芯片供應商正推進LVDS作為下一代基礎設施的基本構造模塊,以支持手機基站、中心局交換設備以及網絡主機和計算機、工作站之間的互連。

1.2ECL電平

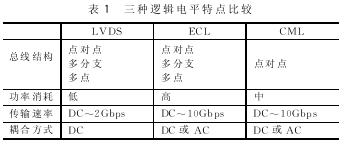

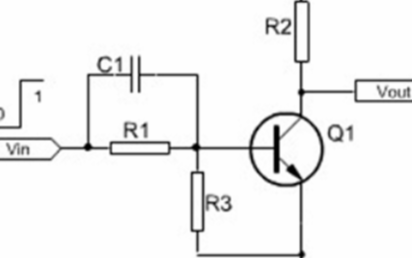

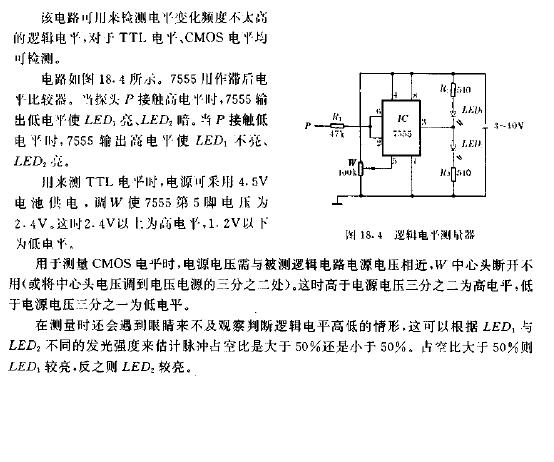

ECL(EmitterCoupled Logic)即射極耦合邏輯,是帶有射隨輸出結構的典型輸入輸出接口電路,如圖2所示。

圖2ECL驅動器與接收器連接示意

ECL電路的最大特點是其基本門電路工作在非飽和狀態,因此ECL又稱為非飽和性邏輯。也正因為如此,ECL電路的最大優點是具有相當高的速度。這種電路的平均延遲時間可達幾個ns數量級甚至更少。傳統的ECL以VCC為零電壓,VEE為-5.2 V電源,VOH=VCC-0.9 V=-0.9 V,VOL=VCC-1.7 V=-1.7 V,所以ECL電路的邏輯擺幅較小(僅約0.8 V)。當電路從一種狀態過渡到另一種狀態時,對寄生電容的充放電時間將減少,這也是ECL電路具有高開關速度的重要原因。另外,ECL電路是由一個差分對管和一對射隨器組成的,所以輸入阻抗大,輸出阻抗小,驅動能力強,信號檢測能力高,差分輸出,抗共模干擾能力強;但是由于單元門的開關管對是輪流導通的,對整個電路來講沒有“截止”狀態,所以電路的功耗較大。

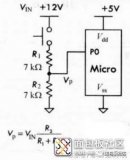

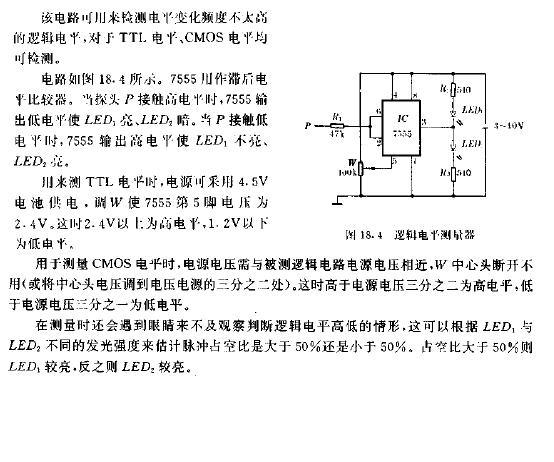

如果省掉ECL電路中的負電源,采用正電源的系統(+5 V),可將VCC接到正電源而VEE接到零點。這樣的電平通常被稱為PECL(Positive Emitter Coupled Logic)。如果采用+3.3 V供電,則稱為LVPECL。當然,此時高低電平的定義也是不同的。它的電路如圖3、4所示。其中,輸出射隨器工作在正電源范圍內,其電流始終存在。這樣有利于提高開關速度,而且標準的輸出負載是接50Ω至VCC-2 V的電平上。

在使用PECL 電路時要注意加電源去耦電路,以免受噪聲的干擾。輸出采用交流耦合還是直流耦合,對負載網絡的形式將會提出不同的需求。直流耦合的接口電路有兩種工作模式:其一,對應于近距離傳送的情況,采用發送端加到地偏置電阻,接收端加端接電阻模式;其二,對應于較遠距離傳送的情況,采用接收端通過電阻對提供截止電平VTT 和50 Ω的匹配負載的模式。以上都有標準的工作模式可供參考,不必贅述。對于交流耦合的接口電路,也有一種標準工作模式,即發送端加到地偏置電阻,耦合電容靠近發送端放置,接收端通過電阻對提供共模電平VBB 和50 Ω的匹配負載的模式。

(P)ECL是高速領域內一種十分重要的邏輯電路,它的優良特性使它廣泛應用于高速計算機、高速計數器、數字通信系統、雷達、測量儀器和頻率合成器等方面。

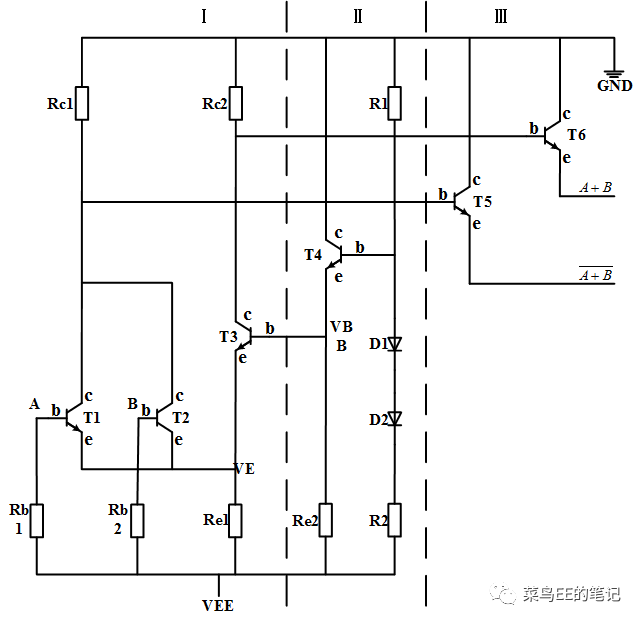

1.3CML電平

CML電平是所有高速數據接口中最簡單的一種。其輸入和輸出是匹配好的,減少了外圍器件,適合于更高頻段工作。它的輸出結構如圖5所示。

CML 接口典型的輸出電路是一個差分對形式。該差分對的集電極電阻為50 Ω,輸出信號的高低電平切換是靠共發射極差分對的開關控制的。差分對的發射極到地的恒流源典型值為16 mA。假定CML的輸出負載為一個50 Ω上拉電阻,則單端CML輸出信號的擺幅為VCC~VCC-0.4 V。在這種情況下,差分輸出信號擺幅為800 mV。信號擺幅較小,所以功耗很低,CML接口電平功耗低于ECL的1/2,而且它的差分信號接口和 ECL、LVDS電平具有類似的特點。

CML到CML之間的連接分兩種情況:當收發兩端的器件使用相同的電源時,CML到CML可以采用直流耦合方式,不用加任何器件;當收發兩端器件采用不同電源時,一般要考慮交流耦合, 中間加耦合電容(注意這時選用的耦合電容要足夠大,以避免在較長連0 或連1 情況出現時,接收端差分電壓變小)。

圖3PECL輸出結構

圖4PECL輸入結構

圖5CML輸出結構

但它也有些不足,即由于自身驅動能力有限,CML更適于芯片間較短距離的連接,而且CML接口實現方式不同用戶間差異較大,所以現有器件提供CML接口的數目還不是非常多。

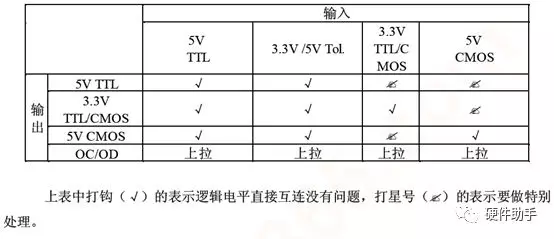

2 各種邏輯電平之間的比較和互連轉化

2.1各種邏輯電平之間的比較

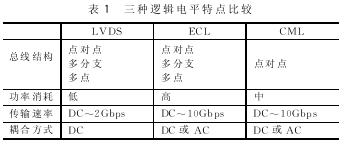

這幾種高速邏輯電平在目前都有應用,但它們在總線結構、功率消耗、傳輸速率、耦合方式等方面都各有特點。為了便于應用比較,現歸納以上三類電平各方面的特點,如表1所列。

2.2各種邏輯電平之間的互連

這三類電平在互連時,首先要考慮的就是它們的電平大小和電平擺幅各不一樣,必須使輸出電平經過中間的電阻轉換網絡后落在輸入電平的有效范圍內。各種電平的擺幅比較如圖6所示。

圖6各種高速電平的偏置擺幅比較

其次,電阻網絡要考慮到匹配問題。例如我們知道,當負載是50 Ω接到VCC-2 V 時,LVPECL 的輸出性能是最優的,因此考慮的電阻網絡應該與最優負載等效;LVDS 的輸入差分阻抗為100 Ω,或者每個單端到虛擬地為50 Ω,該阻抗不提供直流通路,這里意味著LVDS輸入交流阻抗與直流阻抗不等,電阻值的選取還必須根據直流或交流耦合的不同情況作不同的選取。另外,電阻網絡還必須與傳輸線匹配。

另一個問題是電阻網絡需要在功耗和速度方面折中考慮:既允許電路在較高的速度下工作,又盡量不出現功耗過大。

下面以圖7所示的LVPECL到LVDS的直流耦合連接為例,來說明以上所討論的原則。

圖7LVPECL到LVDS的直流耦合連接及等效電路

傳輸線阻抗匹配原則:

Z≈R1//(R2+R3)

根據LVPCEL輸出最優性能:

降低LVPECL擺幅以適應LVDS的輸入范圍:Gain=R3/(R2+R3)

根據實際情況,選擇滿足以上約束條件的電阻值,例如當傳輸線特征阻抗為50 Ω時,可取R1=120 Ω,R2=58 Ω,R3=20 Ω即能完成互連。

由于LVDS 通常用作并聯數據的傳輸,數據速率為155 Mbps、622 Mbps或1.25 Gbps;而CML 常用來做串行數據的傳輸,數據速率為2.5 Gbps或10 Gbps。一般情況下,在傳輸系統中沒有CML和LVDS 的互連問題。

結語

本文粗淺地討論了幾種目前應用較多的高速電平技術。復雜高速的通信系統背板,大屏幕平板顯示系統,海量數據的實時傳輸等等都需要采用新高速電平技術。隨著社會的發展,新高速電平技術必將得到越來越廣泛的應用。

參考文獻

1 武斌,夏宇聞. 數字視頻信號的長線傳輸. 電子技術應用, 2003(10)

2 National Semiconductor. LVDS Owners Manual. 2000

3 趙忠文,曾巒,熊偉. LVDS技術分析和設計應用. 指揮技術學院學報, 2001(12)

4 Differential PECL/ECL/LVPECL/LVECL Clock and Data Driver. 2002 Maxim Integrated Products

1 幾種常用高速邏輯電平

1.1LVDS電平

LVDS(Low Voltage Differential Signal)即低電壓差分信號,LVDS接口又稱RS644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。

LVDS的典型工作原理如圖1所示。最基本的LVDS器件就是LVDS驅動器和接收器。LVDS的驅動器由驅動差分線對的電流源組成,電流通常為3.5 mA。LVDS接收器具有很高的輸入阻抗,因此驅動器輸出的大部分電流都流過100 Ω的匹配電阻,并在接收器的輸入端產生大約350 mV的電壓。當驅動器翻轉時,它改變流經電阻的電流方向,因此產生有效的邏輯“1”和邏輯“0”狀態。

圖1LVDS驅動器與接收器互連示意

LVDS技術在兩個標準中被定義:ANSI/TIA/EIA644 (1995年11月通過)和IEEE P1596.3 (1996年3月通過)。這兩個標準中都著重定義了LVDS的電特性,包括:

① 低擺幅(約為350 mV)。低電流驅動模式意味著可實現高速傳輸。ANSI/TIA/EIA644建議了655 Mb/s的最大速率和1.923 Gb/s的無失真通道上的理論極限速率。

② 低壓擺幅。恒流源電流驅動,把輸出電流限制到約為3.5 mA左右,使跳變期間的尖峰干擾最小,因而產生的功耗非常小。這允許集成電路密度的進一步提高,即提高了PCB板的效能,減少了成本。

③ 具有相對較慢的邊緣速率(dV/dt約為0.300 V/0.3 ns,即為1 V/ns),同時采用差分傳輸形式,使其信號噪聲和EMI都大為減少,同時也具有較強的抗干擾能力。

所以,LVDS具有高速、超低功耗、低噪聲和低成本的優良特性。

LVDS的應用模式可以有四種形式:

① 單向點對點(pointtopoint),這是典型的應用模式。

② 雙向點對點(pointtopoint),能通過一對雙絞線實現雙向的半雙工通信。可以由標準的LVDS的驅動器和接收器構成;但更好的辦法是采用總線LVDS驅動器,即BLVDS,這是為總線兩端都接負載而設計的。

③ 多分支形式(multidrop),即一個驅動器連接多個接收器。當有相同的數據要傳給多個負載時,可以采用這種應用形式。

④ 多點結構(multipoint)。此時多點總線支持多個驅動器,也可以采用BLVDS驅動器。它可以提供雙向的半雙工通信,但是在任一時刻,只能有一個驅動器工作。因而發送的優先權和總線的仲裁協議都需要依據不同的應用場合,選用不同的軟件協議和硬件方案。

為了支持LVDS的多點應用,即多分支結構和多點結構,2001年新推出的多點低壓差分信號(MLVDS)國際標準ANSI/TIA/EIA 8992001,規定了用于多分支結構和多點結構的MLVDS器件的標準,目前已有一些MLVDS器件面世。

LVDS技術的應用領域也日漸普遍。在高速系統內部、系統背板互連和電纜傳輸應用中,驅動器、接收器、收發器、并串轉換器/串并轉換器以及其他LVDS 器件的應用正日益廣泛。接口芯片供應商正推進LVDS作為下一代基礎設施的基本構造模塊,以支持手機基站、中心局交換設備以及網絡主機和計算機、工作站之間的互連。

1.2ECL電平

ECL(EmitterCoupled Logic)即射極耦合邏輯,是帶有射隨輸出結構的典型輸入輸出接口電路,如圖2所示。

圖2ECL驅動器與接收器連接示意

ECL電路的最大特點是其基本門電路工作在非飽和狀態,因此ECL又稱為非飽和性邏輯。也正因為如此,ECL電路的最大優點是具有相當高的速度。這種電路的平均延遲時間可達幾個ns數量級甚至更少。傳統的ECL以VCC為零電壓,VEE為-5.2 V電源,VOH=VCC-0.9 V=-0.9 V,VOL=VCC-1.7 V=-1.7 V,所以ECL電路的邏輯擺幅較小(僅約0.8 V)。當電路從一種狀態過渡到另一種狀態時,對寄生電容的充放電時間將減少,這也是ECL電路具有高開關速度的重要原因。另外,ECL電路是由一個差分對管和一對射隨器組成的,所以輸入阻抗大,輸出阻抗小,驅動能力強,信號檢測能力高,差分輸出,抗共模干擾能力強;但是由于單元門的開關管對是輪流導通的,對整個電路來講沒有“截止”狀態,所以電路的功耗較大。

如果省掉ECL電路中的負電源,采用正電源的系統(+5 V),可將VCC接到正電源而VEE接到零點。這樣的電平通常被稱為PECL(Positive Emitter Coupled Logic)。如果采用+3.3 V供電,則稱為LVPECL。當然,此時高低電平的定義也是不同的。它的電路如圖3、4所示。其中,輸出射隨器工作在正電源范圍內,其電流始終存在。這樣有利于提高開關速度,而且標準的輸出負載是接50Ω至VCC-2 V的電平上。

在使用PECL 電路時要注意加電源去耦電路,以免受噪聲的干擾。輸出采用交流耦合還是直流耦合,對負載網絡的形式將會提出不同的需求。直流耦合的接口電路有兩種工作模式:其一,對應于近距離傳送的情況,采用發送端加到地偏置電阻,接收端加端接電阻模式;其二,對應于較遠距離傳送的情況,采用接收端通過電阻對提供截止電平VTT 和50 Ω的匹配負載的模式。以上都有標準的工作模式可供參考,不必贅述。對于交流耦合的接口電路,也有一種標準工作模式,即發送端加到地偏置電阻,耦合電容靠近發送端放置,接收端通過電阻對提供共模電平VBB 和50 Ω的匹配負載的模式。

(P)ECL是高速領域內一種十分重要的邏輯電路,它的優良特性使它廣泛應用于高速計算機、高速計數器、數字通信系統、雷達、測量儀器和頻率合成器等方面。

1.3CML電平

CML電平是所有高速數據接口中最簡單的一種。其輸入和輸出是匹配好的,減少了外圍器件,適合于更高頻段工作。它的輸出結構如圖5所示。

CML 接口典型的輸出電路是一個差分對形式。該差分對的集電極電阻為50 Ω,輸出信號的高低電平切換是靠共發射極差分對的開關控制的。差分對的發射極到地的恒流源典型值為16 mA。假定CML的輸出負載為一個50 Ω上拉電阻,則單端CML輸出信號的擺幅為VCC~VCC-0.4 V。在這種情況下,差分輸出信號擺幅為800 mV。信號擺幅較小,所以功耗很低,CML接口電平功耗低于ECL的1/2,而且它的差分信號接口和 ECL、LVDS電平具有類似的特點。

CML到CML之間的連接分兩種情況:當收發兩端的器件使用相同的電源時,CML到CML可以采用直流耦合方式,不用加任何器件;當收發兩端器件采用不同電源時,一般要考慮交流耦合, 中間加耦合電容(注意這時選用的耦合電容要足夠大,以避免在較長連0 或連1 情況出現時,接收端差分電壓變小)。

圖3PECL輸出結構

圖4PECL輸入結構

圖5CML輸出結構

但它也有些不足,即由于自身驅動能力有限,CML更適于芯片間較短距離的連接,而且CML接口實現方式不同用戶間差異較大,所以現有器件提供CML接口的數目還不是非常多。

2 各種邏輯電平之間的比較和互連轉化

2.1各種邏輯電平之間的比較

這幾種高速邏輯電平在目前都有應用,但它們在總線結構、功率消耗、傳輸速率、耦合方式等方面都各有特點。為了便于應用比較,現歸納以上三類電平各方面的特點,如表1所列。

2.2各種邏輯電平之間的互連

這三類電平在互連時,首先要考慮的就是它們的電平大小和電平擺幅各不一樣,必須使輸出電平經過中間的電阻轉換網絡后落在輸入電平的有效范圍內。各種電平的擺幅比較如圖6所示。

圖6各種高速電平的偏置擺幅比較

其次,電阻網絡要考慮到匹配問題。例如我們知道,當負載是50 Ω接到VCC-2 V 時,LVPECL 的輸出性能是最優的,因此考慮的電阻網絡應該與最優負載等效;LVDS 的輸入差分阻抗為100 Ω,或者每個單端到虛擬地為50 Ω,該阻抗不提供直流通路,這里意味著LVDS輸入交流阻抗與直流阻抗不等,電阻值的選取還必須根據直流或交流耦合的不同情況作不同的選取。另外,電阻網絡還必須與傳輸線匹配。

另一個問題是電阻網絡需要在功耗和速度方面折中考慮:既允許電路在較高的速度下工作,又盡量不出現功耗過大。

下面以圖7所示的LVPECL到LVDS的直流耦合連接為例,來說明以上所討論的原則。

圖7LVPECL到LVDS的直流耦合連接及等效電路

傳輸線阻抗匹配原則:

Z≈R1//(R2+R3)

根據LVPCEL輸出最優性能:

降低LVPECL擺幅以適應LVDS的輸入范圍:Gain=R3/(R2+R3)

根據實際情況,選擇滿足以上約束條件的電阻值,例如當傳輸線特征阻抗為50 Ω時,可取R1=120 Ω,R2=58 Ω,R3=20 Ω即能完成互連。

由于LVDS 通常用作并聯數據的傳輸,數據速率為155 Mbps、622 Mbps或1.25 Gbps;而CML 常用來做串行數據的傳輸,數據速率為2.5 Gbps或10 Gbps。一般情況下,在傳輸系統中沒有CML和LVDS 的互連問題。

結語

本文粗淺地討論了幾種目前應用較多的高速電平技術。復雜高速的通信系統背板,大屏幕平板顯示系統,海量數據的實時傳輸等等都需要采用新高速電平技術。隨著社會的發展,新高速電平技術必將得到越來越廣泛的應用。

參考文獻

1 武斌,夏宇聞. 數字視頻信號的長線傳輸. 電子技術應用, 2003(10)

2 National Semiconductor. LVDS Owners Manual. 2000

3 趙忠文,曾巒,熊偉. LVDS技術分析和設計應用. 指揮技術學院學報, 2001(12)

4 Differential PECL/ECL/LVPECL/LVECL Clock and Data Driver. 2002 Maxim Integrated Products

電子發燒友App

電子發燒友App

評論