Altera MAX+plus II 介紹

一、軟件功能簡介

MAX+plusⅡ(Multiple Array and Programming Logic User System)開發(fā)工具

是美國Altera 公司推出的一種EDA 工具,具有靈活高效,使用便捷,易學(xué)易用

的特點(diǎn)。Altera 公司在推出各種CPLD 和FPGA 的同時(shí)也在不斷地升級相應(yīng)的開

發(fā)工具軟件,已從早期的第一代A+plus、第二代MAX+plus 發(fā)展到目前的第三

代MAX+plus II 和第四代Quartus。使用MAX+plus Ⅱ軟件,設(shè)計(jì)者無需精通器

件內(nèi)部的復(fù)雜結(jié)構(gòu),只需熟悉所用的設(shè)計(jì)輸入工具,如硬件描述語言、原理圖等

進(jìn)行輸入,MAX+plusⅡ自動(dòng)將設(shè)計(jì)轉(zhuǎn)換成目標(biāo)文件下載到器件中去。

MAX+plusⅡ開發(fā)系統(tǒng)具有以下特點(diǎn)。

(1)多平臺(tái)系統(tǒng) MAX+plusⅡ的設(shè)計(jì)輸入、處理與校驗(yàn)功能一起提供了全集

成化的可編程開發(fā)工具,可以加快動(dòng)態(tài)調(diào)試,縮短開發(fā)周期。

(2)開放的界面 MAX+plusⅡ可與其它工業(yè)標(biāo)準(zhǔn)的設(shè)計(jì)輸入、綜合和校驗(yàn)工

具鏈接。具有EDIF,VHDL,Verilog HDL 以及其他的網(wǎng)表接口,便于與許多公

司的EDA 工具接口,包括Cadence,Mentor,Synopsys,Synplicity,Viewlogic

等公司提供的EDA 工具的接口。

(3)模塊組合式工具軟件MAX+plusⅡ具有一個(gè)完整的可編程邏輯設(shè)計(jì)環(huán)境,

包括設(shè)計(jì)輸入、設(shè)計(jì)處理、設(shè)計(jì)校驗(yàn)仿真和下載編程四個(gè)模塊,設(shè)計(jì)者可以按設(shè)

計(jì)流程選擇工作模塊。

(4)與結(jié)構(gòu)無關(guān) MAX+plusⅡ支持Altera 的Classic、MAX5000、MAX7000、

FLEX8000、FLEXlOK 等可編程器件系列,提供工業(yè)界中唯一真正與結(jié)構(gòu)無關(guān)的

可編程邏輯設(shè)計(jì)環(huán)境。

(5)硬件描述語言 MAX+plusⅡ支持各種HDL 硬件設(shè)計(jì)輸入語言,包括VHDL、

VerilogHDL 和Altera 的硬件描述語言AHDL。

二、軟件的安裝使用說明

MAX+plus II 教學(xué)版軟件是免費(fèi)的,你需要到Altera 公司的網(wǎng)頁去申請一

個(gè)License.dat 授權(quán)文件(軟件安裝部分有詳細(xì)說明),也可使用隨機(jī)光盤的

License.dat 授權(quán)文件(此文件就在光盤中的Altera MAX+plusII 10.0 文件下)。其

商業(yè)版需要到Altera 公司的中國代理購買,它帶有一個(gè)軟件狗,需置于計(jì)算機(jī)的

并行口上。教學(xué)版軟件同樣支持功能仿真和時(shí)序分析,并且同樣支持VHDL 語

言設(shè)計(jì)。該軟件可運(yùn)行在Windows9X/2000/NT 及WindowsXP 操作系統(tǒng)下。

MAX+plusII 10.0 版本推薦PC 機(jī)的配置如為:333MHz 奔騰以上CPU、64M 以

上有效內(nèi)存、600M 以上的硬盤。

1、 軟件的安裝

注意:本安裝過程以10.0 版本為例介紹,其它版本安裝過程類似。

⑴ 將光盤插入PC 機(jī)光驅(qū),假定您的光驅(qū)號(hào)為G:,

⑵ 運(yùn)行G:\MAX+plusII 10.0\setup.exe 文件,按提示進(jìn)行安裝;

⑶ 安裝過程中閱讀完授權(quán)窗口信息后,選擇YES 接受協(xié)議,再選擇適當(dāng)?shù)陌惭b

方式,教學(xué)版軟件請選擇: full installation 模式安裝,若改變安裝目錄及路徑請按

Browse 按鈕修改,一般選擇默認(rèn)安裝即可。軟件安裝完畢后,readme 文件將自

動(dòng)出現(xiàn),它包含一些重要信息,請仔細(xì)閱讀,該軟件要通過License 文件設(shè)置以

后方可使用(見下一節(jié)介紹)。

2、軟件的第一次使用與設(shè)置

MAX+plusII 10.0 軟件安裝完畢后,第一次運(yùn)行軟件必須進(jìn)行l(wèi)icense.dat 文件的

設(shè)置,否則其大部分功能用戶不能正常使用。下面我們將license.dat 文件的安裝

方法簡單介紹如下。

1)、將光盤里隨機(jī)附送的license.dat 文件拷貝至安裝后的MAX+plus2 軟件包根

目錄下。注意:license.dat 文件來自于Altera 網(wǎng)上授權(quán)或代理商提供。也可使用

隨機(jī)光盤提供的License.dat 授權(quán)文件(此文件就在光盤中的Altera MAX+plusII

10.0 文件夾下)。

2)、點(diǎn)擊windows 程序組下的altera\ MAX+plusII 10.0 ,啟動(dòng)本軟件。注意:第一次啟動(dòng)軟件會(huì)有幾個(gè)對話窗口,提示沒有安裝License 文件或軟件狗,并附

有其公司網(wǎng)址及如何申請license 授權(quán)文件等詳細(xì)說明。

3)、軟件啟動(dòng)以后選擇主菜單欄的Option \License Setup 選項(xiàng),彈出如下對話框,

點(diǎn)擊 “Browse”;

4)、通過瀏覽,在如下對話框中指出您保存的License.dat 文件的所在硬盤位置

(路徑),點(diǎn)擊OK 確認(rèn)即可。這樣您的MAX+plusII 軟件就可以正常使用了。

license.Dat 文件生效后,對話框底部的System lnfo 中就有你的硬盤ID 信息了,

如下圖所示。至此您已成功地完成了整個(gè)軟件的安裝。

說明:一般免費(fèi)注冊申請的License.dat 文件只能用六個(gè)月的時(shí)間,如果到期的

話,您可以用同樣的方法再次申請,如果您使用的通用License.dat 文件(此文件

就在光盤中的Altera MAX+plusII 10.0 文件下),就不存在上述問題了,如果您在

安裝和使用本軟件中遇到問題,請及時(shí)與我們聯(lián)系。

三、可編程邏輯器件設(shè)計(jì)流程簡介

可編程邏輯器件CPLD/FPGA 的設(shè)計(jì)是指利用開發(fā)軟件和編程工具對器件

進(jìn)行開發(fā)的過程。

可編程邏輯器件的設(shè)計(jì)流程包括設(shè)計(jì)準(zhǔn)備、設(shè)計(jì)輸入、設(shè)計(jì)處理(項(xiàng)目編譯)、

仿真和定時(shí)分析、器件編程下載(設(shè)計(jì)實(shí)現(xiàn))四個(gè)步驟。

三、MAX+plus II 可編程設(shè)計(jì)流程

1) 設(shè)計(jì)準(zhǔn)備在對可編程邏輯器件的芯片進(jìn)行設(shè)計(jì)之前,首先要進(jìn)行方案論證、

系統(tǒng)設(shè)計(jì)和器件選擇等設(shè)計(jì)準(zhǔn)備工作。設(shè)計(jì)者首先要根據(jù)任務(wù)要求,如系統(tǒng)所完

成的功能及復(fù)雜程度,對工作速度和器件本身的資源、成本及連線的可布通性等

方面進(jìn)行權(quán)衡,選擇合適的設(shè)計(jì)方案。

在前面已經(jīng)介紹過,數(shù)字系統(tǒng)的設(shè)計(jì)方法通常采用從頂向下的設(shè)計(jì)方法,也是基

于芯片的系統(tǒng)設(shè)計(jì)的主要方法,它首先從系統(tǒng)設(shè)計(jì)入手,在頂層進(jìn)行功能劃分和

結(jié)構(gòu)設(shè)計(jì),采用硬件描述語言對高層次的系統(tǒng)進(jìn)行描述,并在系統(tǒng)級采用仿真手

段,驗(yàn)證設(shè)計(jì)的正確性,然后再逐級設(shè)計(jì)在低層的結(jié)構(gòu)。

由于高層次的設(shè)計(jì)與器件及工藝無關(guān),而且在芯片設(shè)計(jì)前就可以用軟件仿真手段

驗(yàn)證系統(tǒng)方案的可行性,因此自頂向下的設(shè)計(jì)方法,有利于在早期發(fā)現(xiàn)結(jié)構(gòu)設(shè)計(jì)

中的錯(cuò)誤,避免不必要的重復(fù)設(shè)計(jì),提高設(shè)計(jì)的一次成功率。自頂向下的設(shè)計(jì)采

用功能分割的方法從頂向下逐次進(jìn)行劃分,這種層次化設(shè)計(jì)的另一個(gè)優(yōu)點(diǎn)是支持

模塊化,從而可以提高設(shè)計(jì)效率。

2)設(shè)計(jì)輸入

設(shè)計(jì)者將所設(shè)計(jì)的系統(tǒng)或電路以開發(fā)軟件要求的某種形式表現(xiàn)出來,并送入

計(jì)算機(jī)的過程稱為設(shè)計(jì)輸入。設(shè)計(jì)輸入通常有以下幾種方式。

1).原理圖輸入方式

2).硬件描述語言輸入方式

3).波形輸入方式

4).層次化設(shè)計(jì)輸入方式

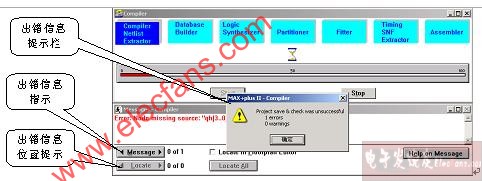

4、項(xiàng)目編譯(設(shè)計(jì)處理)

這是器件設(shè)計(jì)中的核心環(huán)節(jié)。在設(shè)計(jì)處理過程中,編譯軟件將對設(shè)計(jì)輸入文

件進(jìn)行邏輯化簡、綜合和優(yōu)化,并適當(dāng)?shù)赜靡黄蚨嗥骷詣?dòng)進(jìn)行適配,最后

產(chǎn)生編程用的編程文件。

1).語法檢查和設(shè)計(jì)規(guī)則檢查

設(shè)計(jì)輸入完成之后,在編譯過程首先進(jìn)行語法檢驗(yàn),如檢查原理圖有無漏連

信號(hào)線,信號(hào)有無雙重來源,文本輸入文件中的關(guān)鍵字有無輸入錯(cuò)誤等各種語法

錯(cuò)誤,并及時(shí)列出錯(cuò)誤信息 報(bào)告供設(shè)計(jì)者修改;然后進(jìn)行設(shè)計(jì)規(guī)則檢驗(yàn),檢查

總的設(shè)計(jì)有無超出器件資源或規(guī)定的限制 并將編譯報(bào)告列出,指明違反規(guī)則情

況以供設(shè)計(jì)者糾正。

2).邏輯優(yōu)化和綜合

化簡所有的邏輯方程或用戶自建的宏,使設(shè)計(jì)所占用的資源最少。綜合的目

的是將多個(gè)模塊設(shè)計(jì)文件合并為一個(gè)網(wǎng)表文件,并使層次設(shè)計(jì)平面化(即展平)。

3).適配和分割

確定優(yōu)化以后的邏輯能否與器件中的宏單元和I/0 單元適配,然后將設(shè)計(jì)

分割為多個(gè)便于適配的邏輯小塊形式映射到器件相應(yīng)的宏單元中。如果整個(gè)設(shè)計(jì)

不能裝入一片器件時(shí),可以將整個(gè)設(shè)計(jì)自動(dòng)分(分割)成多塊并裝入同一系列的多

片器件中去。

劃分(分割)工作可以全部自動(dòng)實(shí)現(xiàn),也可以部分由用戶控制,還可以全部由

用戶控制進(jìn)行。劃分時(shí)應(yīng)使所需器件數(shù)目盡可能少,同時(shí)應(yīng)使用于器件之間通信

的引線端子數(shù)目最少。

4).布局和布線

布局和布線工作是在設(shè)計(jì)檢驗(yàn)通過以后由軟件自動(dòng)完成的,它能以最優(yōu)的方

式對邏輯元件布局,并準(zhǔn)確地實(shí)現(xiàn)元件間的互連。布線以后軟件會(huì)自動(dòng)生成布線

報(bào)告,提供有關(guān)設(shè)計(jì)中各部分資源的使用情況等信息。

5).生成編程數(shù)據(jù)文件

項(xiàng)目編譯的最后一步是產(chǎn)生可供器件編程使用的數(shù)據(jù)文件。對CPLD 來說,是產(chǎn)

生熔絲圖文件,即JEDEC 文件(電子器件工程聯(lián)合制定的標(biāo)準(zhǔn)格式,簡稱JED 文

件);對于FPGA 來說,是生成位數(shù)據(jù)文件(BitstreamGeneration)。

4、仿真和定時(shí)分析(項(xiàng)目校驗(yàn)):

設(shè)計(jì)項(xiàng)目的校驗(yàn)包括設(shè)計(jì)項(xiàng)目的仿真(功能仿真)、定時(shí)分析兩個(gè)部分。一

個(gè)設(shè)計(jì)項(xiàng)目在編譯完成后只能為項(xiàng)目創(chuàng)建一個(gè)編程文件,但并不能保證是否真正

達(dá)到了用戶的設(shè)計(jì)要求,如邏輯功能和內(nèi)部時(shí)序要求等。所以在器件編程之前應(yīng)

進(jìn)行全面模擬檢測和仿真調(diào)試,以確保其設(shè)計(jì)項(xiàng)目在各種可能的情況下正確響應(yīng)

和正常工作,這就是項(xiàng)目校驗(yàn)(仿真調(diào)試)的必要性。

MAX+plusⅡ提供的設(shè)計(jì)校驗(yàn)過程包括仿真和定時(shí)分析,項(xiàng)目編譯后,為確保設(shè)

計(jì)無誤,再用專門軟件進(jìn)行仿真。如果發(fā)現(xiàn)了錯(cuò)誤,則對設(shè)計(jì)輸入進(jìn)行部分修改

直至無誤。

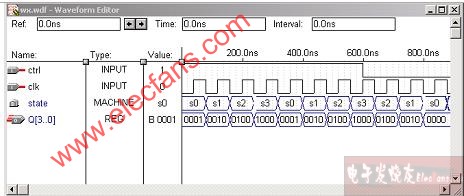

1)仿真(Simulation) MAX+plusII Simulator(仿真器)具有很強(qiáng)的靈活性,可以控制

對單個(gè)器件或多個(gè)器件設(shè)計(jì)的仿真。該模擬程序使用編譯過程中生成的二進(jìn)制模

擬網(wǎng)表文件,對一個(gè)設(shè)計(jì)實(shí)現(xiàn)功能仿真和時(shí)序仿真。

設(shè)計(jì)者可以直接用矢量輸入語言來定義輸入激勵(lì),也可以用MAX+plus ⅡWave

Editor 直接繪制波形。仿真結(jié)果在WaveEditor 或TextEditor 窗口顯示,也可作為

波形或文本文件打印出來。

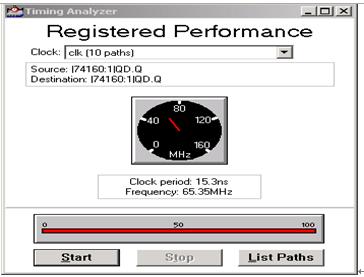

2)定時(shí)分析(TimingAnalysis) MAX+plus TimiⅡ ngAnalyzer(定時(shí)分析程序)能按

矩陣方式計(jì)算設(shè)計(jì)中點(diǎn)到點(diǎn)的延時(shí),確定在器件引線端上要求的上升和保持時(shí)

間,估計(jì)最大時(shí)鐘頻率。MAX+plusⅡ設(shè)計(jì)輸入工具與定時(shí)分析程序綜合在一起,

允許在設(shè)計(jì)文件中簡單地指定起始和終點(diǎn)標(biāo)記,或者用FloorplanEditor(平面圖編

輯器)來確定最短和最長的傳播延時(shí)。

五、器件編程下載

在以上步驟都正確實(shí)施并完全通過以后,我們就可以將我們設(shè)計(jì)的項(xiàng)目(最

終的數(shù)據(jù)編程文件)下載到器件中去,然后加入實(shí)際的激勵(lì)信號(hào)進(jìn)行測試,在我

們的目標(biāo)系統(tǒng)中進(jìn)行產(chǎn)品級使用了。如果還未最終達(dá)到我們的設(shè)計(jì)目的,則需返

回以上步驟查找設(shè)計(jì)問題直至無誤。至此,我們已經(jīng)完整的完成了可編程邏輯器

件的產(chǎn)品級設(shè)計(jì)流程,相信用戶通過對以上步驟的了解,對可編程邏輯器件的設(shè)

計(jì)有了一定的概念和了解。(有關(guān)器件下載編程配置的詳細(xì)使用說明見

MAX+plusII 軟件設(shè)計(jì)與應(yīng)用舉例章節(jié)。)

六、可編程邏輯常用設(shè)計(jì)輸入法介紹

MAX+plus II 的設(shè)計(jì)輸入方法有多種,主要包括文本設(shè)計(jì)輸入、原理圖輸入、

波形設(shè)計(jì)輸入、層次設(shè)計(jì)輸入和平面圖設(shè)計(jì)輸入等多種方式,另外,還可以利用

第三方EDA工具生成的網(wǎng)表文件輸入,該軟件可接受的網(wǎng)表有EDIF格式、VHDL

格式及Verilog 格式。設(shè)計(jì)者可根據(jù)實(shí)際情況靈活地使用最適合自己的設(shè)計(jì)方法。

下面我們將用幾種最常見的輸入法加以介紹。

1、原理圖設(shè)計(jì)輸入法

這是一種最直接的輸入方式,它使用軟件系統(tǒng)提供的元器件庫及各種符號(hào)和

連線畫出原理圖,形成原理圖輸入文件。這種方式大多用在對系統(tǒng)及各部分電路

很熟悉的情況,或在系統(tǒng)對時(shí)間特性要求較高的場合。當(dāng)系統(tǒng)功能較復(fù)雜時(shí),原

理圖輸入方式效率低,它的主要優(yōu)點(diǎn)是容易實(shí)現(xiàn)仿真,便于信號(hào)的觀察和電路的

調(diào)整。

1)、軟件的啟動(dòng):進(jìn)入Altera 軟件包,打開MAX+plus II 10.0 軟件,如下圖所示。

2)、啟動(dòng)File \ New 菜單,彈出設(shè)計(jì)輸入方式選擇窗口,如下圖所示:

3)、選擇Graphic Editor File,單擊OK 按鈕,打開原理圖編輯器,進(jìn)入原理圖設(shè)

計(jì)輸入電路編輯狀態(tài),如下圖所示:

4)、放置一個(gè)器件在原理圖上

a.在原理圖編輯器的空白處雙擊鼠標(biāo)左鍵或單擊鼠標(biāo)右鍵,在彈出的快捷菜單

中選擇Enter Symbol,出現(xiàn)下圖;

b.在上圖光標(biāo)處可直接輸入元件名稱或用鼠標(biāo)點(diǎn)取元器件庫中的所需元件,按下

OK 即可輸入元器件,下面我們將以3-8 譯碼器為例加以說明。

c.如果安放相同元件,只要按住Ctrl 鍵,用鼠標(biāo)拖動(dòng)所選中的元件復(fù)制到指定位

置即可。

d.一個(gè)完整的電路包括:輸入端口INPUT、電路元器件集合、輸出端口OUTPUT。

下圖為3-8 譯碼器的電路元件安放結(jié)果。

5)添加連線:

把鼠標(biāo)移到元件引腳附近,則鼠標(biāo)光標(biāo)自動(dòng)由箭頭變?yōu)槭诌B線狀態(tài),按住鼠標(biāo)

左鍵拖動(dòng),即可畫出連線,如果放開鼠標(biāo)左鍵則一條連線就畫好了(一條連線也

可叫做一個(gè)節(jié)點(diǎn),在原理圖編輯中節(jié)點(diǎn)是以線出現(xiàn)的)。3-8 譯碼器原理圖如下圖

所示。

6)標(biāo)記輸入/輸出端口屬性

分別雙擊輸入端口的“PIN-NAME”,當(dāng)其變成黑色時(shí),即可輸入標(biāo)記符名稱并回

車確認(rèn);輸出端口標(biāo)記方法類似。本譯碼器的三輸入斷分別標(biāo)記為:A、B、C;

其八輸出端分別為:D0、D1、D2、D3、D4、D5、D6、d7。如下圖所示。注意,

端口名字不能為空。

7)保存原理圖

單擊保存按鈕圖標(biāo),對于新建文件,出現(xiàn)類似文件管理器的圖框,請選擇保存路

徑和文件名稱,原理圖的擴(kuò)展名為*.gdf 。

8)點(diǎn)擊File\Project\set project to current file 設(shè)置此項(xiàng)目為當(dāng)前文件,如下圖所示。

注意:此操作尤為重要,否則容易出錯(cuò)。

至此,你已完成了電路原理圖設(shè)計(jì)輸入的整個(gè)過程。當(dāng)然在使用這種輸入法的時(shí)

候,有很多小技巧,如總線的使用等,這里將不再作詳細(xì)介紹。

2、文本設(shè)計(jì)輸入(VHDL)法簡介

文本設(shè)計(jì)輸入法,這種輸入法就是將電子電路的設(shè)計(jì)以文字(專用計(jì)算機(jī)語

言)或文件的形式表現(xiàn)出來,即硬件描述語言,它可分為普通硬件描述語言和行

為描述語言。普通硬件描述語言有ABEL-HDL、CUPL 等,它們支持邏輯方程、

真值表、狀態(tài)機(jī)等邏輯表達(dá)方式。行為描述語言是目前常用的高層次硬件描述語

言,有VHDL 和Verilog-HDL 等,它們都已成為IEEE 標(biāo)準(zhǔn),并且有許多突出的

優(yōu)點(diǎn):如語言與工藝的無關(guān)性,可以使設(shè)計(jì)者在系統(tǒng)設(shè)計(jì)、邏輯驗(yàn)證階段便能確

立方案的可行性;如語言的公開可利用性,使它們便于實(shí)現(xiàn)大規(guī)模系統(tǒng)的設(shè)計(jì)等;

同時(shí)硬件描述語言具有較強(qiáng)的邏輯描述和仿真功能,而且輸入效率高,在不同的

設(shè)計(jì)輸入庫之間轉(zhuǎn)換和移植非常方便,通用性很強(qiáng)。因此,運(yùn)用VHDL、

Verilog-HDL 硬件描述語言設(shè)計(jì)已是當(dāng)前的趨勢,下面我們將以VHDL 語言為例

作一簡單介紹。

1)、在主菜單上選擇File\New 或點(diǎn)擊新建快捷圖標(biāo),在彈出的菜單中選擇TextEditer File,按下OK 按鈕, 即可輸入文本,現(xiàn)已“Adder”加法器為例,進(jìn)行VHDL

語言設(shè)計(jì)輸入,在下面的文本編輯器中輸入該描述語言,如下圖所示。

2)、設(shè)計(jì)輸入完成以后,在主菜單上選擇File \Save 或點(diǎn)擊保存文件快捷圖標(biāo),

彈出如下對話框,請注意文件格式。

3)、選擇文件類型為 •VHD 硬件描述語言,輸入文件名稱“adder”,點(diǎn)擊OK 按

鈕保存文件。再選擇file/project/set project to current file 設(shè)置這個(gè)項(xiàng)目為當(dāng)前的項(xiàng)

目文件。

4)、編譯我們所設(shè)計(jì)的項(xiàng)目,從下圖可以看出其編譯沒有任何錯(cuò)誤,可以說明此

版本軟件支持VHDL 硬件描述語言設(shè)計(jì)輸入,有興趣的讀者可以對該項(xiàng)目試著

仿真一下,以得到進(jìn)一步的驗(yàn)證。

3、波形輸入法簡介

波形輸入主要用于建立和編程波形設(shè)計(jì)文件以及輸入仿真向量和功能測試

向量,從而達(dá)到對電路的設(shè)計(jì)實(shí)現(xiàn)。

波形設(shè)計(jì)輸入適合用于時(shí)序邏輯和有重復(fù)性的邏輯函數(shù)。系統(tǒng)軟件可以根據(jù)

用戶的輸入 輸出波形自動(dòng)生成邏輯關(guān)系。

波形編輯功能還允許設(shè)計(jì)者對波形進(jìn)行拷貝、剪切、粘貼、重復(fù)與伸展,從

而可以用內(nèi)部節(jié)點(diǎn)、觸發(fā)器和狀態(tài)機(jī)建立設(shè)計(jì)文件,并將波形進(jìn)行組合,顯示各

種進(jìn)制的狀態(tài)值,還可以通過將一組波形重疊到另一組波形上,對兩組仿真結(jié)果

進(jìn)行比較。下面我們將以一個(gè)非門為例加以簡單說明。

1)、按下圖方式打開新建波形文件窗口;

2)、按下圖方式分別輸入“input/output”管腳名稱in 和out;

3)、按下圖方式打開波形編輯窗口,用戶可以發(fā)現(xiàn)當(dāng)您選中其輸入或輸出端

口標(biāo)記時(shí),左邊快捷工具欄的波形編輯工具被激活,這時(shí)我們就可以來按電路要

求編輯電路波形了。

4)、按下圖所示,添加邏輯波形。可以看出下面的輸入輸出波形結(jié)構(gòu)實(shí)際上

就是非門這個(gè)電路用波形的形式來描繪和表現(xiàn)的;

5)、保存文件,注意選擇.wdf 擴(kuò)展名,如下圖所示。再選擇file/project/set

project to current file 設(shè)置這個(gè)項(xiàng)目為當(dāng)前的項(xiàng)目文件。

6)、編譯我們所設(shè)計(jì)的項(xiàng)目,從下圖可以看出 ,編譯完全正確,沒有語法

錯(cuò)誤,這說明MAX+plus II 軟件支持波形設(shè)計(jì)輸入。

說明:有興趣的讀者可以試著把該項(xiàng)目仿真一下,有關(guān)編譯和仿真的詳細(xì)說

明請參考MAX+plus II 軟件設(shè)計(jì)與應(yīng)用舉例章節(jié)。在這里提醒讀者一下,用波形

編輯設(shè)計(jì)輸入時(shí),如果要仿真,請關(guān)閉上面所有窗口,然后再選擇File\open 打

開.sym 文件(即該項(xiàng)目自動(dòng)生成的圖形文件)后再進(jìn)行仿真,如下圖所示。具

體仿真方法請參考有關(guān)章節(jié)介紹。

4、層次化設(shè)計(jì)輸入法簡介:

當(dāng)設(shè)計(jì)一個(gè)結(jié)構(gòu)較復(fù)雜的系統(tǒng)時(shí),采用層次化的設(shè)計(jì)方法,使系統(tǒng)設(shè)計(jì)變得

簡潔和方便。層次化設(shè)計(jì)是分層次、分模塊進(jìn)行設(shè)計(jì)描述。描述器件總功能的模

塊放在最上層,稱為頂層設(shè)計(jì);描述器件的某一部分功能的模塊放在下層,成為

底層設(shè)計(jì)。這種分層次的關(guān)系就類似于軟件設(shè)計(jì)分主程序和子程序的關(guān)系。層次

化設(shè)計(jì)的優(yōu)點(diǎn)其一是支持模塊化,底層模塊可反復(fù)被調(diào)用,多個(gè)底層模塊可分別

由不同的設(shè)計(jì)者同時(shí)設(shè)計(jì),從而提高了設(shè)計(jì)效率。其二是設(shè)計(jì)方法較自由,可以

采用自上而下或自下而上的設(shè)計(jì)方法。其三是同一個(gè)設(shè)計(jì)項(xiàng)目的各個(gè)模塊可以用

不同的設(shè)計(jì)輸入法來實(shí)現(xiàn),團(tuán)隊(duì)之間的合作就更加方便靈活,各自的模塊可以用

自己最熟悉的設(shè)計(jì)方法(語言)來編寫程序而相互不約束。

下面我們以一位全加器的設(shè)計(jì)為例,簡單介紹一下層次化的設(shè)計(jì)方法。一位全加

器的整個(gè)設(shè)計(jì)過程包括兩個(gè)模塊:底層半加器模塊(H_adder.vhd)、頂層全加器

模塊(F_adder.gdf)。讀者可以看出這兩個(gè)模塊是分別由VHDL 語言和原理圖兩

種方法來設(shè)計(jì)實(shí)現(xiàn)的。

1)、編寫底層半加器模塊H_adder.vhd,程序清單如下:

2)、將半加器項(xiàng)目編譯,并創(chuàng)建缺省符號(hào)H_adder.sym 。

3)、采用圖形輸入法輸入頂層的圖形文件F_adder.gdf。F_adder.gdf 是全加器設(shè)

計(jì)中的頂層圖形文件,調(diào)用了前面創(chuàng)建的符號(hào)H_adder.sym 和一個(gè)兩輸入或門,

組成一個(gè)設(shè)計(jì)實(shí)體,全加器頂層設(shè)計(jì)原理圖如下圖所示。

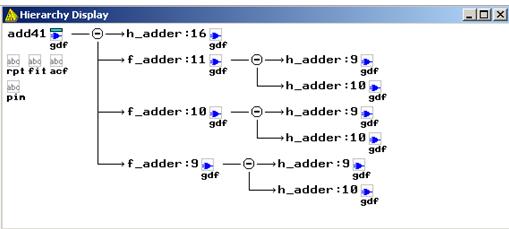

原理圖繪制完成后,就可以在項(xiàng)目的層次顯示窗口中觀察F_adder 的層次結(jié)構(gòu)。

選擇菜單MAX+plus II\Hierarchy Display(層次顯示)或點(diǎn)擊其工具欄快捷按鈕

,打開層次顯示窗口,顯示出F_adder 設(shè)計(jì)項(xiàng)目的層次樹形結(jié)構(gòu),如下圖所

示。在上面的層次顯示窗口中可以看出全加器的頂層設(shè)計(jì)是一個(gè).gdf 的圖形文

件,底層是兩個(gè)用VHDL 語言編寫的文本文件,只要我們雙擊這兩個(gè)模塊,就

可以看到我們底層設(shè)計(jì)的文本程序清單。通過以上的學(xué)習(xí),相信用戶對可編程邏

輯器件設(shè)計(jì)的靈活性更加值得青睞。

五、MAX+plus II 軟件設(shè)計(jì)與應(yīng)用舉例

說明:本書將以本例程為例詳細(xì)介紹altera 公司MAX+plusII 10.0 版本軟件的基

本應(yīng)用,其它實(shí)驗(yàn)將不再贅述。讀者通過對本實(shí)驗(yàn)的應(yīng)用舉例后將對MAX+plusII

軟件及CPLD/FPGA 的設(shè)計(jì)與應(yīng)用有一個(gè)比較完整的概念和思路。此書因篇幅有

限,僅僅介紹了MAX+plusII 軟件的最基本、最常用的一些基本功能,相信讀者

在熟練使用本軟件以后,你定會(huì)發(fā)現(xiàn)該軟件還有好多非常方便、快捷、靈活的設(shè)

計(jì)技巧與開發(fā)功能。由于編者能力有限,不詳之處再所難免,我們希望得到你的

指正與包涵。

1、項(xiàng)目的設(shè)計(jì)輸入

各種設(shè)計(jì)輸入法的詳細(xì)使用請參考“設(shè)計(jì)輸入方法介紹”章節(jié)。

下面我們以3-8 譯碼器為例加以說明:

1、打開MAX+plus II 10.0 軟件,用原理圖方式設(shè)計(jì)的譯碼器電路如下:

2、保存原理圖,本實(shí)驗(yàn)中命名為test1.gdf。

3、點(diǎn)擊File\Project\set project to current file 設(shè)置此項(xiàng)目為當(dāng)前文件,如下圖所示。

注意,此操作在你打開幾個(gè)原有項(xiàng)目文件時(shí)尤為重要,否則容易出錯(cuò)。

2、項(xiàng)目的編譯與適配

1.選擇芯片型號(hào)

選擇當(dāng)前項(xiàng)目文件欲設(shè)計(jì)實(shí)現(xiàn)的實(shí)際芯片進(jìn)行編譯適配,點(diǎn)擊Assign\Device

菜單選擇芯片,如下圖對話框所示。如果此時(shí)不選擇適配芯片的話,該軟件將自

動(dòng)把所有適合本電路的芯片一一進(jìn)行編譯適配,這將耗費(fèi)你許多時(shí)間。該例程中

我們選用CPLD 芯片來實(shí)現(xiàn),如用7000S 系列的EPM7128SLC84-6 芯片;同樣

也可以用FPGA 芯片來實(shí)現(xiàn),你只需在下面的對話窗口中指出具體的芯片型號(hào)即

可。

2、編譯適配

啟動(dòng)MAX+plus II \ Compiler 編譯器菜單,按Start 開始編譯,并顯示編譯結(jié)

果,生成下載文件。如果編譯時(shí)選擇的芯片是CPLD,則生成 .pof 文件;如果

是FPGA 芯片的話,則生成 .sof 文件,以備硬件下載編程時(shí)調(diào)用。同時(shí)生成 .rpt

報(bào)告文件、.sym 符號(hào)文件等,可詳細(xì)查看編譯結(jié)果。如有錯(cuò)誤待修改后再進(jìn)行

編譯適配,如下圖所示。注意,此時(shí)在主菜單欄里的 Processing 菜單下有許多編

譯時(shí)的設(shè)置選項(xiàng),視實(shí)際情況選擇設(shè)置。

如果說你設(shè)計(jì)的電路順利地通過了編譯,在電路不復(fù)雜的情況下,就可以對

芯片進(jìn)行編程下載和使用,直到設(shè)計(jì)的硬件實(shí)現(xiàn),如果你的電路有足夠的復(fù)雜,

那么其仿真就顯得非常必要。

3、項(xiàng)目的功能仿真與時(shí)序分析

MAX+plus II 教學(xué)版軟件支持電路的功能仿真(或稱前仿真)和時(shí)序分析

(或稱后仿真)。眾所周知,開發(fā)人員在進(jìn)行電路設(shè)計(jì)時(shí),非常希望有比較先進(jìn)

的高效的仿真工具出現(xiàn),這將為你的設(shè)計(jì)過程節(jié)約很多時(shí)間和成本。由于EDA

工具的出現(xiàn),和它所提供的強(qiáng)大的(在線)仿真功能迅速地得到了電子工程設(shè)計(jì)

人員的青睞,這也是當(dāng)今EDA(CPLD/FPGA)技術(shù)非常火爆的原因之一。下面

就MAX+plusII 軟件的仿真功能的基本應(yīng)用在本實(shí)驗(yàn)中作一初步介紹,在以后的

實(shí)驗(yàn)例程中將不在一一介紹。

一)添加仿真激勵(lì)信號(hào)波形

1.啟動(dòng)MAX+plusII\Wavefrom editor 菜單,進(jìn)入波形編輯窗口,如下圖所示。

2、將鼠標(biāo)移至空白處并單擊鼠標(biāo)右鍵,出現(xiàn)如下圖所示對話窗口。

3、選擇Enter nodes from snf 選項(xiàng)并按左鍵確認(rèn),出現(xiàn)下圖所示對話筐,單

擊和按鈕,選擇欲仿真的所有I/O管腳。

帶圖并詳細(xì)介紹請?jiān)冢?a href="http://www.nxhydt.com/soft/courseware/2008/200809249161.html" target="_blank">電氣綜合實(shí)驗(yàn)指導(dǎo)書

電子發(fā)燒友App

電子發(fā)燒友App

評論