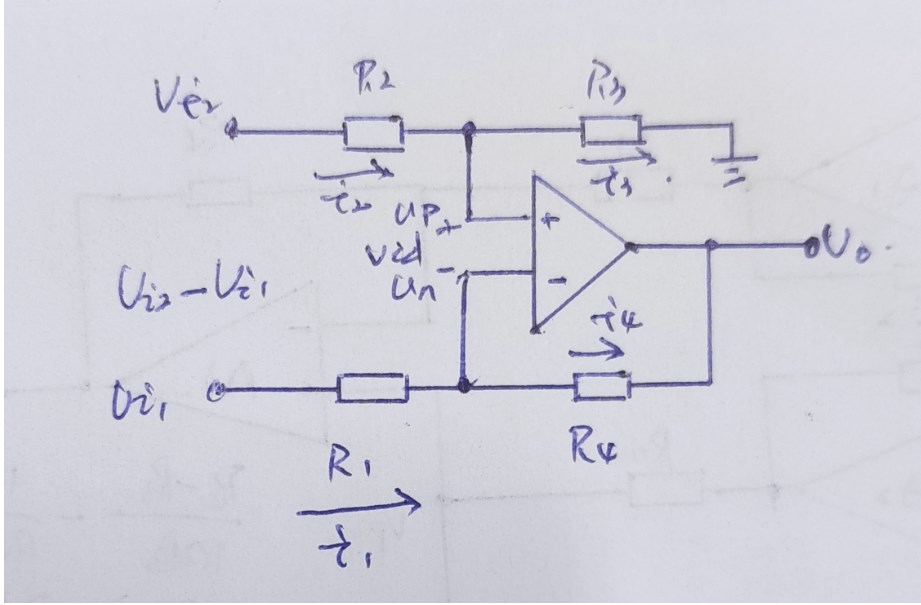

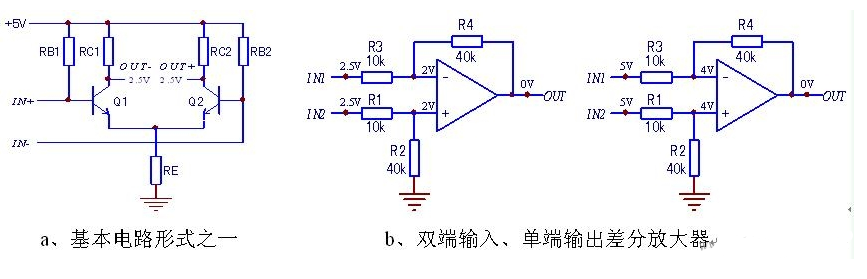

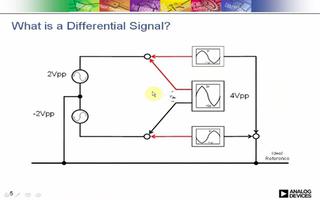

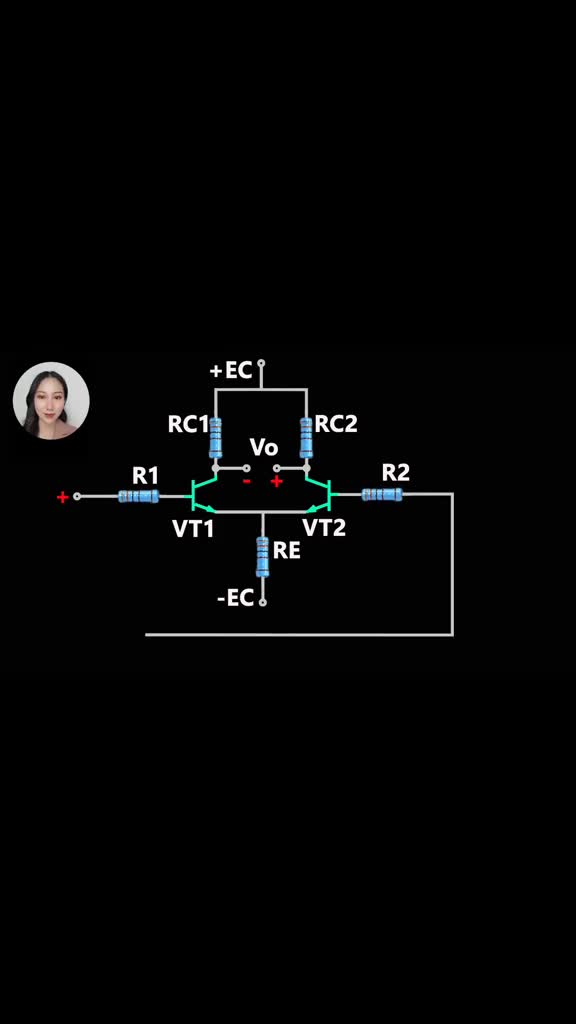

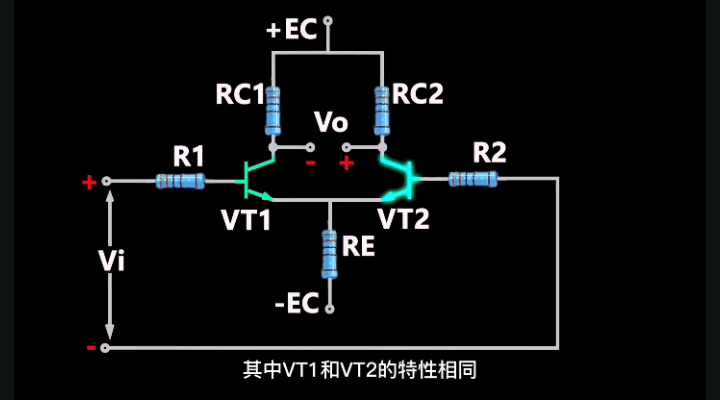

差分放大器也叫差動放大器是一種將兩個輸入端電壓的差以一固定增益放大的電子放大器,有時簡稱為“差放”。差分放大器通常被用作功率放大器(簡稱“功放”)和發射極耦合邏輯電路 (ECL, Emitter Coupled Logic) 的輸入級。

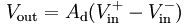

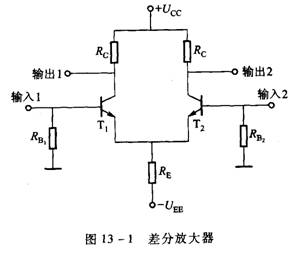

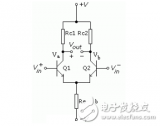

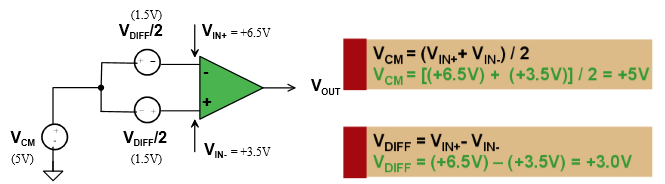

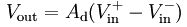

如果Q1 Q2的特性很相似,則Va,Vb將同樣變化。例如,Va變化+1V,Vb也變化+1V,因為輸出電壓VOUT=Va-Vb=0V,即Va的變化與Vb的變化相互抵消。這就是差動放大器可以作直流信號放大的原因。???? 若差放的兩個輸入為 ,則它的輸出Vout為:

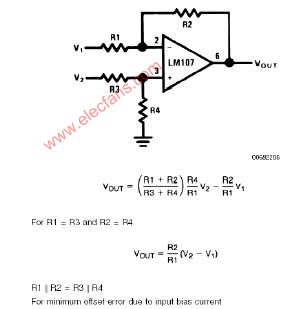

,則它的輸出Vout為:

?

其中Ad是差模增益 (differential-mode gain),Ac是共模增益 (common-mode gain)。

因此為了提高信/噪比,應提高差動放大倍數,降低共模放大倍數。二者之比稱做共模仰制比(CMRR, common-mode rejection ratio)。共模放大倍數AC可用下式求出:

??????? Ac=2Rl/2Re

通常以差模增益和共模增益的比值共模抑制比 (CMRR, common-mode rejection ratio) 衡量差分放大器消除共模信號的能力:

?

由上式可知,當共模增益Ac→0時,CMRR→∞。Re越大,Ac就越低,因此共模抑制比也就越大。因此對于完全對稱的差分放大器來說,其Ac = 0,故輸出電壓可以表示為:

所謂共模放大倍數,就是Va,Vb輸入相同信號時的放大倍數。如果共模放大倍數為0,則輸入噪聲對輸出沒有影響。

要減小共模放大倍數,加大RE就行通常使用內阻大的恒流電路來帶替RE

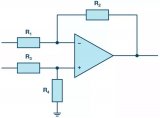

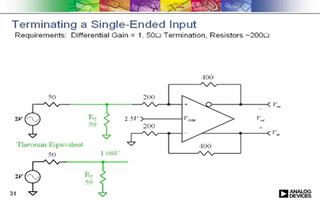

?差分放大器是普通的單端輸入放大器的一種推廣,只要將差放的一個輸入端接地,即可得到單端輸入的放大器。很多系統在差分放大器的一個輸入端輸入反饋信號,另一個輸入端輸入反饋信號,從而實現負反饋。常用于電機或者伺服電機控制,穩壓電源,測量儀器以及信號放大。在離散電子學中,實現差分放大器的一個常用手段是差動放大,見于多數運算放大器集成電路中的差分電路。

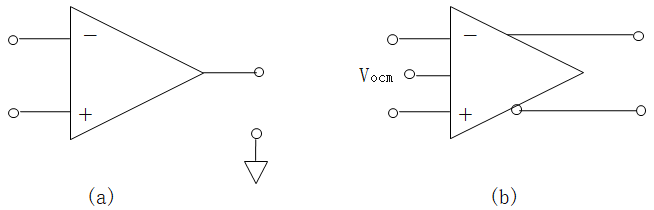

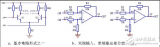

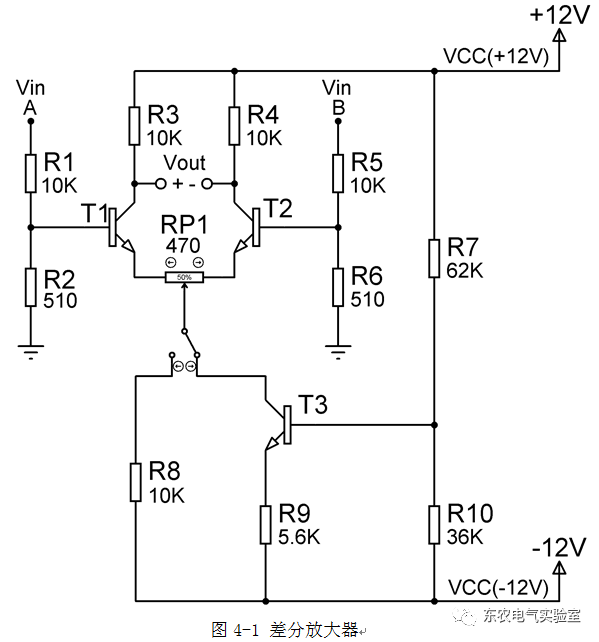

單端輸出的差動放大電路 (不平衡輸出)

?

單端較差動輸出之幅度小一倍,使用單端輸出時,共模訊號不能被抑制,因Vi1與Vi2同時增加,VC1與VC2則減少,而且VC1=VC2,但Vo =VC2,并非于零(產生零點漂移)。

但是加大RE阻值可以增大負回輸而抑制輸出,并且抑制共模訊號,因Vi1=Vi2時,

Ii1及Ii2也同時增加,IE亦上升而令VE升高,這對Q1和Q2產生負回輸,

令Q1和Q2之增益減少,即Vo減少。

當差動訊號輸入時,Vi1 = -Vi2,IC1增加而IC2減少,總電流IE = IC1 + IC2便不變,

因此VE也不變,加大RE電阻值之電路會將差動訊號放大,不會對Q1及Q2產生負回輸

及抑制。

??? b)減低功率消耗(相對純電阻來說)。

??? c)提高差動放大之輸出電壓。

??? d)提高共模抑制比CMRR。

?

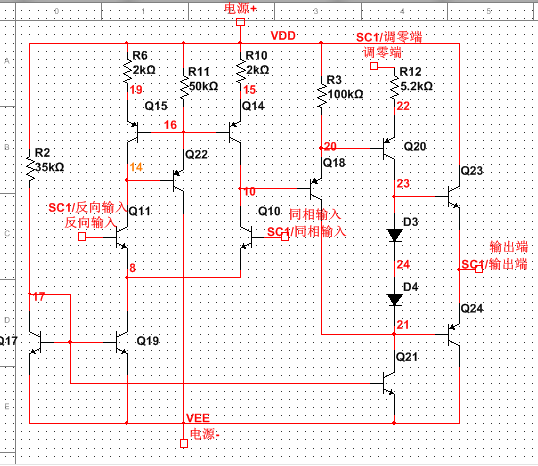

因電流鏡像原理,IC4 = IC1

故此,Io = IC4 IC2 = IC1 IC2 (ΔIo = 2ΔIC1或2ΔIC2)

這說明了輸出電流是IC1和IC2的相差,即將輸出變為具有雙端差動輸出性能的單端輸出 (故對共模訊號之抑制有改善因雙端差動輸出才能產生消除共模訊號作用)。

IC2減少使Q2之VCE增加,使Vo上升而IC4增加,使Q4之VCE減少,這也是使Vo增加,

故此,Vo上升之幅度是使用電阻為負載之單端輸出電壓大一倍。

- 差分(21161)

相關推薦

帶恒流源的差分放大器如何提高共模抑制比的?

31

31差動放大器怎樣進行靜態調零?

776

776差分信號怎么辨別方向?

163

163差分放大器和單端放大器的區別是什么?

454

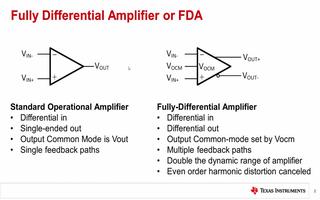

454全差分放大器四個增益的關系是什么?

213

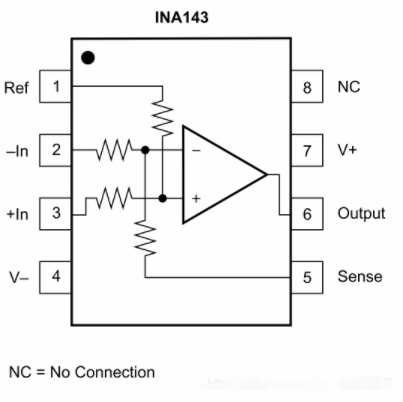

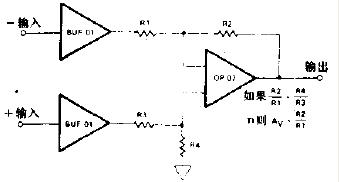

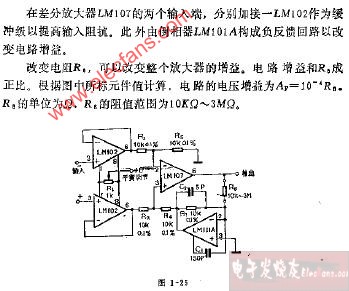

213儀表放大器的工作原理詳解

792

792低噪聲放大器工作原理詳解

625

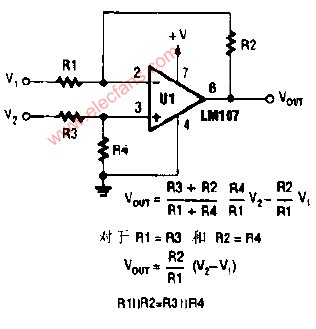

625差分放大器增益計算公式

520

520差分放大器的原理是什么?差分放大器又叫什么?

245

245差分放大器是求差放大電路嗎?

173

173

差分放大器的特點 差分放大器的優缺點 差分放大器的作用

1260

1260差分放大器工作原理詳細講解

604

604

差分放大器和運算放大器區別

744

744差分放大器公式,惠斯通電橋差分放大器電路分析

1540

1540

儀表放大器和差分放大器的區別

509

509低溫放大器的工作原理、種類及應用

487

487增益模塊放大器的的工作原理

154

154高壓放大器工作原理(高壓放大器怎么用的)

378

378

全差分放大器的評估

541

541

單端至差分放大器設計技巧

669

669單端至差分放大器設計技巧

470

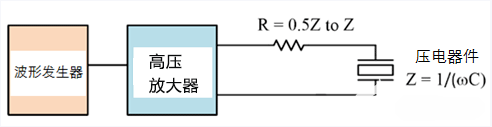

470高壓放大器驅動壓電器件工作原理

679

679

國產高共模電壓差分放大器

544

544

固定增益差分放大器的增益能增加嗎

3174

3174

差分放大器工作原理和基本電路形式

118992

118992

不同差分放大器公式

35632

35632

差分放大器的特點及相關軟件的基礎知識

3759

3759

基礎教程:差分放大器以及相關設計軟件的基礎知識

4073

4073

差分放大器的工作原理和基本電路圖解析

110300

110300

差分放大器的原理,和差分放大器的應用

20589

20589

差分放大器的工作原理

77

77差分放大器的工作原理詳解

41

41差分放大器:The Difference Amplifier

2020

2020

差分放大器驅動高速ADC的電路

1984

1984

電子發燒友App

電子發燒友App

評論