CPLD,CPLD是什么意思

CPLD是指結(jié)構(gòu)比較復(fù)雜的可編程邏輯器件,它包括下述輸出宏單元結(jié)構(gòu):

(1)可編程I/O 允

2010-03-26 17:08:50 2953

2953 請(qǐng)教大神~~~有誰用vhdl語言寫過基于cpld在不帶字庫的12864上顯示字幕流動(dòng)的程序嗎???急求

2014-05-21 16:20:22

AMD公司最先生產(chǎn)帶有宏單元的可編程邏輯器件PAL22V10。目前PAL22V10已成為劃分PLD的界限。可編程邏輯器件所包含的門數(shù)大于PAL22V10所包含則門數(shù),就被認(rèn)為是復(fù)雜可編程邏輯器件,即CPLD。

2018-05-24 01:39:00 2738

2738 CPLD即復(fù)雜可編程邏輯器件,是從PAL和GAL器件發(fā)展出來的器件,相對(duì)而言規(guī)模大,結(jié)構(gòu)復(fù)雜,屬于大規(guī)模集成電路范圍。是一種用戶根據(jù)各自需要而自行構(gòu)造邏輯功能的數(shù)字集成電路。其基本設(shè)計(jì)方法是借助集成

2017-10-24 10:40:00 90223

90223 CPLD是一種用戶根據(jù)各自需要而自行構(gòu)造邏輯功能的數(shù)字集成電路。其基本設(shè)計(jì)方法是借助集成開發(fā)軟件平臺(tái),用原理圖、硬件描述語言等方法,生成相應(yīng)的目標(biāo)文件,通過下載電纜(“在系統(tǒng)”編程)將代碼傳送到目標(biāo)芯片中,實(shí)現(xiàn)設(shè)計(jì)的數(shù)字系統(tǒng)。

2019-10-04 17:59:00 9152

9152 本文主要介紹CPLD和FPGA的基本結(jié)構(gòu)。 CPLD是復(fù)雜可編程邏輯器件(Complex Programable Logic Device)的簡稱,F(xiàn)PGA是現(xiàn)場可編程門陣列(Field

2020-09-25 14:56:33 11489

11489

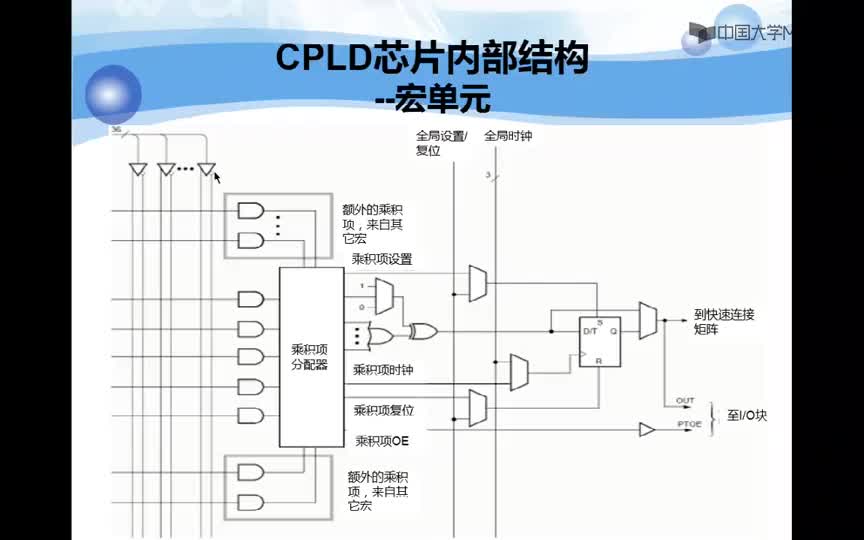

1.CPLD:CPLD主要是由可編程邏輯宏單元(LMC,LogicMacroCell)圍繞中心的可編程互連矩陣單元組成,其中LMC邏輯結(jié)構(gòu)較復(fù)雜,并具有復(fù)雜的I/O單元互連結(jié)構(gòu),可由用戶根據(jù)需要生成

2017-09-26 16:38:12 88759

88759 現(xiàn)在一般把所有超過某一集成度(如1000門以上)的PLD器件都稱為CPLD。CPLD由可編程邏輯的功能塊圍繞一個(gè)可編程互連矩陣構(gòu)成。由固定長度的金屬線實(shí)現(xiàn)邏輯單元之間的互連,并增加了I/O控制模塊

2018-06-20 16:22:42 15379

15379

CPLD綜合應(yīng)用技術(shù),介紹CPLD應(yīng)用技術(shù),非常實(shí)用的教程

2015-12-21 14:52:10 12

12 Altera FPGA/CPLD設(shè)計(jì)(基礎(chǔ)篇)系統(tǒng)地介紹了FPGA/CPLD的基本設(shè)計(jì)方法。在介紹FPGA/CPLD概念的基礎(chǔ)上,介紹了Altera上流FPGA/CPLD的結(jié)構(gòu)與特點(diǎn),并通過豐富的實(shí)例講解Quartus II與ModelSim、Sy

2009-02-12 09:16:07 5248

5248 CPLD設(shè)計(jì)范例

2010-06-30 17:57:47 59

59 FPGA CPLD中的Verilog設(shè)計(jì)小技巧(肇慶理士電源技術(shù)有限)-FPGA CPLD中的Verilog設(shè)計(jì)小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 34

34 altera fpga/cpld設(shè)計(jì) 基礎(chǔ)篇結(jié)合作者多年工作經(jīng)驗(yàn),系統(tǒng)地介紹了FPGA/CPLD的基本設(shè)計(jì)方法。在介紹FPGA/CPLD概念的基礎(chǔ)上,介紹了Altera主流FPGA/CPLD的結(jié)構(gòu)與特點(diǎn),并通過豐富的實(shí)例講解

2009-07-10 17:35:45 57

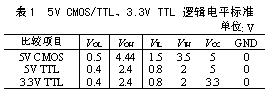

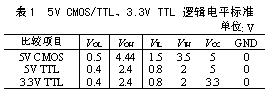

57 CPLD內(nèi)部施密特觸發(fā)器電器特性見表1。目前大部分使用的CPLD都需要兩個(gè)電源VCC和VCCIO,VCC就是CPLD內(nèi)部的核電壓,VCCIO是CPLD所有I/O 引腳電壓。

2018-05-11 08:22:00 1159

1159

在單片機(jī)系統(tǒng)中使用CPLD,可使系統(tǒng)構(gòu)成靈活,提高可靠性,縮短開發(fā)周期。介紹在MCS-51應(yīng)用系統(tǒng)中的CPLD應(yīng)用設(shè)計(jì)實(shí)例,詳細(xì)分析CPLD的應(yīng)用和實(shí)現(xiàn)方法,提出設(shè)計(jì)中選用和使用CPLD的

2010-07-14 14:04:25 39

39 都是FPGA/CPLD邏輯設(shè)計(jì)的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計(jì)思想能在FPGA/CPLD設(shè)計(jì)工作種取得事半功倍的效果。

2023-05-18 08:56:57 165

165

STM32 通過 FSMC 讀寫CPLD 的程序,CPLD掛在STM32的地址線和數(shù)據(jù)線上,將CPLD看做片外RAM的方式來進(jìn)行讀寫,在我做的板子上CPLD掛在第四個(gè)區(qū),因此基地址是0x6c000000,通過FSMC來進(jìn)行讀寫,程序較為簡單,具體的地方在函數(shù)中都有注釋,僅供參考。

2018-04-20 10:38:00 3059

3059

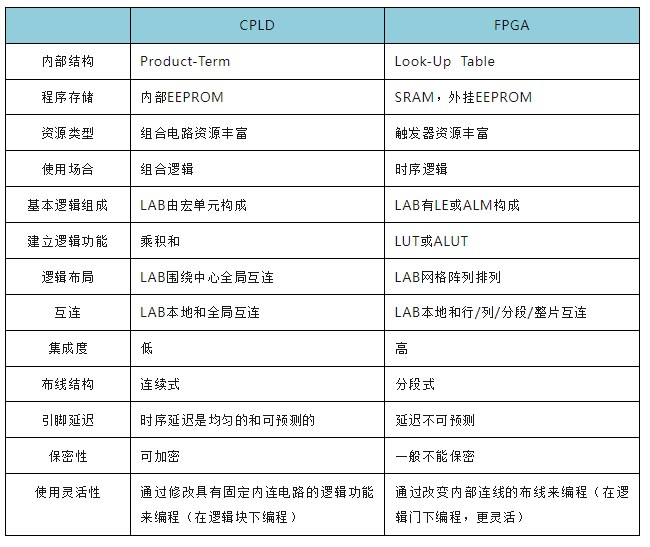

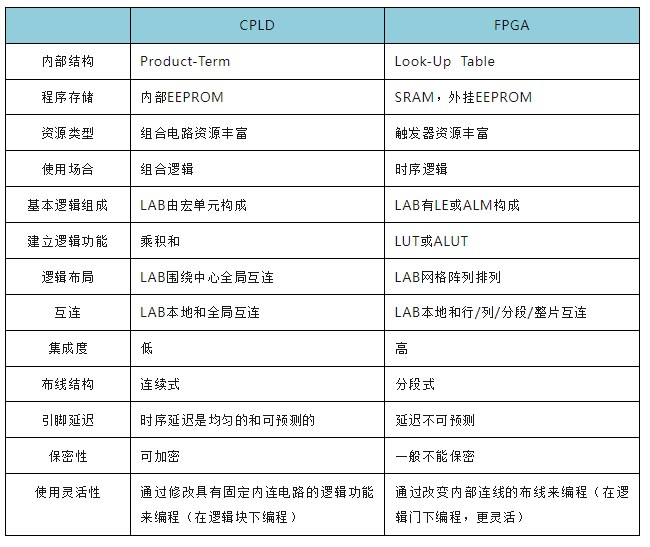

CPLD和FPGA都是我們經(jīng)常會(huì)用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區(qū)分,把他們都叫做FPGA。那么兩者到底有什么區(qū)別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區(qū)別。

2017-09-18 16:35:32 5

5 介紹利用CPLD實(shí)現(xiàn)快速、同步計(jì)算的虛擬相位測量方法,講述系統(tǒng)的原理與結(jié)構(gòu),給出CPLD的模塊設(shè)計(jì)。

2010-08-09 14:58:58 19

19 介紹了一種用CPLD(復(fù)雜可編程邏輯器件)作為核心控制電路的測試系統(tǒng)接口,通過時(shí)cPLD和竹L電路的比較及cPLD在系統(tǒng)中實(shí)現(xiàn)的強(qiáng)大功能,論述了CPLD在測試系統(tǒng)接口中應(yīng)用的可行性和優(yōu)越性,簡單介紹

2019-01-01 16:18:00 1218

1218

可編程邏輯包括 PAL、GAL、PLD 等。通過不斷發(fā)展,它已經(jīng)發(fā)展成為現(xiàn)在的CPLD/FPGA。CPLD(復(fù)雜可編程邏輯器件)和FPGA(現(xiàn)場可編程門陣列)的功能基本相同,只是實(shí)現(xiàn)原理略有不同。當(dāng)

2023-07-03 14:33:38 2379

2379

CPLD 器件應(yīng)用隨著生產(chǎn)工藝的逐步提高以及 CPLD 開發(fā)系統(tǒng)的不斷完善,CPLD 器件容量也由幾百門飛速發(fā)展到百萬門以上,使得一個(gè)復(fù)雜數(shù)字系統(tǒng)完全可以在一個(gè)芯片中實(shí)現(xiàn)。HDL

2010-01-27 11:40:02 48

48 Altera FPGA CPLD學(xué)習(xí)筆記(肇慶理士電源技術(shù)有限)-Altera FPGA CPLD學(xué)習(xí)筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 76

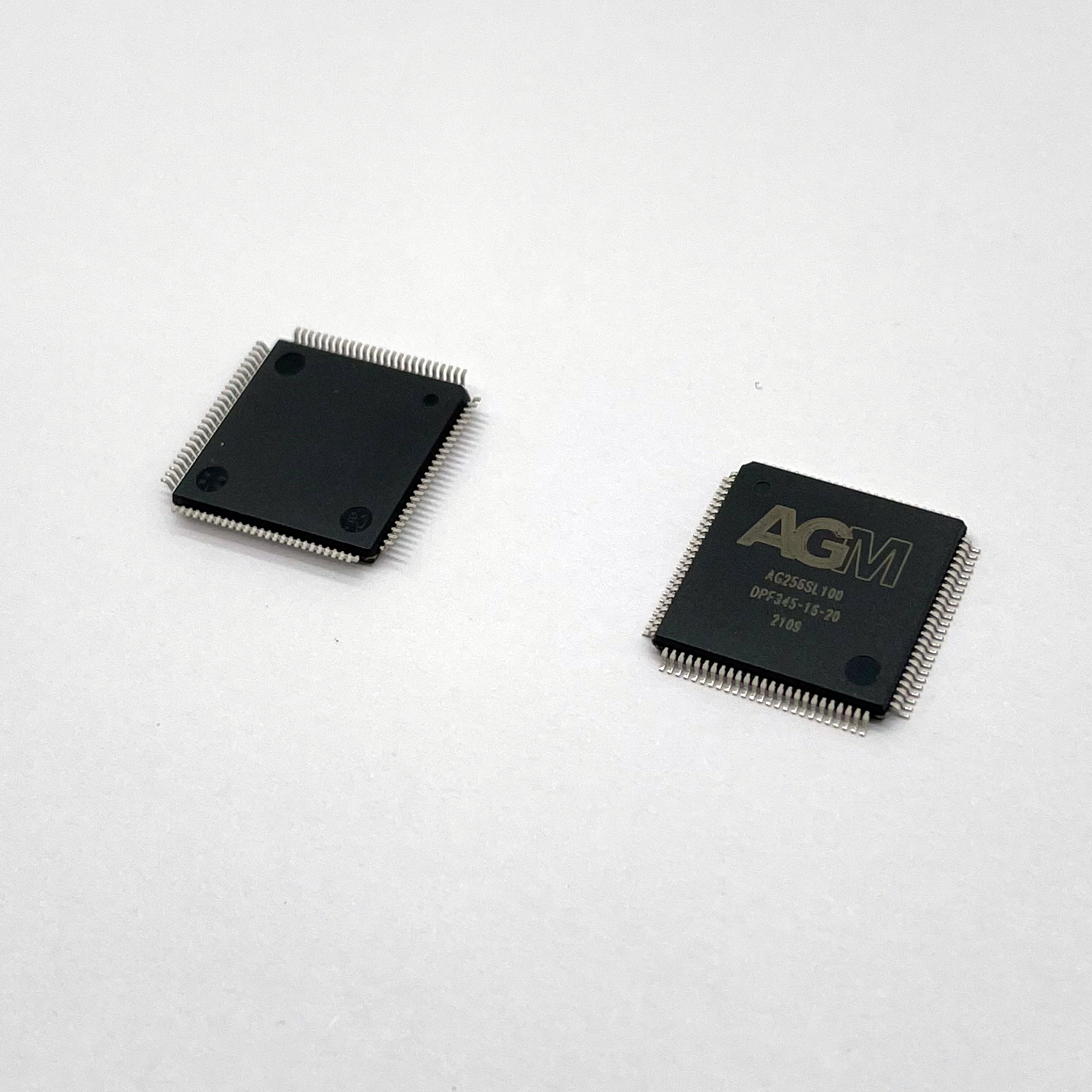

76 EPM570T144C5N - 芯片, CPLD, MAX II, 570單元, 144TQFP

2022-07-29 17:19:16

在單片機(jī)系統(tǒng)中使用CPLD,可使系統(tǒng)構(gòu)成靈活,提高可靠性,縮短開發(fā)周期。介紹在MCS-51 應(yīng)用系統(tǒng)中的CPLD 應(yīng)用設(shè)計(jì)實(shí)例, 詳細(xì)分析CPLD 的應(yīng)用和實(shí)現(xiàn)方法,提出設(shè)計(jì)中選用和使用CPLD

2009-05-14 13:49:49 39

39 cpld的輸入電源電路

2009-09-08 00:48:28 822

822 基于CPLD的SGPIO總線實(shí)現(xiàn)及應(yīng)用

2017-01-24 16:00:51 74

74 CPLD實(shí)現(xiàn)Watchdog 功能,通過對(duì)寄存器的操作,實(shí)現(xiàn)Watchdog各項(xiàng)功能。CPLD 內(nèi)部Watchdog 模塊邏輯框圖如下所示。

2019-06-12 15:59:33 10

10 《Altera FPGA/CPLD設(shè)計(jì)(高級(jí)篇)》結(jié)合作者多年工作經(jīng)驗(yàn),深入地討論了Altera FPGA/CPLD的設(shè)計(jì)、優(yōu)化技巧。在討論FPGA/CPLD設(shè)計(jì)指導(dǎo)原則的基礎(chǔ)上,介紹了Altera器件的高級(jí)應(yīng)用;引領(lǐng)讀者

2009-02-12 09:19:12 4794

4794 CPLD和FPGA都是由邏輯陣列模塊構(gòu)成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。

2023-06-28 11:28:04 491

491

FPGA LAB和CPLD的LAB設(shè)計(jì)不同。CPLD LAB由宏單元構(gòu)成,包括自己的本地可編程陣列,而FPGA LAB由大量的邏輯模塊構(gòu)成,這些模塊被稱為邏輯單元,即LE,而且本地互連和邏輯分開。LE看起來可能和CPLD宏單元相似,但更容易配置,有更豐富的特性來提高性能,減少邏輯資源的浪費(fèi)。

2018-04-17 17:02:00 1858

1858

CPLD邏輯電路 圖6是CPLD內(nèi)部邏輯電路,CPLD選用的是LATTICE公司的ispLSI1016E,邏輯設(shè)計(jì)采用原理圖輸入法,主要功能是對(duì)MUX的通道進(jìn)行選擇、對(duì)A/D轉(zhuǎn)換器進(jìn)

2009-11-13 12:04:13 2413

2413

FPGA和CPLD的區(qū)別,以及設(shè)計(jì)思路思想

2016-02-17 11:20:56 38

38 本文討論的四種常用FPGA/CPLD設(shè)計(jì)思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計(jì)的內(nèi)在規(guī)律的

2010-11-04 10:11:28 585

585

CPLD/FPGA的基本知識(shí)講解。

2021-03-30 09:55:18 27

27 Xilinx FPGA工程例子源碼:Xilinx.CPLD源碼參考設(shè)計(jì)

2016-06-07 15:07:45 33

33 CPLD系統(tǒng)設(shè)計(jì)技術(shù)入門與應(yīng)用定位于復(fù)雜可編程邏輯器件的系統(tǒng)設(shè)計(jì)技術(shù),以ALTERA公司的系列芯片和相應(yīng)的開發(fā)軟件為目標(biāo)載體進(jìn)行闡述.《CPLD系統(tǒng)設(shè)計(jì)技術(shù)入門與應(yīng)用》從系統(tǒng)設(shè)計(jì)的

2009-01-13 14:12:32 159

159 CPLD和FPGA都是我們經(jīng)常會(huì)用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區(qū)分,把他們都叫做FPGA。那么兩者到底有什么區(qū)別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區(qū)別。

2018-05-24 02:03:00 48955

48955

PC機(jī)與CPLD通信問題的研究

2017-01-19 21:22:54 5

5 設(shè)計(jì)了一種基于DSP+CPLD構(gòu)架的電能質(zhì)量監(jiān)測裝置,該裝置利用CPLD產(chǎn)生DSP外圍器件的控制時(shí)序,丈中詳細(xì)介紹了CPLD對(duì)DSP外圍器件的邏輯接口設(shè)計(jì),通過MAX+PLUSII對(duì)CPLD的控制時(shí)序進(jìn)行

2010-08-26 16:06:20 31

31 基于FPGA/CPLD的UART功能設(shè)計(jì)

2017-01-23 20:45:37 30

30 FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享.(電源技術(shù)發(fā)展怎么樣)-FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 當(dāng)利用CPLD/FPGA開發(fā)系統(tǒng)完成數(shù)字電路或系統(tǒng)的開發(fā)設(shè)計(jì)并仿真校驗(yàn)通過之后,就需要將獲得的CPLD/FPGA編程配置數(shù)據(jù)下載到CPLD/FPGA芯片中,以便最后獲得所設(shè)計(jì)的硬件數(shù)字電路或系

2010-06-01 10:14:46 23

23 UART 是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計(jì)包含UART 發(fā)送器、接收器和波特率發(fā)生器。設(shè)計(jì)應(yīng)用EDA 技術(shù),基于FPGA/CPLD 器件設(shè)計(jì)與實(shí)現(xiàn)UART。關(guān)鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 22

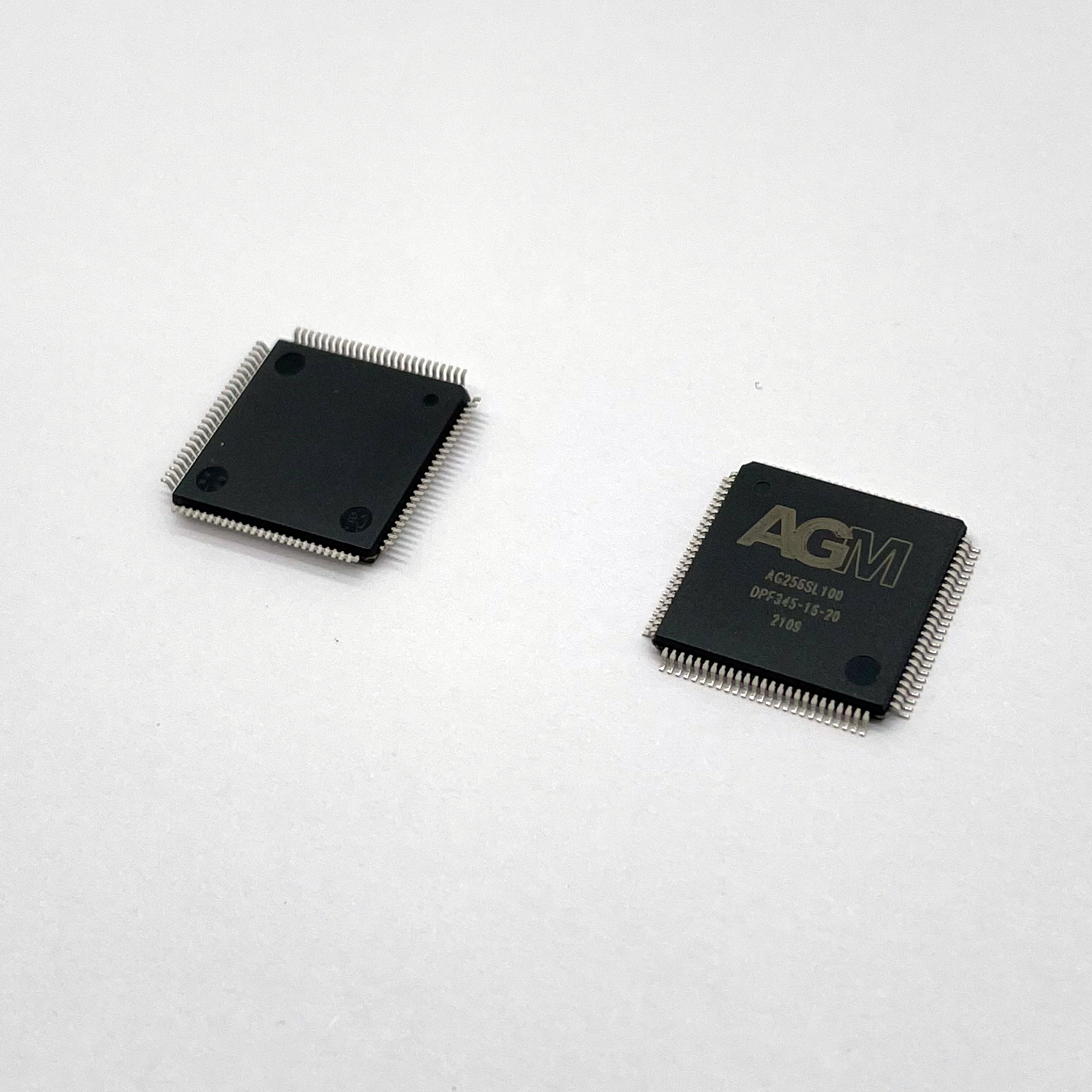

22 CPLD國產(chǎn)替代的最成熟選擇是什么?

2022-03-04 09:21:03 8011

8011

CPLD的MAX系列器件庫max-13.0.1.232

2022-12-21 17:26:11 4

4 一、 配置方式

ALTERA CPLD器件的配置方式主要分為兩大類:主動(dòng)配置方式和被動(dòng)方式。主動(dòng)配置方式由CPLD器件引導(dǎo)配置操作過程,它控制著外部存儲(chǔ)器和

2009-06-20 10:58:14 1751

1751 項(xiàng)目中需要使用CPLD完成一部分算法設(shè)計(jì),參數(shù)由AVR給出,因此需要完成AVR和CPLD的通信。因此寫了一個(gè)測試程序。CPLD掛在AVR的數(shù)據(jù)和地址總線上,AVR使用ATmega128,在CPLD中設(shè)置幾個(gè)寄存器,通過AVR讀寫寄存器來實(shí)現(xiàn)兩者之間的通信。

2019-06-03 15:24:28 894

894 FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域

2017-10-24 10:04:00 45754

45754 電子發(fā)燒友網(wǎng)站提供《CPLD在臭氧電源中的應(yīng)用.pdf》資料免費(fèi)下載

2023-10-19 10:37:01 0

0 摘要: 較詳細(xì)地闡述不同邏輯電平的接口原理。以低壓CPLD EPM7512A為例,給出在混合電壓系統(tǒng)中的具體設(shè)計(jì)方案。

關(guān)鍵詞: 低壓CPLD 邏輯電平

2009-06-20 10:53:23 753

753

電子發(fā)燒友網(wǎng)站提供《Xilinx CPLD在線編程參考指南.pdf》資料免費(fèi)下載

2022-10-14 15:26:58 3

3

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論