第二十五講 同步計數(shù)器

7.3.2 同步計數(shù)器

一、同步二進制計數(shù)器

1.同步二進制加法計數(shù)器

JK觸發(fā)器組成的4位同步二進制加法計數(shù)器

工作原理簡介。

2.同步二進制減法計數(shù)器

設(shè)計思想:

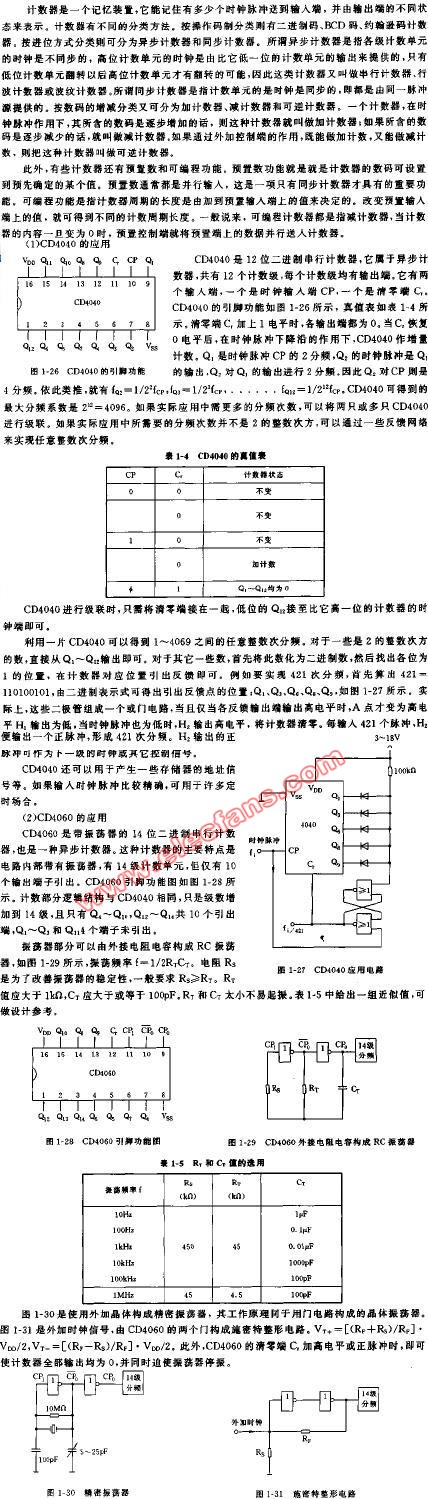

3.集成同步二進制計數(shù)器CT74LS161

邏輯功能示意圖。

功能表。

4.利用反饋置數(shù)法獲得N進制計數(shù)器

⑴ 計數(shù)器的置數(shù)功能

⑵ 利用反饋置數(shù)法獲得N進制計數(shù)器

步驟:

① 寫出計數(shù)器狀態(tài)的二進制代碼。

② 寫出反饋歸零函數(shù)。

③ 畫連線圖。

[例7.3.2] 試用 CT74LS161構(gòu)成十進制計數(shù)器

[例7.3.3]試用CT74LS161構(gòu)成十二進制計數(shù)器。

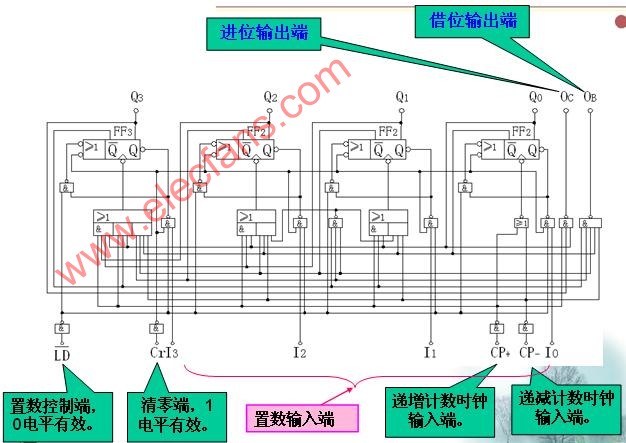

5.同步二進制加/減計數(shù)器

二、同步十進制加法計數(shù)器

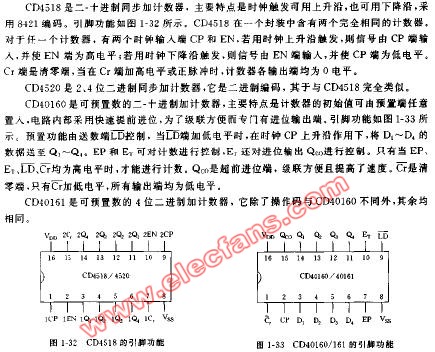

三、集成同步計數(shù)器

1.集成十進制同步加法計數(shù)器CT74LS160

2.集成十進制同步加/減計數(shù)器CT74LS190

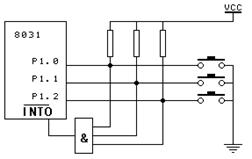

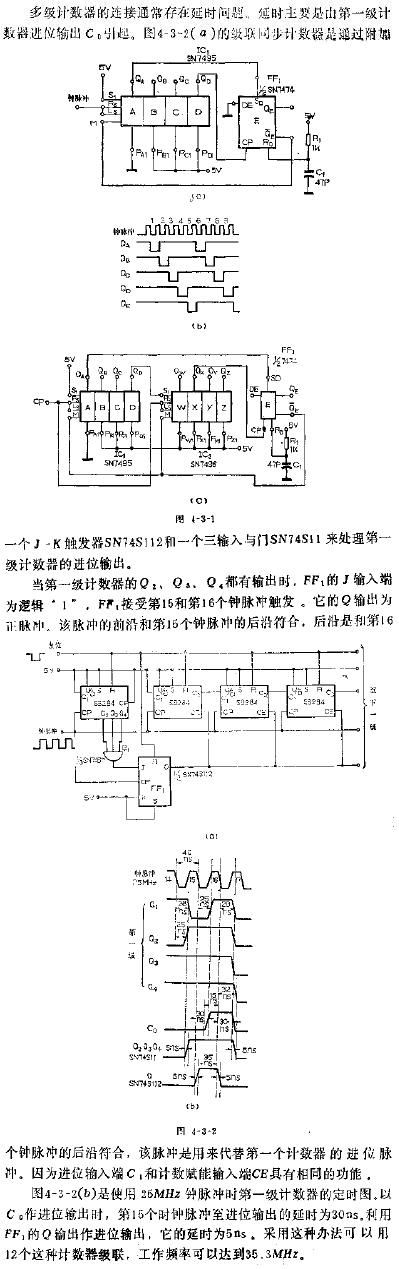

7.3.3B 利用計數(shù)器的級聯(lián)獲得大容量同步N進制計數(shù)器

一、級聯(lián)法

同步計數(shù)器實現(xiàn)的方法:

兩片CT74LS160級聯(lián)成100進制同步加法計數(shù)器。

二、反饋歸零法

兩片4位二進制數(shù)加法計數(shù)器CT74LS161級聯(lián)成五十進制計數(shù)器。

現(xiàn)代教學方法與手段:

用DLCCAI或EWB演示74LS161、74LS160、74LS190的邏輯功能

7.3.2 同步計數(shù)器

一、同步二進制計數(shù)器

1.同步二進制加法計數(shù)器

根據(jù)學生的程度,有時也可以從設(shè)計的角度,討論同步二進制計數(shù)器的設(shè)計思想。

[同步計數(shù)器中,所有觸發(fā)器的CP端是相連的,CP的每一個觸發(fā)沿都會使所有的觸發(fā)器狀態(tài)更新。因此不能使用T′觸發(fā)器。

應(yīng)控制觸發(fā)器的輸入端,即將觸發(fā)器接成T觸發(fā)器。

只有當?shù)臀幌蚋呶贿M位時(即低位全1時再加1),令高位觸發(fā)器的T=1,觸發(fā)器翻轉(zhuǎn),計數(shù)加1。]

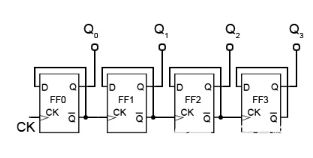

由JK觸發(fā)器組成的4位同步二進制加法計數(shù)器(參見教材中圖7.3.7)

用下降沿觸發(fā)。下面分析它的工作原理。(鞏固同步計數(shù)器的分析方法,簡單介紹思路,可由學生自學詳細的內(nèi)容。可不寫板書)

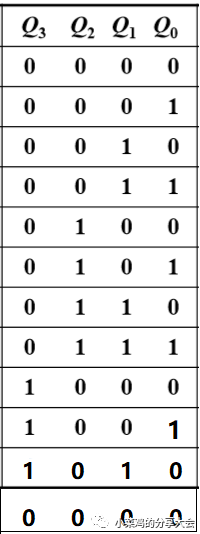

(2)列狀態(tài)轉(zhuǎn)換真值表。

與或式(狀態(tài)方程)→真值表(狀態(tài)轉(zhuǎn)換真值表)。

將現(xiàn)態(tài)看成是輸入變量,次態(tài)看成是輸出函數(shù)。

(3)邏輯功能。十六進制計數(shù)器。

2.同步二進制減法計數(shù)器

設(shè)計思想:

[同步計數(shù)器中,所有觸發(fā)器的CP端是相連的,CP的每一個觸發(fā)沿都會使所有的觸發(fā)器狀態(tài)更新。因此不能使用T′觸發(fā)器。

應(yīng)控制觸發(fā)器的輸入端,即將觸發(fā)器接成T觸發(fā)器。

只有當?shù)臀幌蚋呶唤栉粫r(即低位全0時再減1),令高位觸發(fā)器的T=1,觸發(fā)器翻轉(zhuǎn),計數(shù)減1。]

為此,只要將二進制加法計數(shù)器的輸出由Q端改為 端,便成為同步二進制減法計數(shù)器了。

3.集成同步二進制計數(shù)器CT74LS161

主要功能分析:(看功能表分析,不必寫板書。)

4.利用反饋置數(shù)法獲得N進制計數(shù)器

⑴ 計數(shù)器的置數(shù)功能

應(yīng)先將計數(shù)起始數(shù)據(jù)預(yù)先置入計數(shù)器。

集成計數(shù)器的置數(shù)方式也有異步和同步兩種。

①異步置數(shù):與時鐘脈沖CP沒有任何關(guān)系,只要異步置數(shù)控制端出現(xiàn)置數(shù)信號,并行數(shù)據(jù)便立刻被置入。

② 同步置數(shù):輸入端獲得置數(shù)信號后,只是為置數(shù)創(chuàng)造了條件,還需要再輸入一個計數(shù)脈沖CP,計數(shù)器才能將預(yù)置數(shù)置入。

⑵ 利用反饋置數(shù)法獲得N進制計數(shù)器

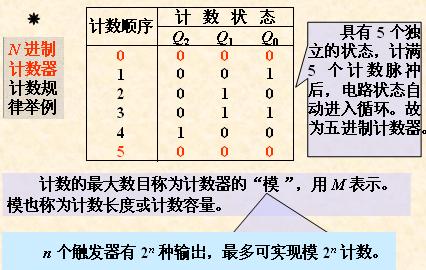

用 S0,S1,S2…,SN 表示輸入0,1,2,…,N個計數(shù)脈沖CP時計數(shù)器的狀態(tài)。

N進制計數(shù)器的計數(shù)工作狀態(tài)應(yīng)為N個:S0,S1,S2…,SN-1

對于異步置數(shù):在輸入第N個計數(shù)脈沖CP后,通過控制電路,利用狀態(tài) 產(chǎn)生一個有效置數(shù)信號,送給異步置數(shù)端,使計數(shù)器返回到初始的預(yù)置數(shù)狀態(tài),即實現(xiàn)了N進制計數(shù)。

對于同步置數(shù):在輸入第N-1個計數(shù)脈沖CP時,利用狀態(tài) 產(chǎn)生一個有效置數(shù)信號,送給同步置數(shù)控制端,等到輸入第N個計數(shù)脈沖CP時,計數(shù)器返回到初始的預(yù)置數(shù)狀態(tài),從而實現(xiàn)N進制計數(shù)。

課堂討論:實現(xiàn)N進計數(shù),異步置數(shù)時狀態(tài) 出現(xiàn)嗎?

步驟:

① 寫出計數(shù)器狀態(tài)的二進制代碼。

利用異步置數(shù)輸入端獲得N進制計數(shù)器時,寫出 對應(yīng)的二進制代碼;

利用同步置數(shù)端獲得 N進制計數(shù)器時,寫出 對應(yīng)的二進制代碼。

② 寫出反饋歸零函數(shù)。

根據(jù)SN或SN-1寫出置數(shù)端的邏輯表達式。

③ 畫連線圖。主要根據(jù)反饋置數(shù)函數(shù)畫連線圖。

[例7.3.2] 試用 CT74LS161構(gòu)成十進制計數(shù)器

解:CT74LS161實現(xiàn)16進制,可利用其同步置數(shù)控制端來實現(xiàn)十進制計數(shù)。

第一種方案:設(shè)從Q3Q2Q1Q0=0000狀態(tài)開始計數(shù),取D3D2D1D0=0000。

采用置數(shù)控制端獲得N進制計數(shù)器一般都從0開始計數(shù)。

(1)寫出SN-1的二進制代碼為

SN-1=S10-1=S9=1001

(2)寫出反饋歸零(置數(shù))函數(shù)。由于計數(shù)器從0開始計數(shù),因此,應(yīng)寫反饋歸零函數(shù)![]() (7.3.4)

(7.3.4)

(3)畫連線圖。根據(jù)上式和置數(shù)的要求畫十進制計數(shù)器的連線圖,如圖7.3.9(a)所示。

第二種方案:利用后10個狀態(tài)0110~1111,取D3D2D1D0=0110,

反饋置數(shù)信號從進位輸出端CO取得。

討論:為什么?

取狀態(tài)S15=1111,此時正好CO=1,經(jīng)非門,![]() 可取代與非門。

可取代與非門。

電路如圖7.3.9(b)所示。

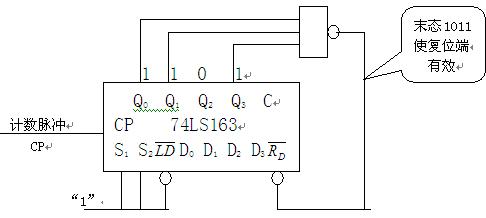

[例7.3.3]試用CT74LS161構(gòu)成十二進制計數(shù)器。

解:設(shè)從Q3Q2Q1Q0=0000狀態(tài)開始計數(shù)。

(1)利用異步置0控制端 實現(xiàn)

① 寫出S12的二進制代碼S12=1100

② 寫出反饋歸零函數(shù)![]() (7.3.5)

(7.3.5)

③ 畫連線圖。如圖7.3.10(a)所示

(2)利用同步置數(shù)控制端 實現(xiàn)

取D3D2D1D0=0000。

① 寫出SN-1的二進制代碼

S12-1=S11=1011

② 寫出反饋歸零置數(shù)函數(shù)![]() (7.3.6)

(7.3.6)

③ 畫連線圖。根據(jù) 的表達式畫連線圖,如圖7.3.10(b)所示。

5.同步二進制加/減計數(shù)器

復(fù)習:JK觸發(fā)器組成的二進制計數(shù)器:

如從Q端輸出信號時,為加法計數(shù)器;

如從![]() 端輸出信號時,則為減法計數(shù)器。

端輸出信號時,則為減法計數(shù)器。

設(shè)計思想:關(guān)鍵是用加/減控制信號將Q端或![]() 端的輸出信號加到相鄰高位T觸發(fā)器的T輸入端上。

端的輸出信號加到相鄰高位T觸發(fā)器的T輸入端上。

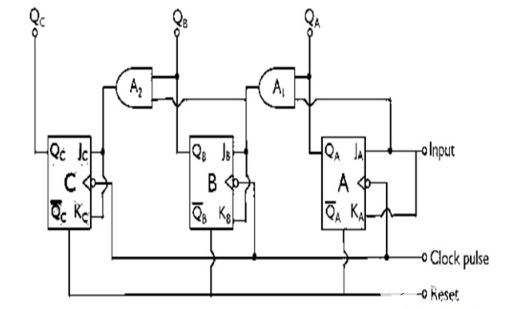

圖7.3.11所示為三位同步二進制加/減計數(shù)器的邏輯圖。

M為加/減控制信號,其值可為1,也可為0。

由圖可得三個T觸發(fā)器的驅(qū)動方程分別為

教材中圖7.3.12所示為由JK觸發(fā)器組成的8421BCD同步十進制加法計數(shù)器的邏輯圖,用下降沿觸發(fā)。

分析它的工作原理。(鞏固同步時序電路的分析方法,可由學生自學)

邏輯功能:與異步十進制計數(shù)器相同。

三、集成同步計數(shù)器

1.集成十進制同步加法計數(shù)器CT74LS160

邏輯功能示意圖。與CT74LS161基本相同,只是型號不一樣。

功能表。與CT74LS161完全相同。

主要功能。與CT74LS161基本相同,只是實現(xiàn)十進制計數(shù)。

進位輸出信號CO=CTT Q3Q0=Q3Q0

[例7.3.4] 試用CT74LS160構(gòu)成七進制計數(shù)器。

解:利用同步置數(shù)控制端歸零。

(1)寫出SN-1的二進制代碼

SN-1=S7-1=S6=0110

(2)寫出反饋歸零(置數(shù))函數(shù)。設(shè)計數(shù)器從0開始計數(shù),為此,應(yīng)取D3D2D1D0=0000,故![]() (7.3.11)

(7.3.11)

(3)畫連線圖。根據(jù)式(7.3.11)和置數(shù)的要求畫連線圖,如圖7.3.14所示。

課后思考題:利用CT74LS160的異步置0控制端 構(gòu)成七進制計數(shù)器。

2.集成十進制同步加/減計數(shù)器CT74LS190

⑶ 主要邏輯功能。(根據(jù)功能表分析,不用寫板書)

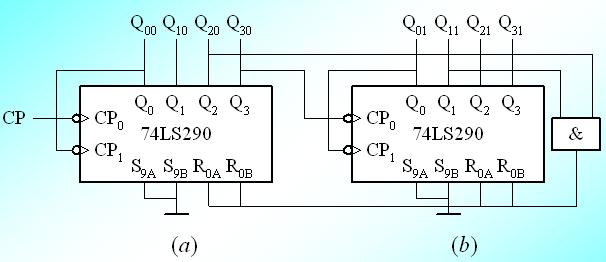

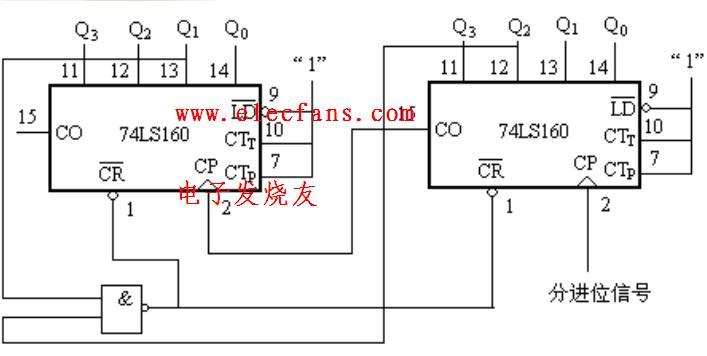

7.3.3B 利用計數(shù)器的級聯(lián)獲得大容量同步N進制計數(shù)器

一、級聯(lián)法

計數(shù)器的級聯(lián)是將多個集成計數(shù)器(如M1進制、M2進制)串接起來,以獲得計數(shù)容量更大的N(=M1×M2)進制計數(shù)器。

一般集成計數(shù)器都設(shè)有級聯(lián)用的輸入端和輸出端。

同步計數(shù)器實現(xiàn)的方法:

低位的進位信號→高位的保持功能控制端(相當于觸發(fā)器的T端)

有進位時,高位計數(shù)功能;無進位時,高位保持功能。

兩片CT74LS160級聯(lián)成100進制同步加法計數(shù)器。

由圖可看出:低位片CT74LS160(1)在計到9以前,其進位輸出CO=Q3Q0=0,高位片CT74LS160(2)的CTT=0,保持原狀態(tài)不變。當?shù)臀黄嫷?時,其輸出CO=1,即高位片的CTT=1,這時,高位片才能接收CP端輸入的計數(shù)脈沖。所以,輸入第10個計數(shù)脈沖時,低位片回到0狀態(tài),同時使高位片加1。

二、反饋歸零法

兩片4位二進制數(shù)加法計數(shù)器CT74LS161級聯(lián)成五十進制計數(shù)器。

現(xiàn)代教學方法與手段:用DLCCAI或EWB演示74LS161、74LS160、74LS190的邏輯功能

電子發(fā)燒友App

電子發(fā)燒友App

評論