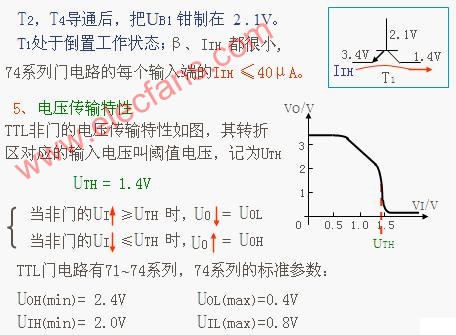

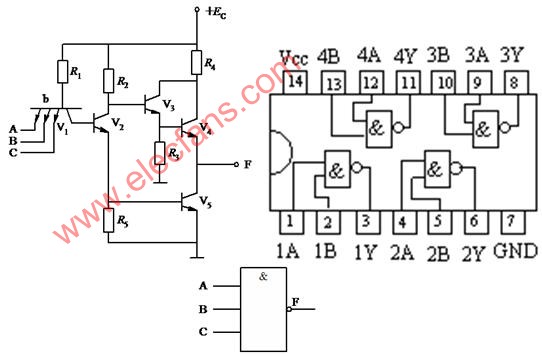

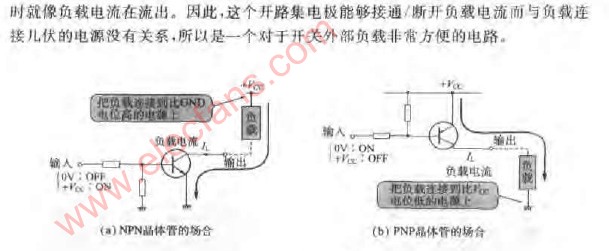

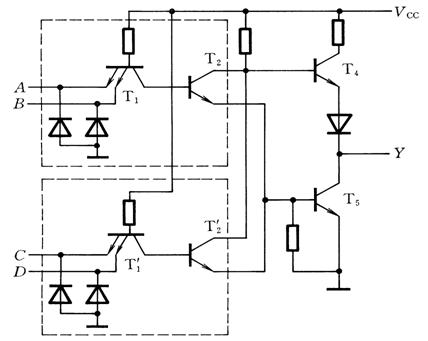

1.TTL或非門

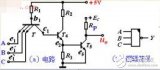

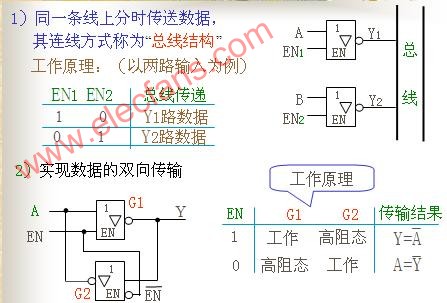

下圖為TTL或非門的邏輯電路及其代表符號。

由圖可見 ,或非邏輯功能是對TTL與非門的結構改進而來,即用兩個 三極管T2A和T2B代替T2。

若兩輸入端為低電平,則T2A和T2B均將截止 ,iB3=0,輸出為高電平。

若A、B兩輸入端中有一個為高電平 ,則T2A或T2B將飽和 ,導致iB3>0,iB3便使T3飽和 ,輸出為低電平。這就實現了或非功能。即 。

。

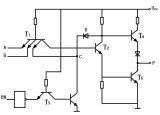

2.集電極開路門

在工程實踐中將兩個門的輸出端并聯以實現與邏輯的功能稱為線與。

考察下圖所示的情況。當將圖中所示的兩個邏輯門的輸出連接在一起,并且當第一個門的輸出為高電平(第一個門的T4導通),第二個門的輸出為低電平(第二個門的T3導通)時,正如圖中紅線所示將出現一個大電流通道,很可能導致晶體管的損壞。

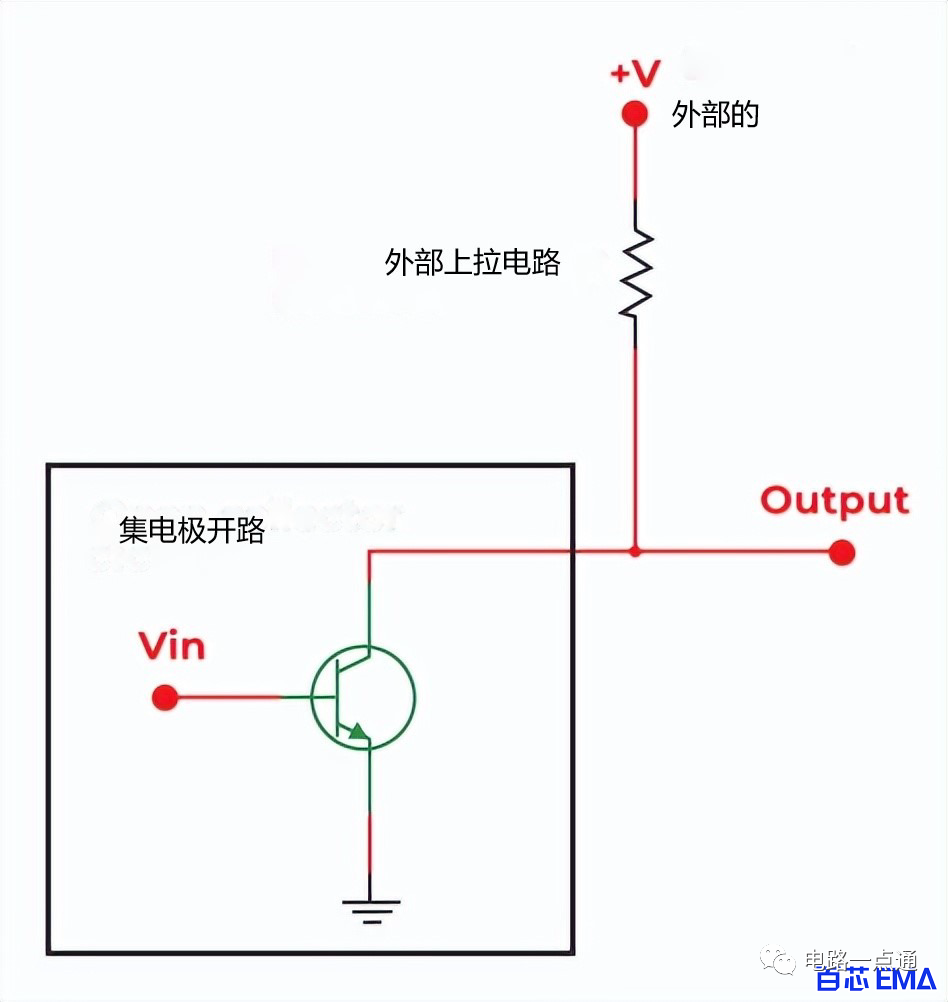

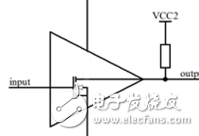

為了避免線與時的產生大電流,可以采用集電極開路門(簡稱OC門)來解決 。所謂集電極開路是指從TTL與非門電路的推挽式輸出級中刪去電壓跟隨器,如下圖所示:

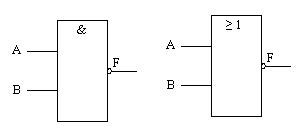

對于一個兩輸入端的OC門,其在電路中的符號可用下圖來表示:

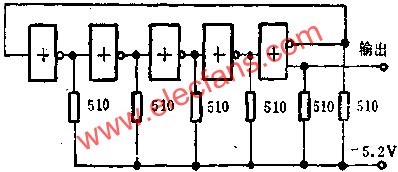

為了實現線與的邏輯功能,可將多個門電路輸出管T3的集電極至電源VCC之間,加一公共的上拉電阻RP,如下圖所示。為了簡明起見,圖中以兩個OC門并聯為例,其中圖標“ ”表示集電極開路之意。

”表示集電極開路之意。

上拉電阻Rp的值可以這樣來計算,主要考慮OC門必須驅動一定的拉電流或灌電流負載。有關這兩類負載的概念前已討論,這里仍然適用 ,所不同的是驅動門是由多個TTL門的輸出端直接并聯而成。當OC門中的一個TTL門的輸出為低電平 ,其他為高電平時,灌電流將由一個輸出BJT(如T1或T2)承擔 ,這是一種極限情況,此時上拉電阻RP具有限制電流的作用。為保證IOL不超過額定值IOL(max),必須合理選用RP的值。例如VCC=5V,RP=1kΩ,則IOL=5mA。

另一方面,由于門電路的輸出、輸入電容和接線電容的存在,RP的大小必將影響OC門的開關速度。RP的值愈大,負載電容的充電時間常數亦愈大,因而開關速度愈慢。RP的最小值RP(min)可按下式來確定

:

RP的最大值RP(max)可按下式來確定:

實際上,RP的值選在RP(min)和RP(max)之間,并且選用靠近RP(min)的標準值。

例:設TTL與非門74LS01(OC)驅動8個74LS04(反相器),試確定一合適大小的上拉電阻RP,設VCC=5V。

由以上計算可知Rp的值可在985Ω至18.75kΩ之間選擇 。為使電路有較快的開關速度,可選用一標準值為1kΩ的電阻器為宜。

集電極開路門除了可以實現多門的線與邏輯關系外,還可用于直接驅動較大電流的負載。

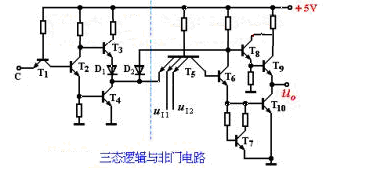

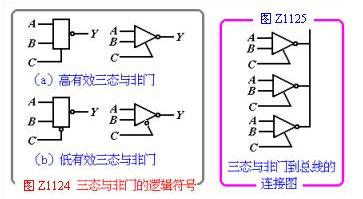

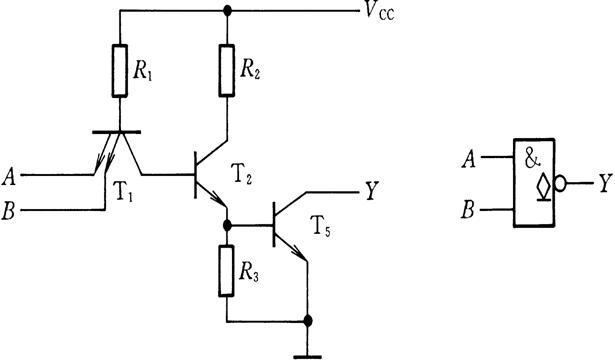

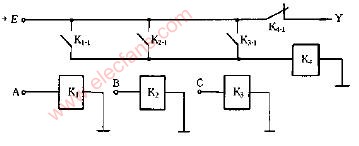

3.三態與非門(TSL)

利用OC門雖然可以實現線與的功能,但外接電阻Rp的選擇要受到一定的限制而不能取得太小,因此影響了工作速度。同時它省去了有源負載,使得帶負載能力下降。為保持推拉式輸出級的優點,還能作線與聯接,人們又開發了一種三態與非門,它的輸出除了具有一般與非門的兩種狀態,即輸出電阻較小的高、低電平狀態外,還具有高輸出電阻的第三狀態,稱為高阻態,又稱為禁止態。

一個簡單的TSL門的電路如上圖所示。其中CS為片選信號輸入端,A、B為數據輸入端。

當CS=1時,TSL門電路中的T5處于倒置放大狀態 ,T6飽和,T7截止,即其集電極相當于開路。此時輸出狀態將完全取決于數據輸入端A、B的狀態,電路輸出與輸入的邏輯關系與一般與非門相同。這種狀態稱為TSL的工作狀態。

當CS=0時T7導通,使T4的基極鉗制于低電平。同時由于低電平的信號送到T1的輸入端,迫使T2和T3截止 。這樣T3和T4均截止,門的輸出端L出現開路,既不是低電平,又不是高電平 ,這就是第三工作狀態。這樣,當CS為高電平時,TSL門的輸出信號送到總線 ,而當CS為低電平時,門的輸出與數據總線斷開,此時數據總線的狀態由其他門電路的輸出所決定。

抗飽和TTL電路是目前傳輸速度較高的一類TTL電路。這種電路由于采用肖特基勢壘二極管SBD鉗位方法來達到抗飽和的效果 ,一般稱為SBDTTL電路(簡稱STTL電路),其傳輸速度遠比基本TTL電路為高。

肖特基勢壘二極管的工作特點如下:

(1)它和PN結一樣,同樣具有單向導電性,這種鋁-硅勢壘二極管導通電流的方向是從鋁到硅。

(2)AL-SiSBD的導通閾值電壓較低,約為0.4~0.5V ,比普通硅PN結約低0.2V。

(3)勢壘二極管的導電機構是多數載流子 ,因而電荷存儲效應很小。

根據前面的學習,我們已經知道,BJT工作在飽和時 ,發射結和集電結都處在正向偏置,集電結正向偏置電壓越大,則表明飽和程度越深。

為了限制BJT的飽和深度,在BJT的基極和集電極并聯上一個導通閾值電壓較低的肖特基二極管,如下圖所示。

當沒有SBD時,隨著基級電壓的升高,電流沿著藍線方向流動。由于SBD的作用,當基級電壓大于0.4V時, SBD首先電導通,電流沿著紅線方向流動(如下圖所示),從而使T的基極電流不會過大(而且使T的集電結正向偏壓將被鉗制在0.4V左右),因此SBD起到抵抗過飽和的作用,因而又將這種電路稱為抗飽和電路,使電路的開關時間大為縮短。

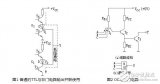

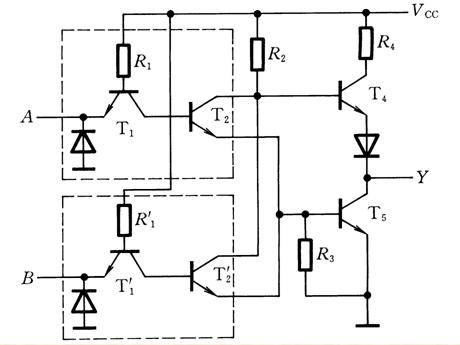

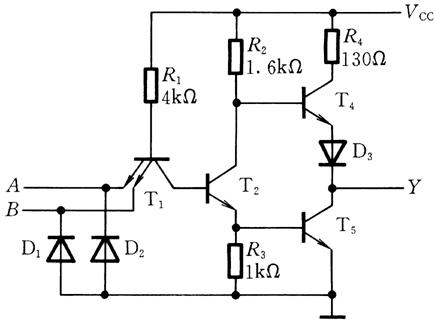

下圖為肖特基TTL(STTL)與非門的典型電路。與基本TTL與非門電路相比,作了若干改進。在基本的TTL電路中 ,T1、T2和T3工作在深度飽和區,管內電荷存儲效應對電路的開關速度影響很大。現在除T4外,其余的BJT均采用SBD鉗位,以達到明顯的抗飽和效果。其次,基本電路中的所有電阻值這里幾乎都減半。這兩項改進導致門電路的開關時間大為縮短。由于電阻值的減小也必然會引起門電路功耗的增加。

STTL門電路還有以下三點對基本TTL電路的性能作了改進:

(1)二極管D被由T4和T5所組成的復合管所代替,當輸出由低電平向高電平過渡時,由于復合管電路的電流增益很大,輸出電阻很小

,從而減小了電路對負載電容的充電時間。

(2)電路輸入端所加的SBD—DA和DB,用來減小由門電路之間的連線而引起的雜散信號。

(3)基本電路中的Re2(1kΩ)改為由T6與Rc6 、Rb6的組合電路所代替。這個組合電路是有源非線性電阻。當其兩端的電壓(發射極e2對地)較低時,呈現很大的電阻,而當其兩端的電壓達到0.7V左右時,則呈現很小的電阻。這樣,當與非門的全部輸入端由低電平轉向高電平時,有源電阻開始不導通使T3很快達到飽和;反之,當電路的全部輸入端(或其中之一)由高電平轉向低電平時,T2和T3將截止,由于T3飽和時,VBE=0.7V,在轉換開始的瞬間,有源電阻的阻值很小

T3基區存儲的電荷通過此低阻回路很快消散。由于這個緣故,有源非線性電路稱為有源下拉電路 ,它與有源上拉電路是對應的 。意即將 VBE3從0.7 V很快拉到0V,從而使輸出電壓很快升高,即提高了開關速度。

基于上述特點,STTL與非門具有較為理想的傳輸特性。與基本TTL反相器的傳輸特性相比,C點不再存在了,由B點直接下降到D點,即傳輸特性變化非常陡峭,見下圖。

除典型的肖特基型(STTL)外,尚有低功耗肖特基型(LSTTL)、先進的肖特基型(ASTTL),先進的低功耗型(ALSTTL)等,它們的技術參數各有特點,是在TTL工藝的發展過程中逐步形成的。

TTL門電路的各種系列的性能比較

|

電子發燒友App

電子發燒友App

評論