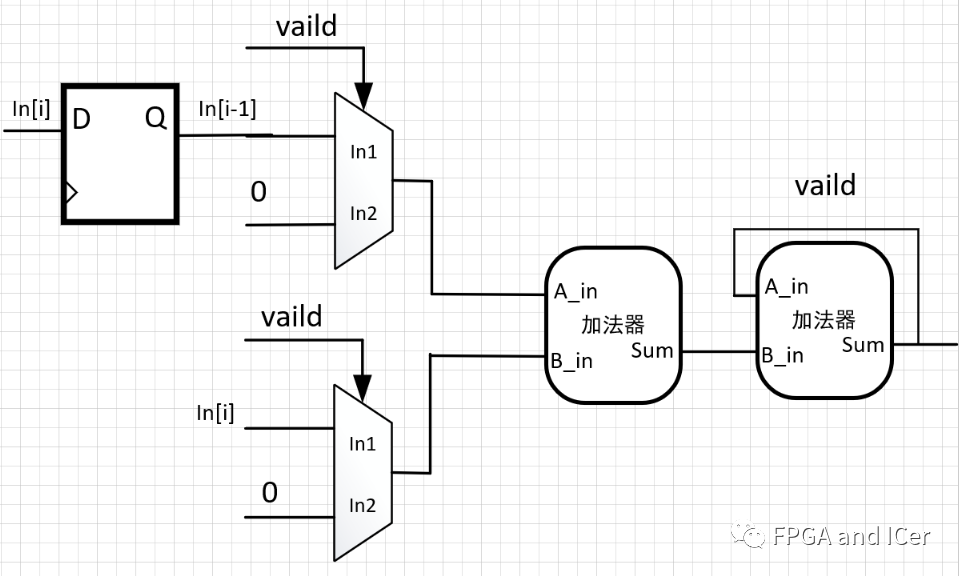

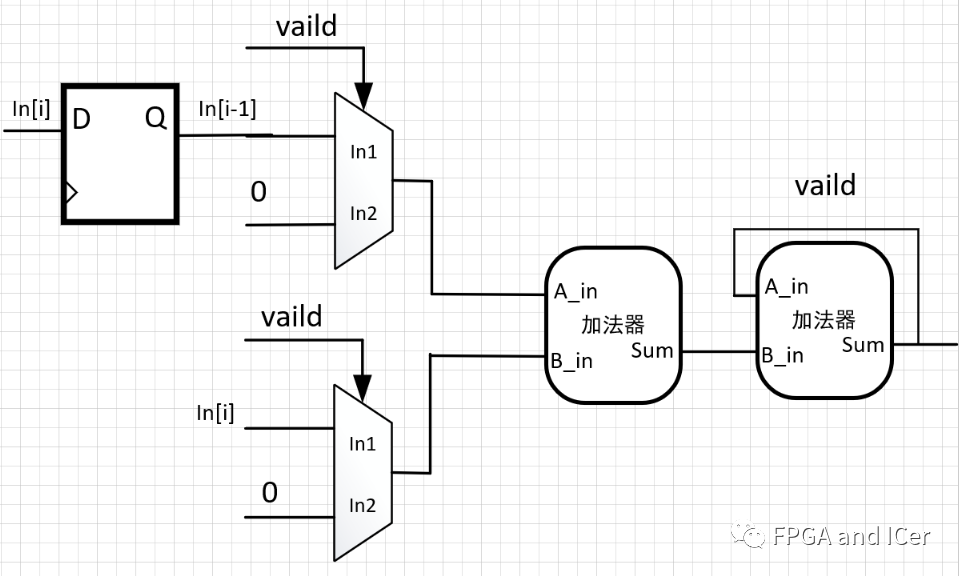

實現(xiàn)累加器的加法器例化的個數(shù)。按照原文大佬的設(shè)計方法,因為數(shù)據(jù)連續(xù)且加法器的延遲周期是2,使用使用一個實現(xiàn)累加,會有一半的數(shù)據(jù)丟失。

2023-06-02 16:35:40 1029

1029

模式下高達12 GSPS。高動態(tài)范圍和帶寬使這些DAC非常適合最嚴苛的高速射頻(RF) DAC應(yīng)用。DDS由一組32個32位數(shù)控振蕩器(NCO)組成,各帶相位累加器

2023-03-10 16:10:39

此DDS器件是一款數(shù)控振蕩器,在單個CMOS芯片內(nèi)集成了一個相位累加器、一個SINE查找表以及一個10位數(shù)模轉(zhuǎn)換器,提供相位調(diào)制和頻率調(diào)制兩種調(diào)制能力。 最高支持25 MHz時鐘速率。頻率

2023-03-09 16:40:21

此DDS器件是一款數(shù)控振蕩器,在單個CMOS芯片內(nèi)集成了一個相位累加器、一個正弦查找表以及一個10位數(shù)模轉(zhuǎn)換器,提供相位調(diào)制和頻率調(diào)制兩種調(diào)制能力。 最高支持50 MHz時鐘速率。頻率

2023-02-15 09:43:52

AD9832是一款數(shù)控振蕩器,在單個CMOS芯片內(nèi)集成了一個相位累加器、一個正弦查找表以及一個10位數(shù)模轉(zhuǎn)換器(DAC),提供相位調(diào)制和頻率調(diào)制兩種調(diào)制能力。 最高支持25 MHz時鐘速率

2023-02-15 09:41:06

AD9835是一款數(shù)控振蕩器,在單個CMOS芯片內(nèi)集成了一個相位累加器、一個COS查找表以及一個10位數(shù)模轉(zhuǎn)換器,提供相位調(diào)制和頻率調(diào)制兩種調(diào)制能力。 最高支持50 MHz時鐘速率。頻率

2023-02-15 09:38:09

模式下高達12 GSPS。高動態(tài)范圍和帶寬使這些DAC非常適合最嚴苛的高速射頻(RF) DAC應(yīng)用。DDS由一組32個32位數(shù)控振蕩器(NCO)組成,各帶相位累加器

2023-02-14 15:24:06

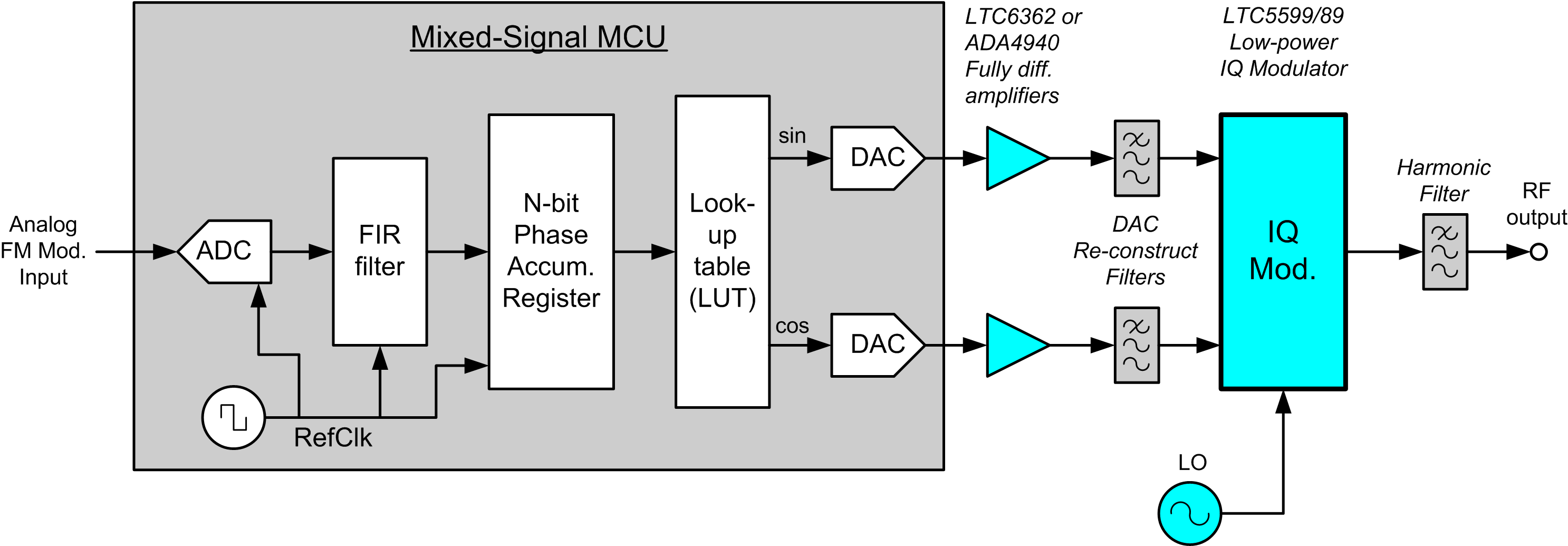

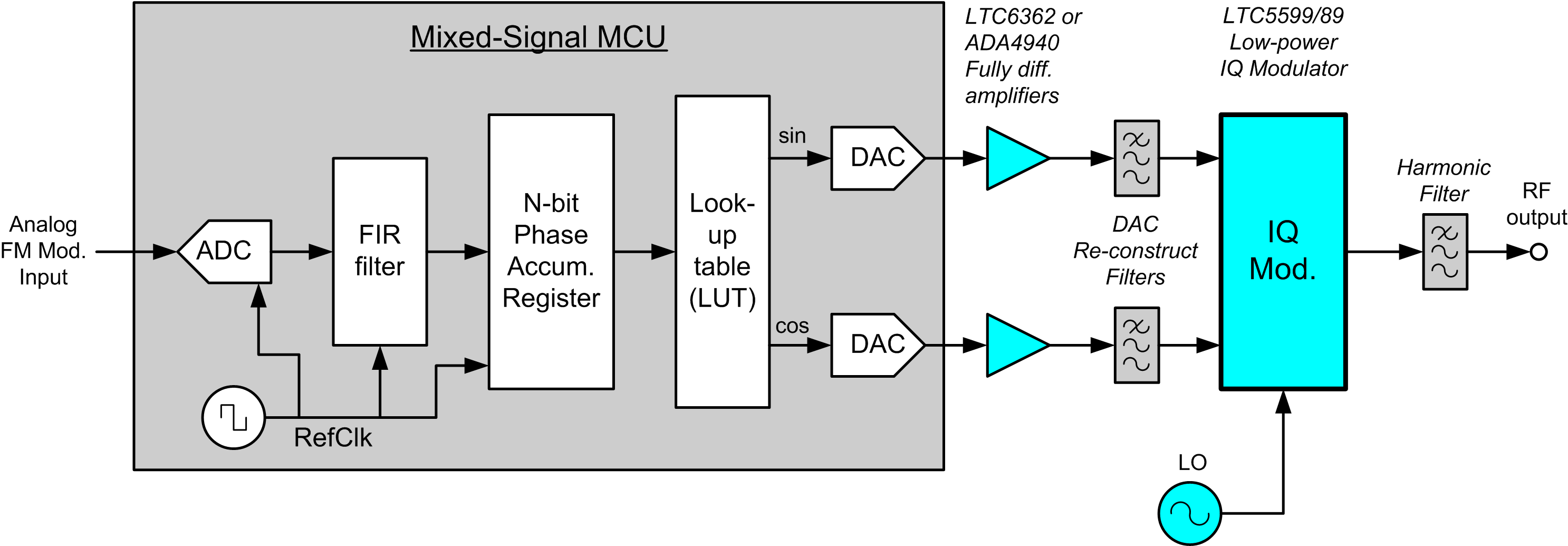

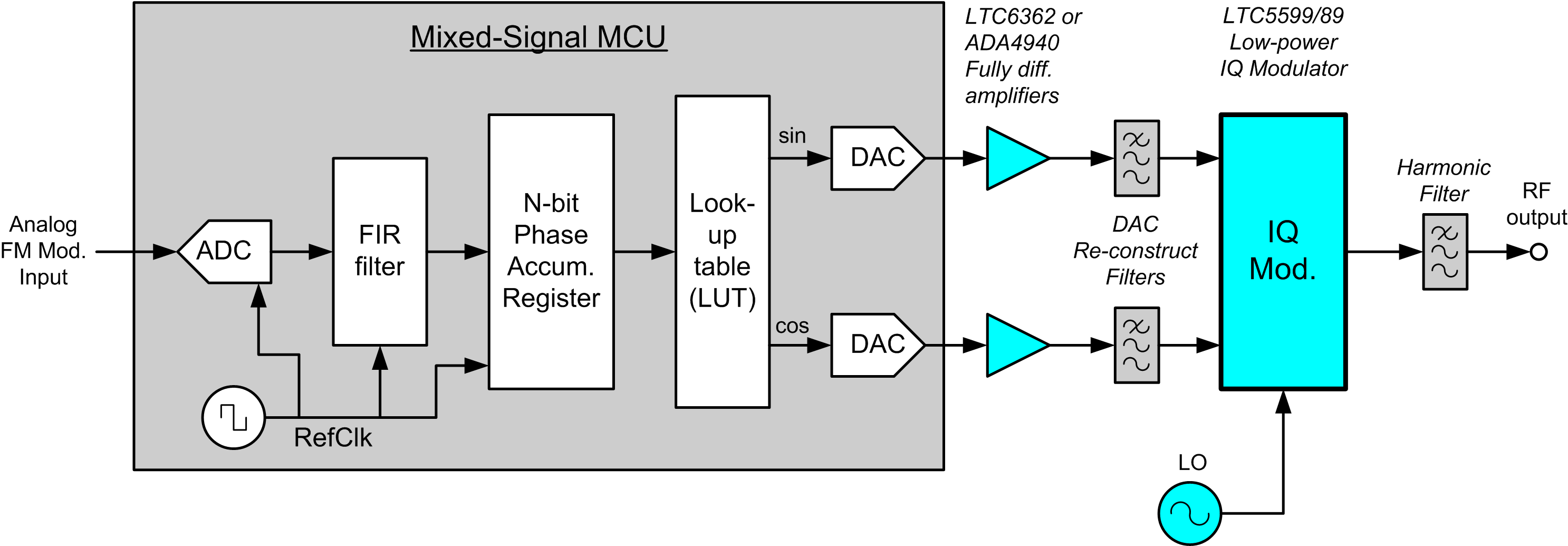

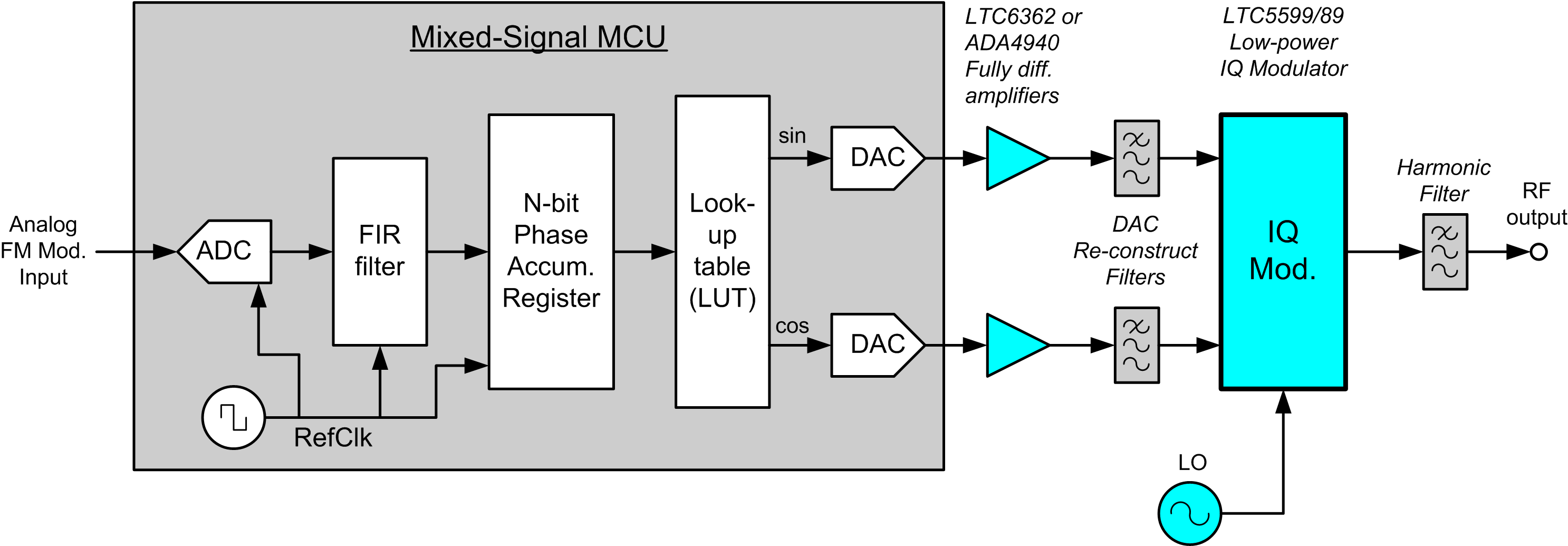

在為通信應(yīng)用生成模擬或數(shù)字FM時,IQ調(diào)制器可提供多功能的低功耗解決方案。示例設(shè)計將展示如何使用混合信號MCU執(zhí)行相位累加器和正弦/余弦查找表功能。證明了 IQ 調(diào)制器精度和線性度的重要性。

2023-01-03 14:20:06 855

855

相位累加器寄存器的輸出代表生成波形的當前相位。由于相位到正弦或相位到余弦映射器引擎,每個離散累加器輸出相位值隨后被轉(zhuǎn)換為幅度正弦或余弦數(shù)據(jù)或樣本。

2022-07-24 16:51:14 935

935

本設(shè)計相位累加器設(shè)定為32位,正弦表數(shù)據(jù)為8位,因此在ROM查找表里的容量為232×8=34,359,738,368(bits),在理論上這可以獲得精細的頻率分辨率,但是這么大容量的數(shù)據(jù)卻很難實現(xiàn)。

2022-06-21 10:54:35 5249

5249

相位累加器寄存器的輸出代表生成波形的當前相位。由于相位到正弦或相位到余弦映射器引擎,每個離散累加器輸出相位值隨后被轉(zhuǎn)換為幅度正弦或余弦數(shù)據(jù)或樣本。

2022-06-06 14:58:19 1024

1024

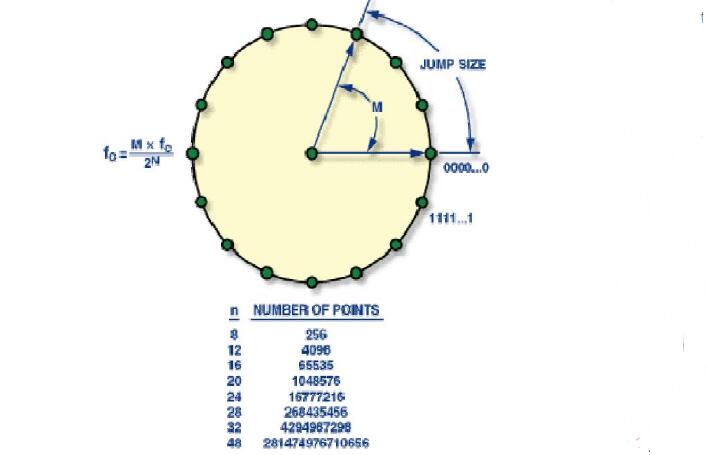

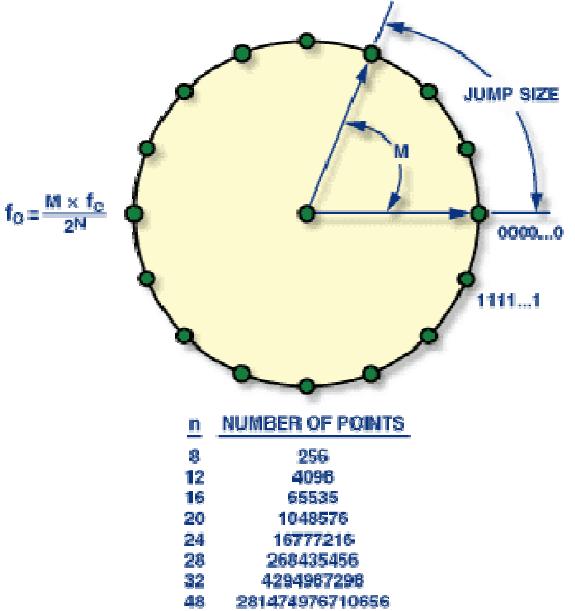

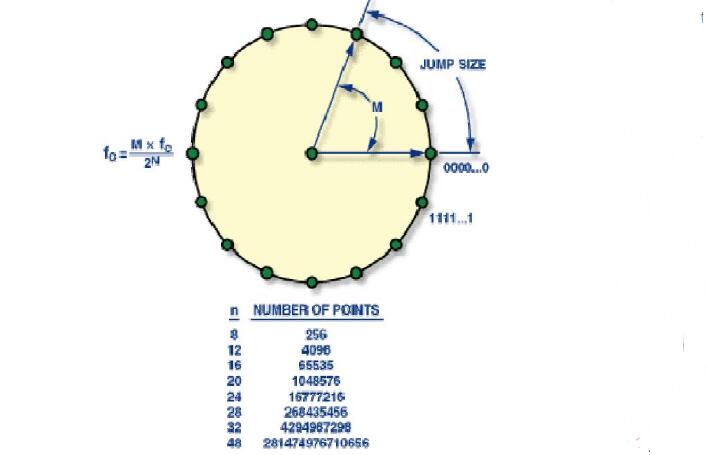

精細的頻率調(diào)節(jié)。采用這種方法設(shè)計的信號源可工作于調(diào)制狀態(tài),可對輸出電平進行調(diào)節(jié),也可輸出各種波形。一個完整周期的函數(shù)波形被存儲在上面所示的存儲器查找表中。相位累加器跟蹤輸出函數(shù)的電流相位。為了輸出一個非常低的頻率,采樣樣本之間的差相位(Δ)將非常小。例

2021-12-02 18:51:18 28

28 累加器A與ACC區(qū)別累加器寫成A或ACC在51匯編語言指令中是有區(qū)別的。ACC在匯編后的機器碼必有一個字節(jié)的操作數(shù),即累加器的字節(jié)地址E0H,A在匯編后則隱含在指令操作碼中。所以在指令中A不能

2021-11-23 09:06:01 98

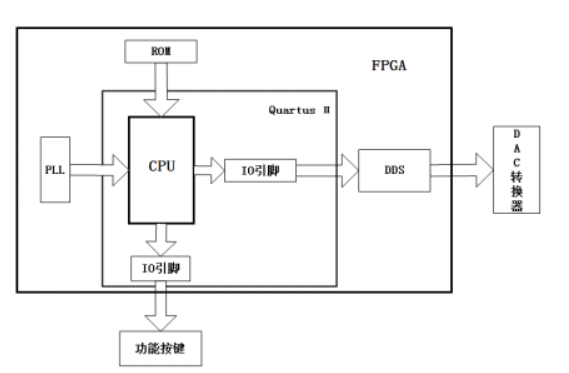

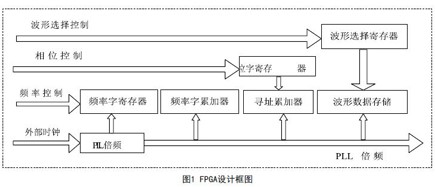

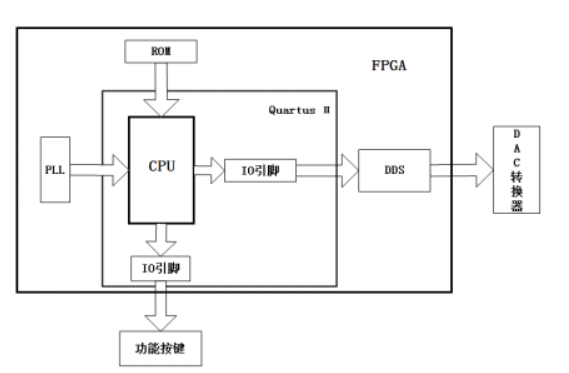

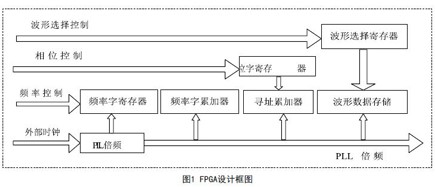

98 可編程邏輯器件設(shè)計環(huán)境,其功能更為強大。用Max+plusII設(shè)計DDS系統(tǒng)數(shù)字部分最簡單的方法是采用原理圖輸入。相位累加器調(diào)用lmp_add_sub加減法器模擬,相位累加器的好壞將直接影響到整個系統(tǒng)

2011-07-13 14:13:56

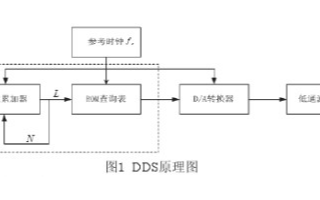

正弦信號產(chǎn)生采用DDS技術(shù),以FGPA方式實現(xiàn),DDS的基本結(jié)構(gòu)由參考時鐘、相位累加器、存儲器(ROM)、DAC和濾波器(LPF)組成,其組成如圖2所示。

2021-05-20 10:20:40 1604

1604

本文檔的主要內(nèi)容詳細介紹的是Arduino的累加器實驗程序和工程文件免費下載。

2021-01-13 17:24:00 5

5 在大部分的教科書中,都會提到如何分頻,包括奇數(shù)分頻,偶數(shù)分頻,小數(shù)分頻等。 1、DDS相位累加器 (1)DDS合成流程 首先講述DSS(直接頻率合成法)的原理。 DDS是重要的頻率合成方法,在波形

2020-11-29 10:19:00 3728

3728 累加器 (accumulator) 是一種寄存器,用來儲存計算產(chǎn)生的中間結(jié)果。如果沒有像累加器這樣的寄存器,那么在每次計算 (加法,乘法,移位等等) 后就必須要把結(jié)果寫回到 內(nèi)存,也許馬上就得讀回來。然而存取主存的速度是比從算術(shù)邏輯單元到有直接路徑的累加器存取更慢。

2020-10-14 16:00:00 8

8 圖5.FTW最右邊非零位的位置確定了理論上SFDR的最差水平。由Nicholas修改的相位累加器解決了采用任何N值的問題,并且使NCO的SFDR最大。

2020-10-07 10:33:00 1580

1580

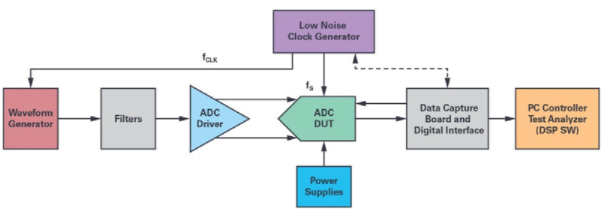

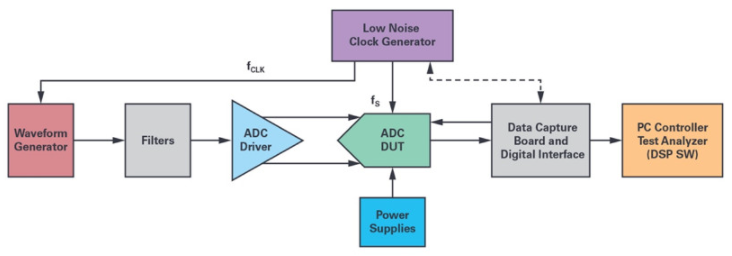

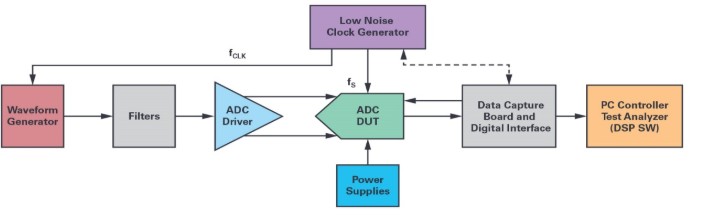

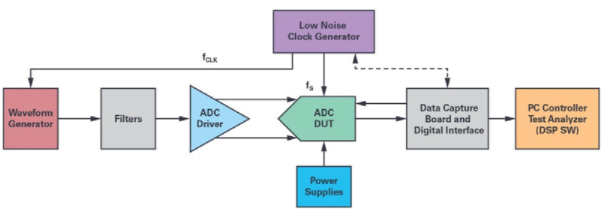

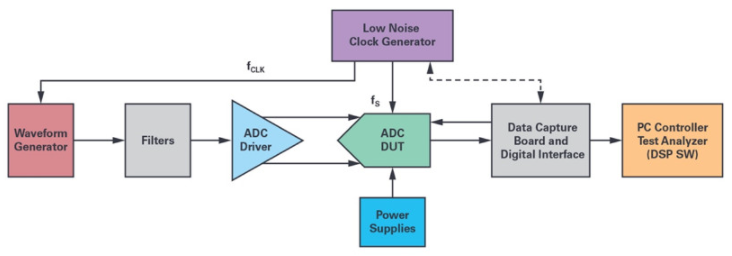

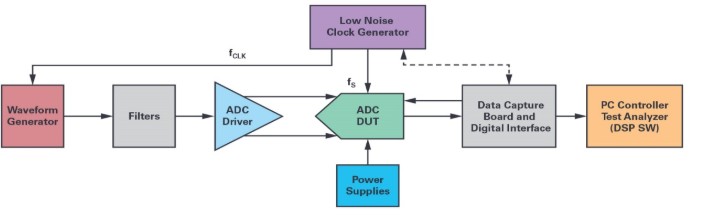

的某種波形。 在測試測量領(lǐng)域有另一個概念 - AWG(任意波形發(fā)生器)是跟DDS緊密相關(guān)的,波形發(fā)生器未必一定采用DDS的方式,但任意波形的產(chǎn)生就離不開DDS了。 DDS可以生成任意波形 - 比如心狀波形 DDS的基本原理如下面的框圖,主要由以下幾個部

2020-09-24 14:20:24 11474

11474 的產(chǎn)生原理是基于奈奎斯特采樣定律, 先對模擬信號采集,經(jīng)過量化后存入查表中, 再由相位累加器產(chǎn)生地址, 通過對查表尋址,得到離散化波形序列,最后經(jīng)過D/A 轉(zhuǎn)換輸出模擬波形。方波的產(chǎn)生是在輸出波形的前半周期輸出低電平, 后半周期輸

2020-08-25 16:32:00 4

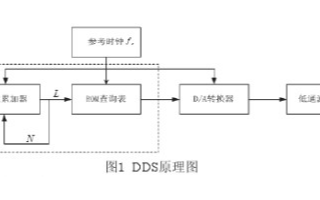

4 DDS的原理如圖1所示,包含相位累加器、波形存儲器(ROM)、數(shù)模轉(zhuǎn)換器(DAC)和低通濾波器4個部分。在參考時鐘的驅(qū)動下,相位累加器對頻率控制字N位進行累加,得到的相位碼L作為ROM的地址,根據(jù)地址ROM輸出相應(yīng)幅度的波形碼,然后經(jīng)過DAC生成階梯波形,經(jīng)低通濾波器后得到所需要的連續(xù)波形。

2020-01-14 16:27:27 2476

2476

假設(shè)系統(tǒng)時鐘為Fc,輸出頻率為Fout。每次轉(zhuǎn)動一個角度360°/2N, 則可以產(chǎn)生一個頻率為Fc/2N 的正弦波的相位遞增量。那么只要選擇恰當?shù)念l率控制字M,使得 Fout / Fc= M / 2N,就可以得到所需要的輸出頻率Fout,

2019-07-22 08:52:56 6983

6983 在系統(tǒng)時鐘脈沖的作用下,相位累加器不停累加,即不停查表,把波形數(shù)據(jù)送到D/A轉(zhuǎn)換器轉(zhuǎn)換成模擬量輸出,從而合成波形。濾波器則進一步平滑D/A轉(zhuǎn)換器輸出的近似正弦波的鋸齒階梯波,同時衰減不必要的雜散信號。

2019-05-12 09:41:58 3495

3495

DDS頻率合成器具有頻率分辨率高,輸出頻點多,可達2N個頻點(假設(shè)DDS相位累加器的字長是N);頻率切換速度快,可達us量級;頻率切換時相位連續(xù)的優(yōu)點,可以輸出寬帶正交信號,其輸出相位噪聲低,對參考頻率源的相位噪聲有改善作用;可以產(chǎn)生任意波形;全數(shù)字化實現(xiàn),便于集成,體積小,重量輕。

2019-04-24 08:30:00 2795

2795

為通信應(yīng)用生成模擬或數(shù)字FM時,IQ調(diào)制器提供通用的低功耗解決方案。示例設(shè)計將顯示混合信號MCU如何用于執(zhí)行相位累加器和正弦/余弦查找表功能。證明了IQ調(diào)制器精度和線性度的重要性。

2019-04-15 08:18:00 5007

5007

本系統(tǒng)采用數(shù)字合成芯片AD9850完成整個系統(tǒng)設(shè)計AD9850內(nèi)含可編程DDS系統(tǒng)和高速比較器,能實現(xiàn)全數(shù)字編程控制的頻率合成。可編程DDS系統(tǒng)的核心是相位累加器,它由一個加法器和一個N位相位寄存器

2018-11-19 08:00:00 36

36 DDS由相位累加器、只讀存儲器(ROM)、數(shù)模轉(zhuǎn)換器(DAC)和低通濾波器(LPF)組成。DDS的關(guān)鍵部分是相幅轉(zhuǎn)換部分,根據(jù)相幅轉(zhuǎn)換方式的不同,DDS大致可分為兩大類:(1)ROM查詢表法。ROM

2018-10-07 11:50:50 3000

3000

設(shè)計時,只要將波形的一個周期(周期波形)中分成N段輸出就可以了。???????? DDS的實現(xiàn)一般都是由頻率控制器、相位累加器和波形存儲器構(gòu)成(如圖3)。?圖3?剛剛開始的時候百度到這個信息,筆者也不太

2018-08-22 19:18:00 79

79 DDS頻率合成器具有頻率分辨率高,輸出頻點多,可達2N個頻點(假設(shè)DDS相位累加器的字長是N);頻率切換速度快,可達us量級;頻率切換時相位連續(xù)的優(yōu)點,可以輸出寬帶正交信號,其輸出相位噪聲低,對參考頻率源的相位噪聲有改善作用;可以產(chǎn)生任意波形;全數(shù)字化實現(xiàn),便于集成,體積小,重量輕。

2018-06-11 09:49:00 4780

4780

直接數(shù)字頻率合成(DDS)技術(shù)是20世紀70年代以來推出的一種頻率合成法。隨著數(shù)字集成電路和微電子技術(shù)發(fā)展,DDS技術(shù)已廣泛應(yīng)用于電子、通信、雷達等領(lǐng)域。DDS是通過改變頻率控制字來改變相位累加器

2018-06-07 08:07:00 18101

18101 在中央處理器中,累加器(accumulator) 是一種寄存器,用來儲存計算產(chǎn)生的中間結(jié)果。如果沒有像累加器這樣的寄存器,那么在每次計算 (加法,乘法,移位等等) 后就必須要把結(jié)果寫回到內(nèi)存,也許馬上就得讀回來。然而存取主存的速度是比從算術(shù)邏輯單元到有直接路徑的累加器存取更慢。

2018-04-11 16:46:27 20510

20510 本文首先對寄存器、累加器、暫存器做個哥介紹,其次解答了累加器是不是寄存器,最后闡述了寄存器、累加器、暫存器的區(qū)別。

2018-04-11 16:31:42 8860

8860 本文開始介紹了累加器的概念和相位累加器原理,其次介紹了累加器的作用,最后介紹了流水線相位累加器的設(shè)計與累加定時器在PLC控制程序中的應(yīng)用。

2018-04-11 11:40:16 65911

65911

DDS的具體工作過程如圖1所示。N位相位累加器由N位加法器和N位累加寄存器組成。每來一個時鐘脈沖,N位加法器將頻率控制字K與N位累加寄存器輸出的累加相位數(shù)據(jù)相加,并把相加后的結(jié)果送至累加寄存器的輸入

2017-11-24 15:06:42 7012

7012

導(dǎo)航數(shù)字信號源的系統(tǒng)設(shè)計,完整參考方案 本無線電導(dǎo)航數(shù)字信號源總體設(shè)計思想采用直接數(shù)字頻率合成器(DDS)技術(shù),設(shè)計精確的時鐘參考源精度、頻率和相位累加器字長和正弦波函數(shù)表,實現(xiàn)研制技術(shù)要求的輸出頻率變化范圍、頻

2017-11-15 13:59:17 21

21 AD9854正交數(shù)字信號發(fā)生器是一款有著廣泛應(yīng)用的非常靈活的器件。器件包括一個48位的相位累加器,可編程基準時鐘乘法器,反辛格濾波器,數(shù)字乘法器,兩個12位/300HZ數(shù)模轉(zhuǎn)換器,一個高速模擬比較器和內(nèi)部邏輯電路。這款高度集成的器件可以用作本機震蕩發(fā)生器,靈活的時鐘發(fā)生器和FSK/BPSK調(diào)制器。

2017-11-03 18:31:00 3785

3785

直接數(shù)字頻率合成(DDSDigital Direct Frequency Synthesis)技術(shù)是一種新的頻率合成方法 DDS是一種全數(shù)字化的頻率合成器,由相位累加器、波形ROM、D/A轉(zhuǎn)換器和低通濾波器構(gòu)成。時鐘頻率給定后,

2011-04-06 16:34:30 45

45 在利用可編程電路實現(xiàn)高速直接數(shù)字合成的基礎(chǔ)上,提出了一種通過實時改變直接數(shù)字合成頻率控制字,直接實現(xiàn)波形頻率調(diào)制的方法。重點對高速相位累加器、FM、掃頻、FSK等調(diào)

2009-02-28 16:45:28 26

26 TMS320F24X 指令集累加器、算術(shù)與邏輯指令附件

TMS320F24X 指令集累加器、算術(shù)與邏輯指令

助記

2008-10-17 22:41:11 1024

1024

電子發(fā)燒友App

電子發(fā)燒友App

評論