實現模2除法的線路

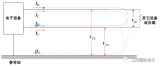

循環校驗碼的核心邏輯線路是實現模2除的線路。按照前面介紹的方法,可將模2除的步驟分解歸納為兩種操作:如果被除數或者余數最高位的值為0,直接將余數左移一位;如果被除數或部分余數最高位的值為1,用生成多項式G(x)作模2減,然后余數左移一位。

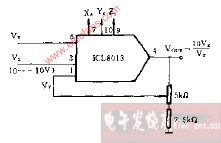

圖2.2 實現模2除的邏輯圖

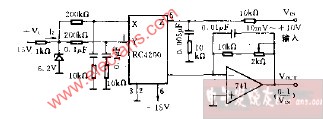

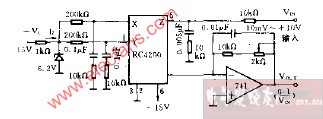

對前述用G(x)=1011產生(7,4)校驗碼的例子,可采用圖2.2所示線路,產生3位的余數。圖中的模2減用異或門實現,左移一位由移位寄存器實現;用異或門的輸出控制左邊一位寄存器的D輸入端,可同時實現模2減和左移。用最左一位的取值控制是否做模2減,當其為1時,減去的數就是生成多項式G(x)=1011。這里,被除數D是逐位串行送到移位寄存器的,且由CP脈沖同步。

圖2.3 實現G(x)=1011的線性(7,4)分組碼模2除線路圖

由于G(x)固定不變,故G2可省去;只求三位余數,故G3和T0也失去意義。圖2.2可簡化為圖2.3(a)。

對圖2.3(a)的線路來說,在發送端,輸入信息碼D為1100,串行從低位送入,先左移三位形成1100000,再通過7步模2除,可在移位寄存器 T3 T2 T1 中得到余數010;在接收端,對7位的CRC碼字1100010,執行7步模2除之后,若在 T3 T2 T1 得到000,表明CRC碼字中無任何一位出錯;若余數不為全0,可根據表2.4確定出錯位置。

設Ti為T3T2T1某觸發器當前狀態,Ti'為次態,可用次態方程表示圖2.3(a)的模2除電路: T3'=T2, T2'=T3⊕T1 , T1'=T3⊕D。

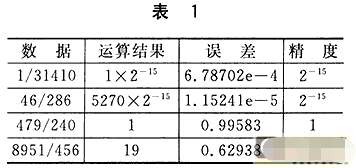

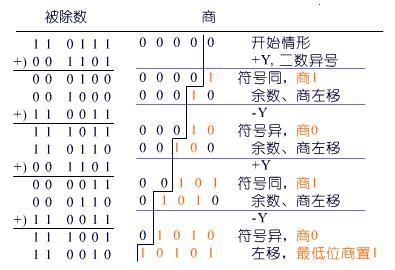

分別用被除數1100000和1010000驗證取得余數為010和011的工作過程,見表2.6。讀者可用模2除豎式計算各步結果并與之比較。

表2.6 圖2.3(a)線路工作過程舉例

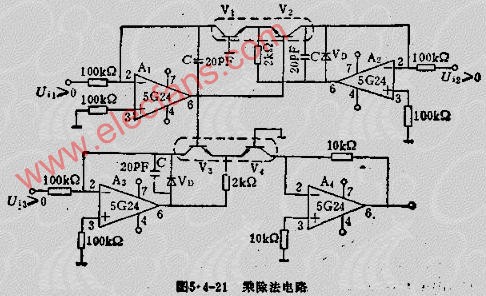

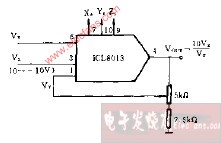

可以將圖2.3(a)的線路稍加變化,即得到圖2.3(b)的線路,用作為G(x)=1011的系統線性(7,4)分組碼的編碼線路。待編碼信息D由高位端送入,CRC碼由T送出。開始時,開關K1閉合,K2打到b位置,輸入信息進入除法線路的同時送到T輸出。經過4步之后,T3T2T1即為余數。然后,K1斷開,K2打到a,T3T2T1只有移位功能,正好將余數拼接在信息碼后經T送出。圖2.3(b)中,開關K1閉合,K2打到b,T3T2T1及輸出T可表達為: T=b=D, T3' =T2 , T2' =T1⊕T3⊕D, T1'=T3⊕D 。 當開關K1斷開,K2打到a,T3T2T1及輸出T可表達為: T=a=T3⊕D=T3(D為0), T3'=T2, T2' =T1, T1' =0。信息碼為1100和1010取得的CRC碼1100010和1010011的工作過程見表2.7。

表2.7 圖2.3(b)線路編碼過程舉例

循環校驗碼的核心邏輯線路是實現模2除的線路。按照前面介紹的方法,可將模2除的步驟分解歸納為兩種操作:如果被除數或者余數最高位的值為0,直接將余數左移一位;如果被除數或部分余數最高位的值為1,用生成多項式G(x)作模2減,然后余數左移一位。

圖2.2 實現模2除的邏輯圖

對前述用G(x)=1011產生(7,4)校驗碼的例子,可采用圖2.2所示線路,產生3位的余數。圖中的模2減用異或門實現,左移一位由移位寄存器實現;用異或門的輸出控制左邊一位寄存器的D輸入端,可同時實現模2減和左移。用最左一位的取值控制是否做模2減,當其為1時,減去的數就是生成多項式G(x)=1011。這里,被除數D是逐位串行送到移位寄存器的,且由CP脈沖同步。

圖2.3 實現G(x)=1011的線性(7,4)分組碼模2除線路圖

由于G(x)固定不變,故G2可省去;只求三位余數,故G3和T0也失去意義。圖2.2可簡化為圖2.3(a)。

對圖2.3(a)的線路來說,在發送端,輸入信息碼D為1100,串行從低位送入,先左移三位形成1100000,再通過7步模2除,可在移位寄存器 T3 T2 T1 中得到余數010;在接收端,對7位的CRC碼字1100010,執行7步模2除之后,若在 T3 T2 T1 得到000,表明CRC碼字中無任何一位出錯;若余數不為全0,可根據表2.4確定出錯位置。

設Ti為T3T2T1某觸發器當前狀態,Ti'為次態,可用次態方程表示圖2.3(a)的模2除電路: T3'=T2, T2'=T3⊕T1 , T1'=T3⊕D。

分別用被除數1100000和1010000驗證取得余數為010和011的工作過程,見表2.6。讀者可用模2除豎式計算各步結果并與之比較。

|

步驟 |

信息碼1100 |

信息碼1010 |

|

輸入D TTT |

輸入D TTT | |

|

初態 1 2 3 4 5 6 7 |

0 000 1 001 1 011 0 110 0 111 0 101 0 001 0 010 |

0 000 1 001 0 010 1 101 0 001 0 010 0 100 0 011 |

可以將圖2.3(a)的線路稍加變化,即得到圖2.3(b)的線路,用作為G(x)=1011的系統線性(7,4)分組碼的編碼線路。待編碼信息D由高位端送入,CRC碼由T送出。開始時,開關K1閉合,K2打到b位置,輸入信息進入除法線路的同時送到T輸出。經過4步之后,T3T2T1即為余數。然后,K1斷開,K2打到a,T3T2T1只有移位功能,正好將余數拼接在信息碼后經T送出。圖2.3(b)中,開關K1閉合,K2打到b,T3T2T1及輸出T可表達為: T=b=D, T3' =T2 , T2' =T1⊕T3⊕D, T1'=T3⊕D 。 當開關K1斷開,K2打到a,T3T2T1及輸出T可表達為: T=a=T3⊕D=T3(D為0), T3'=T2, T2' =T1, T1' =0。信息碼為1100和1010取得的CRC碼1100010和1010011的工作過程見表2.7。

表2.7 圖2.3(b)線路編碼過程舉例

|

步驟 |

信息碼1100 |

信息碼1010 |

|

輸入D TTT 輸出T |

輸入D TTT 輸出T | |

|

初態 1 2 3 4 5 6 7 |

0 000 0 1 011 1 1 101 1 0 001 0 0 010 0 0 100 0 0 000 1 0 000 0 |

0 000 0 1 011 1 0 110 0 1 100 1 0 011 0 0 110 0 0 100 1 0 000 1 |

電子發燒友App

電子發燒友App

評論