在高速設計中,如何解決信號的完整性問題?

- 完整(13395)

相關推薦

基于信號完整性分析的高速數字PCB的設計方法

業界中的一個熱門課題。基于信號完整性計算機分析的高速數字PCB板設計方法能有效地實現PCB設計的信號完整性。 1. 信號完整性問題概述 信號完整性(SI)是指信號在電路中以正確的時序和電壓作出響應

2008-06-14 09:14:27

pcb信號完整性詳解

pcb信號完整性詳解 隨著電子領域技術日新月異的發展,高速電路已經成為了電路設計的重要領域之一。在高速電路中,信號完整性顯得尤為重要。在設計PCB電路時,信號完整性是一個必須考慮的因素。那么

2023-09-08 11:46:58 399

399

399

399什么是信號完整性?

業界經常流行這么一句話:“有兩種設計師,一種是已經遇到了信號完整性問題,另一種是即將遇到信號完整性問題”。固態硬盤作為一種高集成度的高時鐘頻率的硬件設備,信號完整性的重要性不言而喻。借著這句話本文主要跟大家聊下信號完整性的一些基本內容。

2023-06-27 10:43:26 632

632

632

632

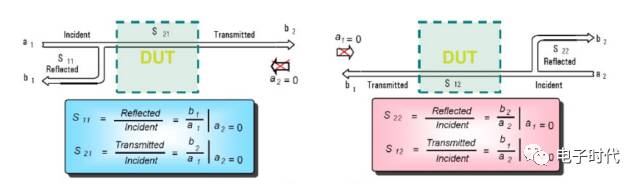

S參數:信號完整性的風象標

隨著速率的不斷提高,信號能夠在鏈路中傳輸的難度越來越大,信號質量會不斷下降,我們把高速信號在傳輸中遇到各種問題統稱為信號完整性問題。

2023-06-21 14:17:56 634

634

634

634

如何將頻域和時域建立聯系方便的分析解決信號完整性問題?

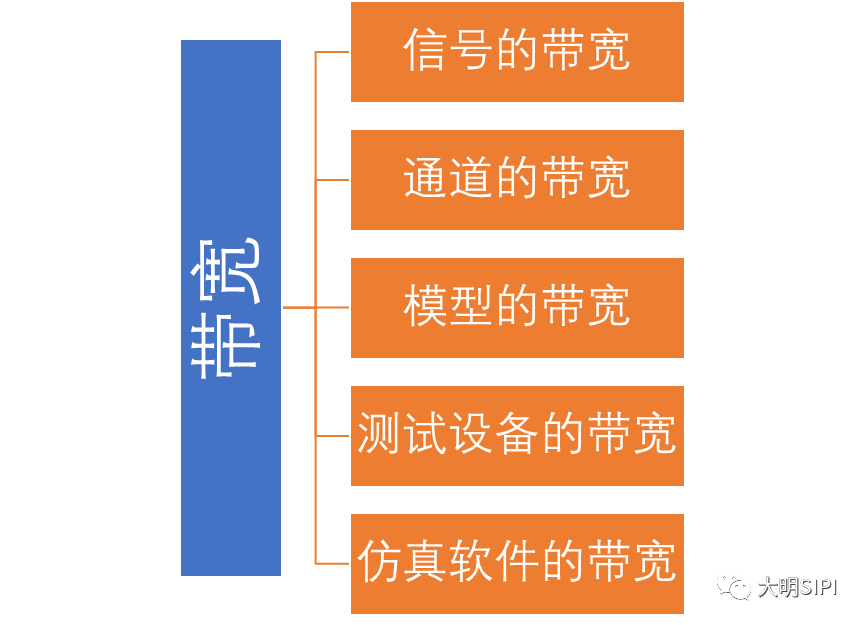

時域是真實存在的域,頻域只是一個數學構造,但頻域對我們分析解決信號完整性問題非常重要。那么如何將頻域和時域建立聯系方便的分析解決信號完整性問題?因此引出了時域和頻域之間的紐帶--帶寬。對于信號完整性分析來說,帶寬實在是太重要了,這里再嘮叨嘮叨。

2023-06-14 10:20:06 754

754

754

754

常見的信號完整性問題及解決方案

在實際的應用場景中,會遇到多種信號完整性問題,典型問題有如下幾種:反射、串擾,電源/地噪,時序等。其中,發射和串擾是引起信號完整性問題的兩大主要原因。

2022-10-09 10:56:55 2497

2497

2497

2497在PCB設計時有哪些點會導致信號完整性問題

通常說的信號完整性就是指信號無失真的進行傳輸。前面我們討論很多信號完整性問題,包括時序、串擾、衰減、反射、電源完整性、EMC等等。

2022-09-29 17:00:06 880

880

880

880高速電路的定義與信號完整性問題

在工作中經常會遇到有人問什么是高速電路,或者在設計高速電路的時候需要注意什么。每當遇到這種問題就頭腦發懵,其實不同的產品、不同的人對其都有不同的理解。今天簡單總結一下最基本的一些概念包括對高速電路的理解、什么是信號完整性還有信號的帶寬等。

2022-07-13 09:09:32 928

928

928

928信號完整性分析及在高速PCB設計中的應用

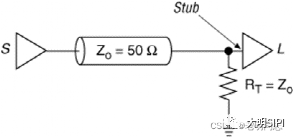

本文首先介紹了傳輸線理論,詳細分析了高速PCB設計中的信號完整性問題,包括反射、串擾、同步開關噪聲等,然后利用Mentor Graphics公司的EDA軟件HyperLynx對給定電路模型進行了反射

2022-07-01 10:53:00 3

3

3

3什么時候需要注意信號完整性問題

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

信號完整性是指高速產品設計中由互連線引起的所有問題。包括以下幾部分:

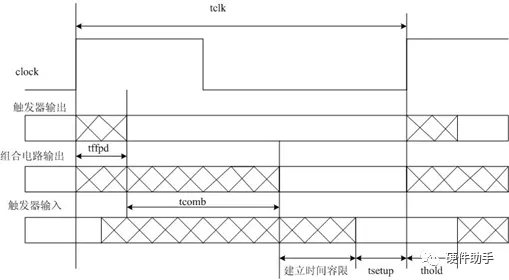

時序

噪聲

2022-02-09 16:14:50 808

808

808

808

信號完整性系列之“信號完整性簡介”

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

信號完整性是指高速產品設計中由互連線引起的所有問題。包括以下幾部分:

時序

噪聲

電磁干擾(EMI

2021-01-26 09:28:30 12

12

12

12什么因素導致信號完整性問題?

在這里,我們將討論潛在的信號完整性問題,它們的來源,理解它們的重要性,以及我們如何分析和解決這些問題。關于電氣設計,信號完整性應該集中在兩個主要方面:定時和信號質量。

2020-09-26 09:22:36 6811

6811

6811

6811什么時候需要注意信號完整性問題?

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題? 信號完整性是指高速產品設計中由互連線引起的所有問題。包括以下幾部分: 時序 噪聲 電磁干擾(EMI) 數據采樣

2020-09-18 11:01:48 4191

4191

4191

4191如何克服高速PCB設計中信號完整性問題?

PCB基板:PCB構造期間使用的基板材料會導致信號完整性問題。每個PCB基板具有不同的相對介電常數(εr )值。它決定了將信號走線視為傳輸線的長度,當然,在這種情況下,設計人員需要注意信號完整性威脅。

2020-09-17 15:48:23 2335

2335

2335

2335識別和修復pcb信號完整性問題

在PCB信號完整性問題可以很容易地定位和固定使用HyperLynx?。出口你的設計從PCB布局之后,可以以批處理方式運行模擬和/或交互模式發現信號完整性問題。內置的終結者向導可以分析一個拓撲和建議

2019-10-12 07:08:00 2427

2427

2427

2427基于信號完整性的高速PCB設計流程解析

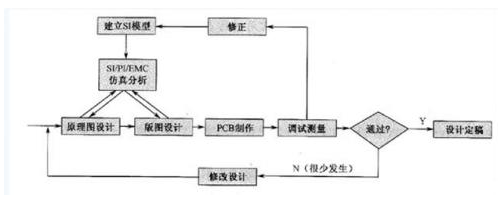

(1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立或獲取高速數字信號傳輸系統各個環節的信號完整性模型。

(2)在設計原理圖過程中,利用信號完整性模型對關鍵網絡進行信號完整性預分析,依據分析結果來選擇合適的元器件參數和電路拓撲結構等。

2019-10-11 14:52:33 1946

1946

1946

1946

信號完整性問題的有效解決方法

今天的設計技術,可以導致嚴重的信號完整性問題如果處理不當。墊,您可以運行pre-layout分析來確定高速約束、層分層盤旋飛行,和終止策略。驗證結果與布線后如果分析以確保設計滿足你所有的高需求,再被發送出去制造業。

2019-10-11 07:03:00 4374

4374

4374

4374高速pcb設計的信號完整性問題

在髙速PCB電路原理全過程中,常常會碰到信號完整性難題,造成數據信號傳送品質不佳乃至錯誤。那麼怎樣區別髙速數據信號和一般數據信號呢?許多人感覺數據信號頻率高的就是說髙速數據信號,其實要不然。

2019-10-03 16:54:00 2139

2139

2139

2139

如何在高速電路設計中完善信號的完整性詳細方法說明

在高速PCB電路設計過程中,經常會遇到信號完整性問題,導致信號傳輸質量不佳甚至出錯。那么如何區分高速信號和普通信號呢?很多人覺得信號頻率高的就是高速信號,實則不然。我們知道任何信號都可以由正弦信號的N次諧波來表示,而信號的最高頻率或者信號帶寬才是衡量信號是否是高速信號的標準。

2019-08-17 11:37:21 3226

3226

3226

3226

高速PCB設計的信號完整性問題分析

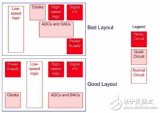

當信號在高速PCB板上沿傳輸線傳輸時可能會産生信號完整性問題。布線拓撲對信號完整性的影響,主要反映在各個節點上信號到達時刻不一致,反射信號同樣到達某節點的時刻不一致,所以造成信號質量惡化。一般來講,星型拓撲結構,可以通過控制同樣長的幾個分支,使信號傳輸和反射時延一致,達到比較好的信號質量。

2019-06-18 15:09:36 571

571

571

571基于信號完整性的高速PCB設計

借助功能強大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對高速信號進行信號完整性仿真分析是一種高效可行的分析方法,可以發現信號完整性問題,根據仿真結果在信號完整性相關問題上做出優化的設計,從而達到提高設計質量,縮短設計周期的目的。

2019-05-20 15:25:37 1011

1011

1011

1011

布線前仿真解決設計中存在的信號完整性問題

當前要創建高難度的電子產品,需要采取戰略性的方法來解決信號和電源完整性問題。在 Layout 開始之前提前研究敏感信號中存在的信號完整性問題,有助于實施布線策略、端接方法和疊層選擇,并最終減少測試工作量、降低電路板設計遍數、并縮短設計時間。

2019-05-20 06:20:00 2366

2366

2366

2366

使用HyperLynx修復和解決信號完整性問題

使用 HyperLynx? 可以輕松地查找并修復 PCB 上的信號完整性問題。從 PCB Layout 導出設計后,您可以采用批量模式和/或交互模式運行仿真,以查找信號完整性問題。內置的端接器向導

2019-05-16 06:22:00 3647

3647

3647

3647

如何確保PADS設計信號的完整性

當今設計中采用的一些技術,如果處理不當,可能會導致嚴重的信號完整性問題。借助 PADS ES Suite,您可以通過運行布線前分析來確定高速約束、疊層和端接策略。也可以使用布線后信號完整性分析來驗證結果,以確保設計在發送制造之前,符合您的所有高速要求。

2019-05-14 06:25:00 2708

2708

2708

2708高速PCB電路設計中信號完整性問題的快速定位

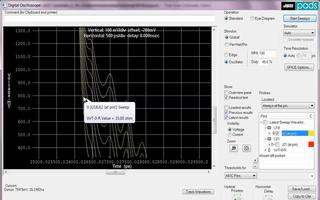

在高速電路設計中,定位信號完整性問題的傳統方法是采用硬件觸發來隔離事件,和/或利用深度采集存儲技術捕獲事件,然后再尋找問題。隨著高性能電路系統的速度和復雜程度的不斷提高,用示波器定位信號完整性問題的局限性也在逐步凸顯。

2019-01-01 11:26:00 577

577

577

577基于PCB信號完整性的反射設計

高速數字系統中,對于頻率達到百兆甚至CHz以上的信號,會由于系統的信號完整性的問題而導致信號質量不佳。甚至對于不到50 MHz的信號,由于其電平跳變時間在Ins甚至ps級,最終PCB產品中依然有可能會m現信號完整性問題。 為了縮短開

2017-11-09 16:24:32 13

13

13

13高速PCB電路板的信號完整性設計

描述了高速PCB電路板信號完整性設計方法。 介紹了信號完整性基本理論, 重點討論了如何采用高速PCB設計方法保證高速數采模塊的信號完整性

2017-11-08 16:55:13 10

10

10

10信號完整性分析

本書全面論述了信號完整性問題。主要講述了信號完整性和物理設計概論,帶寬、電感和特性阻抗的實質含義,電阻、電容、電感和阻抗的相關分析,解決信號完整性問題的四個實用技術手段,物理互連設計對信號完整性

2015-11-10 17:36:24 77

77

77

77高速電路信號完整性分析與設計—高速信號完整性的基本理論

2.1 基本電磁理論 本書主要討論高速數字電路中信號完整性分析與高速電路設計的基本方法,而信號完整性分析是以電磁場理論作為基本理論,因此必須首先討論高速信號完整性所涉及

2012-05-25 16:21:42 1536

1536

1536

1536PCB布線知識面試題_PCB工程師必備

本內容匯總了近30個PCB布線知識面試題是PCB工程師必備的知識點總結,也是面試者需要的知識。如何處理實際布線中的一些理論沖突的問題,在高速設計中,如何解決信號的完整性問題

2011-11-24 10:00:51 836

836

836

836數字電路設計的信號完整性問題探討

文章介紹了數字電路設計中的信號完整性問題, 探討了振鈴、邊沿畸變、反射、地彈、串擾和抖動等各種信號完整性問題的成因和抑制措施。針對常見的反射和串擾給出了較為詳細的分

2011-09-07 16:14:58 104

104

104

104高速并行總線信號完整性測試技術

高速并行總線信號完整性測試技術張楷 泰克科技(中國)有限公司摘要:隨著信號速度的顯著提高,信號完整性問題已經成為高速數字設計中的關鍵。本文介紹了一種新的信

2009-12-17 14:38:21 23

23

23

23高速并行總線信號完整性測試技術

高速并行總線信號完整性測試技術:隨著信號速度的顯著提高,信號完整性問題已經成為高速數字設計中的關鍵。本文介紹了一種新的信號完整性分析技術,通過集成邏輯分析儀和

2009-10-17 17:11:55 44

44

44

44在高速電路設計中信號完整性分析

由于系統時鐘頻率和上升時間的增長,信號完整性設計變得越來越重要。不幸的是,絕大多數數字電路設計者并沒意識到信號完整性問題的重要性,或者是直到設計的最后階段才

2009-09-18 09:28:46 43

43

43

43高速DSP 數據采集的信號完整性問題

深入研究高速數字電路設計中的信號完整性問題;分析電路中破壞信號完整性的原因;結合一個實際的DSP 數據采集系統, 闡述實現信號完整性的具體方法。

2009-05-18 13:24:58 17

17

17

17高速DSP 數據采集的信號完整性問題

深入研究高速數字電路設計中的信號完整性問題;分析電路中破壞信號完整性的原因;結合一個實際的DSP 數據采集系統, 闡述實現信號完整性的具體方法。

2009-04-15 09:08:03 16

16

16

16如何實現高速時鐘信號的差分布線

如何實現高速時鐘信號的差分布線

在高速設計中,如何解決信號的完整性問題?差分布線方式是如何實現的?對于只有一個輸出端的時鐘信號線,如何實現差分布線?

2009-04-15 00:26:37 2963

2963

2963

2963PCB Layout and SI設計問答集錦

PCB Layout and SI設計問答集錦

1.如何實現高速時鐘信號的差分布線? 在高速設計中,如何解決信號的完整性問題?差分布線方式是如何實現的?對于只

2009-04-15 00:23:38 1240

1240

1240

1240高速電路的信號完整性分析

摘要! 介紹了高速+,& 設計中的信號完整性概念以及破壞信號完整性的原因!從理論和計算的層面上分析了高速電路設計中反射和串擾的形成原因!并介紹了-&-. 仿真"關鍵詞!

2008-10-15 08:15:02 59

59

59

59 電子發燒友App

電子發燒友App

評論