使用CMOS集成電路需注意的幾個問題(王玲)

集成電路按晶體管的性質分為TTL和CMOS兩大類,TTL以速度見長,CMOS以功

耗低而著稱,其中CMOS電路以其優良的特性成為目前應用最廣泛的集成電路。在電子制

作中使用CMOS集成電路時,除了認真閱讀產品說明或有關資料,了解其引腳分布及極限

參數外,還應注意以下幾個問題:

1、電源問題

(1) CMOS集成電路的工作電壓一般在3-18V,但當應用電路中有門電路的模擬

應用(如脈沖振蕩、線性放大)時,最低電壓則不應低于4.5V。由于CMOS集成電路

工作電壓寬,故使用不穩壓的電源電路CMOS集成電路也可以正常工作,但是工作在不同

電源電壓的器件,其輸出阻抗、工作速度和功耗是不相同的,在使用中一定要注意。

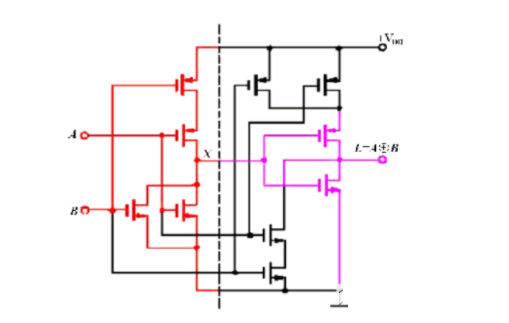

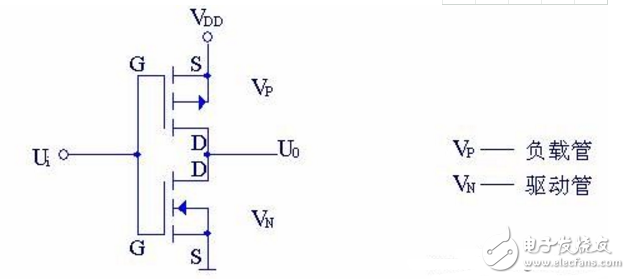

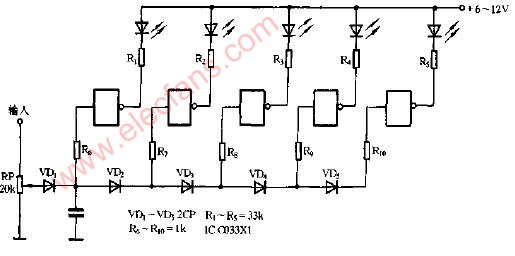

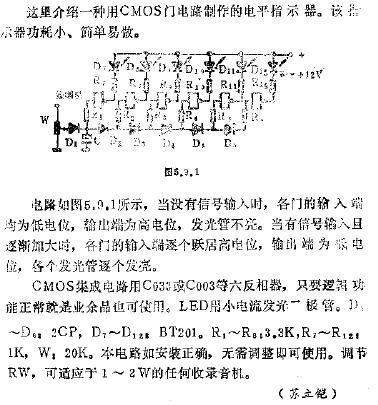

(2)CMOS集成電路的電源電壓必須在規定范圍內,不能超壓,也不能反接。因為在制

造過程中,自然形成許多寄生二極管,如圖1所示為反相器電路,在正常電壓下,這些二極

管皆處于反偏,對邏輯功能無影響,但是由于這些寄生二極管的存在,一旦電源電壓過高或

電壓極性接反,就會使電路產生損壞。

2、驅動能力問題

CMOS電路的驅動能力的提高,除選用驅動能力較強的緩沖器來完成之外,還可將同一個

芯片幾個同類電路并聯起來提高,這時驅動能力提高到N倍(N為并聯門的數量)。如圖2

所示。

3、輸入端的問題

(1)多余輸入端的處理。CMOS電路的輸入端不允許懸空,因為懸空會使電位不定,破

壞正常的邏輯關系。另外,懸空時輸入阻抗高,易受外界噪聲干擾,使電路產生誤動作,而

且也極易造成柵極感應靜電而擊穿。所以“與”門,“與非”門的多余輸入端要接高電平,

“或”門和“或非”門的多余輸入端要接低電平。若電路的工作速度不高,功耗也不需特別

考慮時,則可以將多余輸入端與使用端并聯。

(2)輸入端接長導線時的保護。在應用中有時輸入端需要接長的導線,而長輸入線必然有

較大的分布電容和分布電感,易形成LC振蕩,特別當輸入端一旦發生負電壓,極易破壞C

MOS中的保護二極管。其保護辦法為在輸入端處接一個電阻,如圖3所示, R=VDD

/1mA。

(3)輸入端的靜電防護。雖然各種CMOS輸入端有抗靜電的保護措施,但仍需小心對

待,在存儲和運輸中最好用金屬容器或者導電材料包裝,不要放在易產生靜電高壓的化工材

料或化纖織物中。組裝、調試時,工具、儀表、工作臺等均應良好接地。要防止操作人員的

靜電干擾造成的損壞,如不宜穿尼龍、化纖衣服,手或工具在接觸集成塊前最好先接一下

地。對器件引線矯直彎曲或人工焊接時,使用的設備必須良好接地。

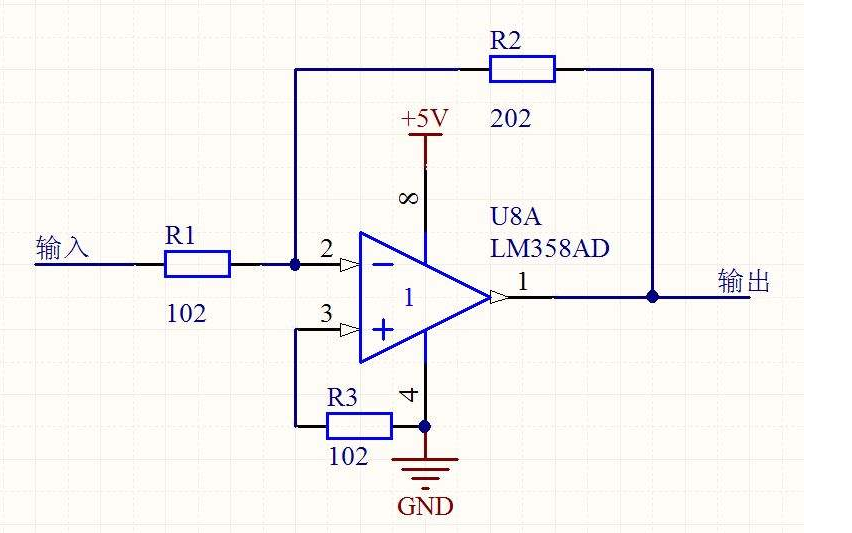

(4) 輸入信號的上升和下降時間不易過長,否則一方面容易造成虛假觸發而導致器件失

去正常功能,另一方面還會造成大的損耗。對于74HC系列限于0.5us以內。若不滿

足此要求,需用施密特觸發器件進行輸入整形,整形電路如圖4所示。

(5)CMOS電路具有很高的輸入阻抗,致使器件易受外界干擾、沖擊和靜電擊穿,所以

為了保護CMOS管的氧化層不被擊穿,一般在其內部輸入端接有二極管保護電路,如圖5

所示。

其中R約為1.5-2.5KΩ。輸入保護網絡的引入使器件的輸入阻抗有一定下降,但仍

在108Ω以上。這樣也給電路的應用帶來了一些限制:

(A)輸入電路的過流保護。CMOS電路輸入端的保護二極管,其導通時電流容限一般為

1mA?在可能出現過大瞬態輸入電流(超過10mA)時,應串接輸入保護電阻。例如,

當輸入端接的信號,其內阻很小、或引線很長、或輸入電容較大時,在接通和關斷電源時,

就容易產生較大的瞬態輸入電流,這時必須接輸入保護電阻,若VDD=10V,則取限流

電阻為10KΩ即可。

(B) 輸入信號必須在VDD到VSS之間,以防二極管因正向偏置電流過大而燒壞。因

此在工作或測試時,必須按照先接通電源后加入信號,先撤除信號后關電源的順序進行操

作。在安裝,改變連接,拔插時,必須切斷電源,以防元件受到極大的感應或沖擊而損壞。

(C)由于保護電路吸收的瞬間能量有限,太大的瞬間信號和過高的靜電電壓將使保護電路

失去作用。所以焊接時電烙鐵必須可靠接地,以防漏電擊穿器件輸入端,一般使用時,可斷

電后利用電烙鐵的余熱進行焊接,并先焊其接地管腳。

(D)要防止用大電阻串入VDD或VSS端,以免在電路開關期間由于電阻上的壓降引起

保護二極管瞬時導通而損壞器件。

4、CMOS的接口電路問題

(1)CMOS電路與運放連接。當和運放連接時,若運放采用雙電源,CMOS采用的是

獨立的另一組電源,即采用如圖6所示電路,電路中,VD1、VD2為鉗位保護二極管,

使CMOS輸入電壓處在10V與地之間。15KΩ的電阻既作為CMOS的限流電阻,又

對二極管進行限流保護。若運放使用單電源,且與CMOS使用的電源一樣,則可直接相

連。

(2)CMOS與TTL等其它電路的連接。在電路中常遇到TTL電路和CMOS電路混

合使用的情況,由于這些電路相互之間的電源電壓和輸入、輸出電平及負載能力等參數不

同,因此他們之間的連接必須通過電平轉換或電流轉換電路,使前級器件的輸出的邏輯電平

滿足后級器件對輸入電平的要求,并不得對器件造成損壞。邏輯器件的接口電路主要應注意

電平匹配和輸出能力兩個問題,并與器件的電源電壓結合起來考慮。下面分兩種情況來說

明:

(A)TTL到CMOS的連接。用TTL電路去驅動CMOS電路時,由于CMOS電路

是電壓驅動器件,所需電流小,因此電流驅動能力不會有問題,主要是電壓驅動能力問題,

TT L電路輸出高電平的最小值為2.4V,而CMOS電路的輸入高電平一般高于3.

5V,這就使二者的邏輯電平不能兼容。為此可采用圖7所示電路,在TTL的輸出端與電

源之間接一個電阻R(上拉電阻)可將TTL的電平提高到3.5V以上。

若采用的是OC門驅動,則可采用如圖8所示電路。其中R為其外接電阻。R的取值一般在

1-4.7KΩ。

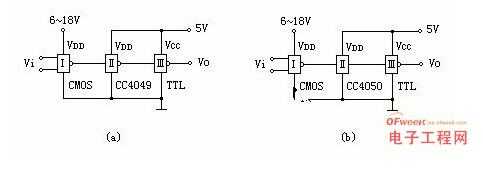

(B) CMOS到TTL的連接。CMOS電路輸出邏輯電平與TTL電路的輸入電平可

以兼容,但CMOS電路的驅動電流較小,不能夠直接驅動TTL電路。為此可采用CMO

S/TTL專用接口電路,如CMOS緩沖器CC4049等,經緩沖器之后的高電平輸出

電流能滿足TTL電路的要求,低電平輸出電流可達4mA。實現CMOS電路與TTL電

路的連接,如圖9所示。 需說明的時,CMOS與TTL電路的接口電路形式多種多樣,

實用中應根據具體情況進行選擇。

5、輸出端的保護問題

(1)MOS器件輸出端既不允許和電源短接,也不允許和地短接,否則輸出級的MOS管

就會因過流而損壞。

(2)在CMOS電路中除了三端輸出器件外,不允許兩個器件輸出端并接,因為不同的器

件參數不一致,有可能導致NMOS和PMOS器件同時導通,形成大電流。但為了增加電

路的驅動能力,允許把同一芯片上的同類電路并聯使用。

(3)當CMOS電路輸出端有較大的容性負載時,流過輸出管的沖擊電流較大,易造成電

路失效。為此,必須在輸出端與負載電容間串聯一限流電阻,將瞬態沖擊電流限制在10m

A以下。

電子發燒友App

電子發燒友App

評論