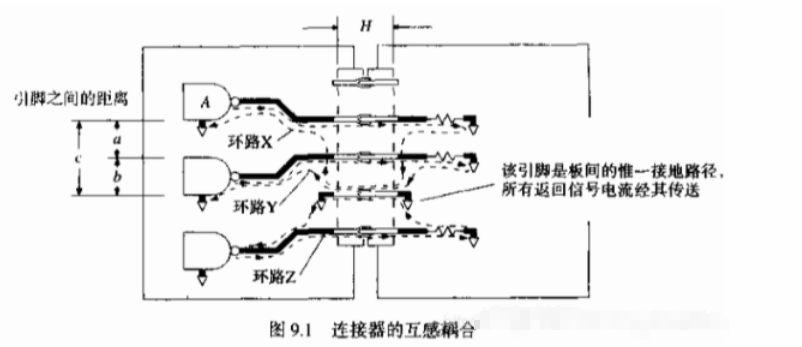

與點到點連接應用相比,在多支路總線的應用中,連接器系統的負荷要多一些。在點到點應用中,被傳送的信號只穿過連接器一次。在這種情況下,連接器的串聯電感決定了其傳輸性能。

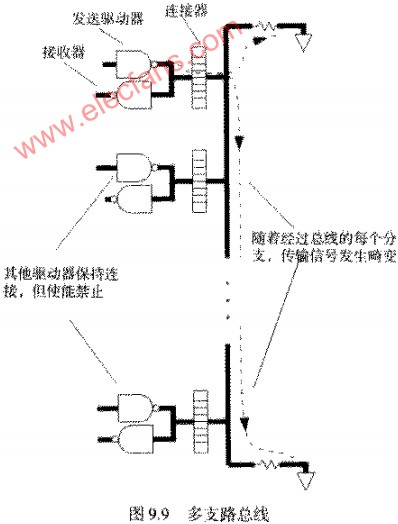

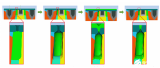

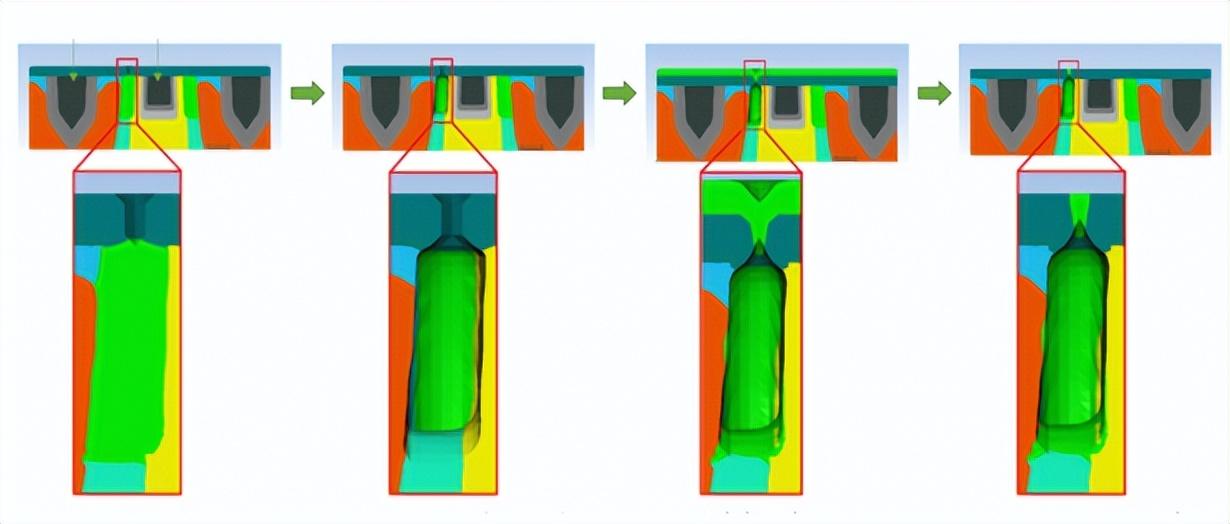

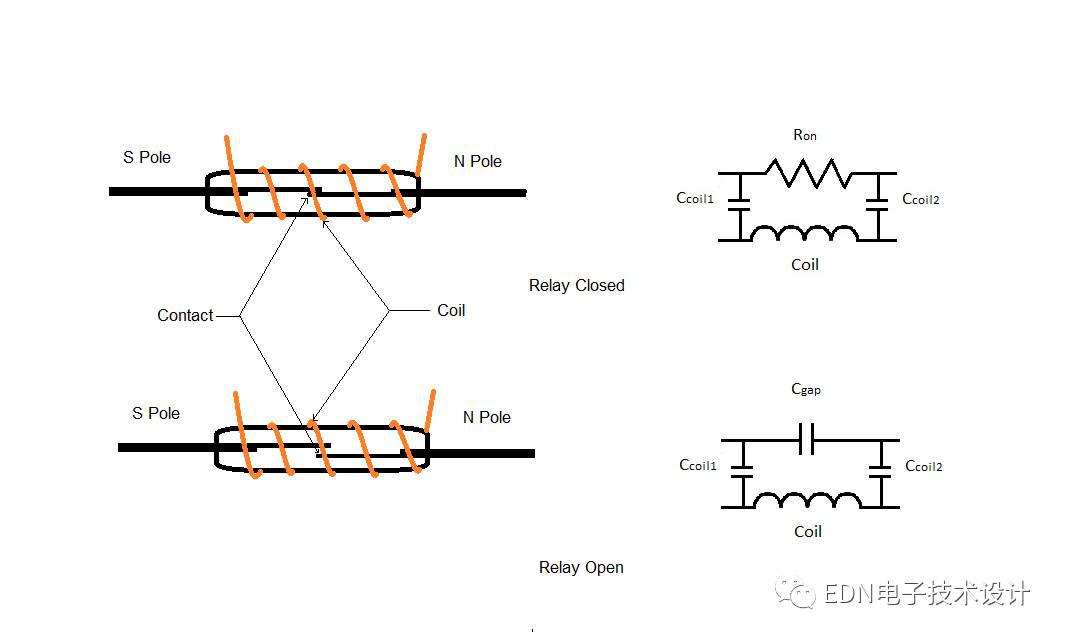

多支路情況下就有很大不同,在如圖9.9所示的多支路總線中,連接在總線上的發送器每次只有一個使能,而其他發送器則保持使能禁止,但其還是連接在總線上,直至辦輪到其發送,這種特殊類型的總線兩端都進行了端接,以防止反射,總線上傳播的信號的上升時間只是線路總長度的一小部分。

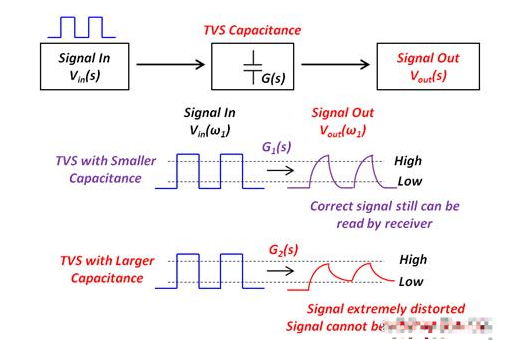

隨著經過總線的每個分支,傳輸信號逐步發生畸變,與源端連接器的串聯電感的影響相比,多個連接器寄生電容的積累導致信號畸變更嚴重。對于多支路應用,需要寄生電容非常低的連接器,即使要付出電感更大的代價。

對于調整總線操作,需要使每個總線分支處的對地集總電容最小。

每個總線分支處的集總電容包含3個部分,其中只有一個與連接器有關。

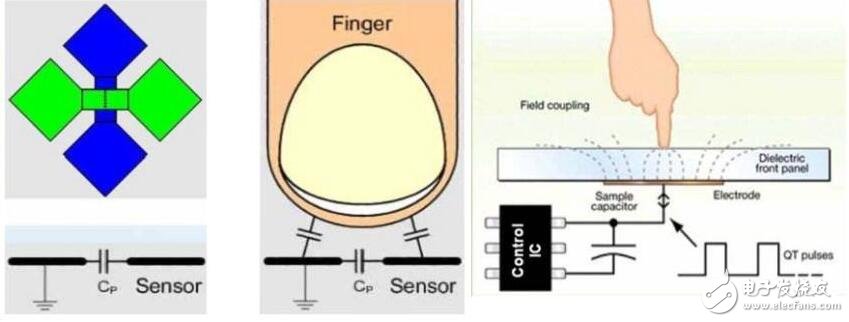

1)連接器的引腳到引腳的電容及其在印刷電路板上的焊盤電容。

2)連接本地驅動器和接收器到連接器的走線電容。

3)本地接收器的輸入電容,加上本地驅動器在使能禁止時的輸出電容。

1、引腳到引腳的電容

這一項很容易測量。將連接器安裝到板子上,留出一個信號引腳,其他所有引腳接地,用普通的電容表就可以測量信號引腳到地的電容。

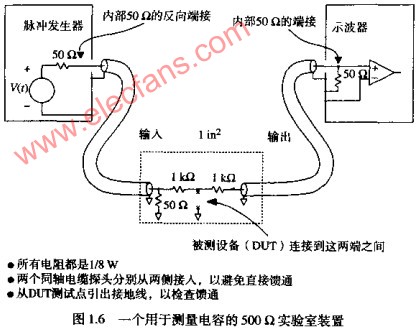

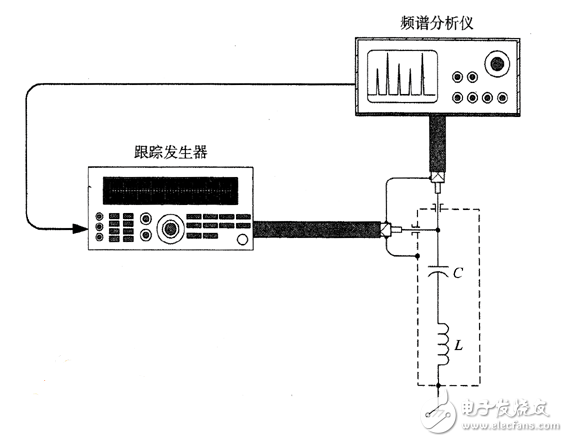

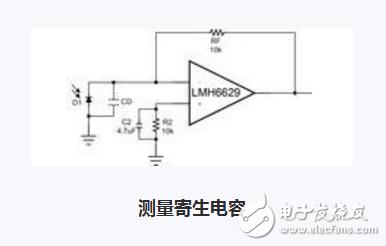

如果沒有電容表,可以使用圖1.6所示的電路來測量。

大多數的連接器的引腳間距為0.1IN,任意信號引腳到地的電容一般為幾個PF,在一個板間的連接器上,兩邊印刷電路板上的焊盤會各增加0.5PF左右。

有些連接器的引腳間距特別大,或者有其特殊的引腳熱電廠列,這都有助于減小電容,同時也為板子焊接面上的焊盤留出了更多的間距,這也正是生產技術人員所期望的。對于引腳間距為0.05IN或更小的連接器,引腳的交錯排列變得越來越重要。

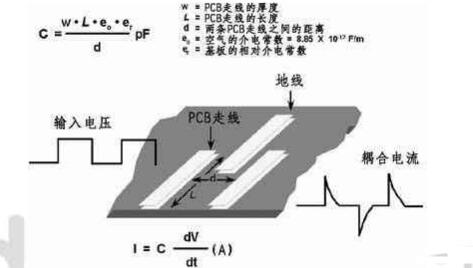

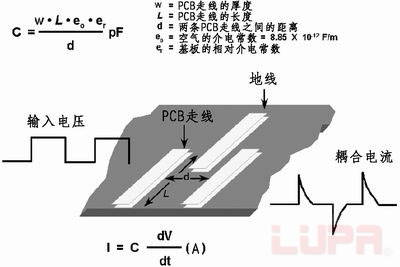

2、電路走線電容

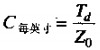

根據走線的阻抗和傳播延時,采用下式可以計算每英寸長度電路走線的電容:

其中:TD=走線傳播延時,PS/IN

????? ZO走線阻抗,Ω

????? C=電容,PF/IN

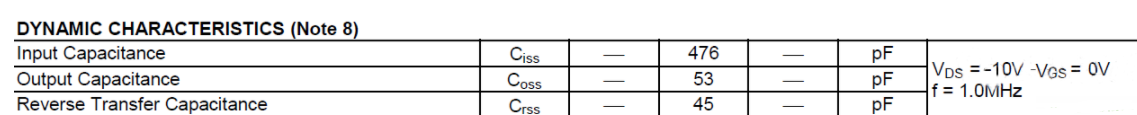

3、接收器和驅動器電容

在很多高速接收器的技術規范文檔中,生產商說明了其電容參數。但是,如果沒有技術規范文檔,可以采用圖1.6所示的電路測量其中一個樣品。測量時,調整脈沖發生器產生一個脈沖,使其電壓大小處于接收器有效范圍的中間,而且幅值和實際應用條件下的幅值相差不多。給接收器上電。一般典型的電容值為2~10PF。

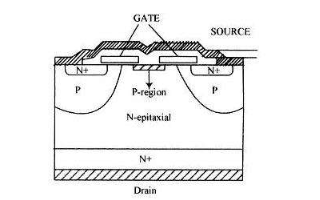

一個三態驅動器在處于關閉狀態時的電容是很大的。很多生產商不提供這個電容參數,希望用戶忽略這個因素。實際上驅動器由很大的晶體管組成,當其關閉時具有非常大的寄生電容。

只有通過測量的方法才能得到驅動器的實際電容,采用的是與接收器相同的測量方式。發送門加上電源,但其輸出使禁止,使脈沖發生器偏置在門電路的有效范圍。測量值一般不會高于80PF。

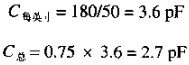

例:走線電容

一條內部走線,從連接器引出,首先進入一個驅動芯片,然后到一個接收器,總長0.75IN其電容是多少?

TD=180PD/IN(FR-4內部走線)

ZO=50Ω

4、均勻間隔負載

電容集中到一點相比,對于信號的傳播,間隔均勻地布放總線分支點,可以減小總線阻抗,降低干擾的影響。

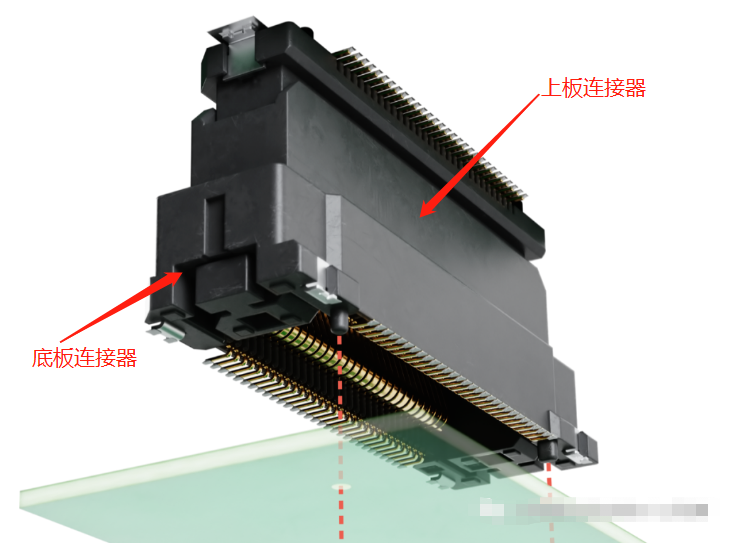

在一個插板式的機架系統中,如果插槽沿著母板卡均勻安置,并且每個板卡都插在插槽上,這時的均勻間隔模型是適用的。如果系統工作時有些插槽總是空的,均勻間隔模型將不再適用。

有一種折衷模型的假定連接器的電容在每個插槽中,但沒有插卡。只有連接器電容的作用對降低背板的阻抗、降低傳輸速度的影響是顯著的。降低背板的阻抗帶來一個好效果:當插入每塊板卡時,對整個傳輸特性的影響很小。

5、低速總線

如果不需要很高的速度,可以在多支路總線中考慮源端端接。這種情況下可以省略圖9.9中總路線兩端的電阻,通過一個串聯衰減電阻把每個三態輸出連接到總線上,接收端可以直接連到總線上。在插板式的機架應用中,這種拓撲結構的鋮點在于,在背板上不需要端接元件。

如果驅動器的上升時間比總的電氣長度長,總線作為一個集總電路元件,因此沒有反射。源端電阻給總線的集總電容充電,雖然緩慢,但卻是正常的方式。

如果驅動器的上升時間和總線的電氣長度相當,總線上會出現反射。我們可以減緩驅動器的上升時間,直到總線考慮不周為一個集總電路,從而減少反射。通過使源端電阻大于總線阻抗,就會得到RC上升時間的效果,隨著阻抗的增加,系統達到一個慢的單調的RC上升特性。連接器的電容,以及其他走線和驅動端或接收端電容,都通過源端電阻緩慢地充電。

如果可以提供等待,總路線在每個時鐘之間穩定下來,那么就可以采用一個大的源端電阻,從而具有以下優點:

降低功耗,靜態驅動電流為零

簡單,背板上不需要端接電阻

降低EMI,減少了渡過連接器的電流

電子發燒友App

電子發燒友App

評論