設計出色的低功耗應用需要同時考慮終端應用的需求和各種可用的 μC 特性。

設計人員可能會提出以下問題:是否能夠重新充電?尺寸能夠做到多小?典型的工作時間是多少?速度必須多快?要連接哪種類型的外圍器件?這些答案將最終為確立設計標準和功率要求積累原始資料。

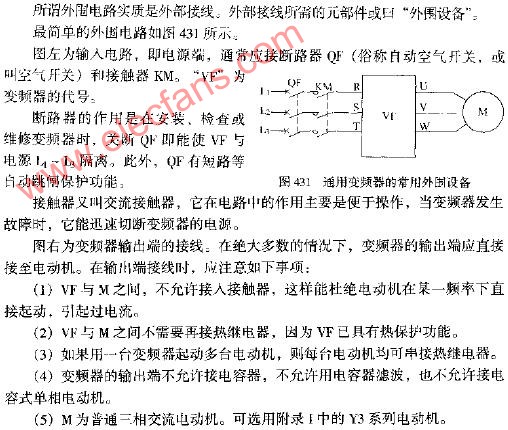

圖 1:典型 μC 環(huán)境中的器件

處理功率

首先應該考慮 CPU 的處理功率,一般來說,CPU 是功耗最高的外圍器件。處理器全速運行時,耗電量非常大,因此 CPU 處于待機或關閉狀態(tài)的時間越多,電池壽命越長。例如,4 位處理器比 32 位處理器的功率消耗低;而處于休眠或停機狀態(tài)的任何位數(shù)的處理器均比工作中的處理器的功耗要低。因此,如果 32 位處理器執(zhí)行功能所耗的時間僅為 4 位處理器的1/10,那么,它在整個系統(tǒng)生命周期內(nèi)要少消耗 9/10 的功率。因此,大多數(shù)制造商建議以較高的頻率運行 CPU,迅速完成任務,并立即返回到功耗最低的休眠狀態(tài)。總之,在選擇處理器速度時,要考慮能夠迅速處理預期工作量并盡可能長時間地處于休眠狀態(tài)。

其次應考慮大多數(shù)便攜式應用的中斷服務例程 (ISR)。ISR 會定期喚醒處理器執(zhí)行預排程序的或用戶啟動的任務,然后讓處理器返回到休眠狀態(tài)。進入和退出 ISR 所用的 CPU 時鐘周期越少越好。事實上,許多 ISR(例如端口 I/O)有多個標志,這些標志可能會觸發(fā)同一中斷。采用程序計數(shù)器相對尋址方式的處理器會大大縮短識別和處理適當中斷源所需的必要周期-尤其是在鍵盤掃描應用中。如果 ISR 編寫得好,通過限制喚醒 CPU、執(zhí)行任務和返回休眠狀態(tài)所需的程序分支,可以確保處理時間最短。采用中斷向量表的處理器中,程序計數(shù)器加載 ISR 地址,這種處理器有助于減少額外的程序分支,并降低功耗。自動上下文保存以及算術(shù)邏輯單元 (ALU) 標志和功率模式的恢復功能也可以促進節(jié)能。

此外,由于在低速或時鐘停止的環(huán)境中,動態(tài)內(nèi)核處理器不能保持數(shù)據(jù)的完整性,因而應盡可能使用靜態(tài)內(nèi)核處理器。

工作模式

休眠和“低功耗”模式也是必須考慮的重要問題。通過減慢喚醒時間實現(xiàn)低功耗狀態(tài)(或關閉對喚醒器件非常重要的功能)會增加功耗,而不是降低功耗。

大多數(shù)低功耗器件的休眠或空閑模式會關閉處理器和時鐘,通常流耗低于一微安。然后,需要 I/O 中斷把處理器從休眠模式喚醒。使用 32kHz 時鐘驅(qū)動定時器或實時時鐘能以更靈活的方式喚醒處理器。基于32kHz 振蕩器的功耗不像“深度睡眠”模式那樣低,但它能以幾微安的電流提供時鐘功能。由于許多便攜式應用需要實時時鐘功能,這種改進可以讓系統(tǒng)選用多種不同的外圍器件。

需要注意的一點是,如果處理器必須使用 RESET 信號從停機狀態(tài)喚醒,它必須運行所有硬件初始化程序。事實上,即使處理器SRAM 中的內(nèi)容沒有改變且仍然能夠?qū)ぶ分袛?它也將不得不重新初始化處理器外圍器件,這將消耗能量。

振蕩器

在通過復位喚醒時,由于穩(wěn)定振蕩器晶體所花費的時間不同,內(nèi)部振蕩器能比外部振蕩器多執(zhí)行將近 1,000 條指令。例如,使用外部振蕩器的100 MIP 機器啟動、穩(wěn)定和處理指令需要的時間為1 毫秒。與此相比,同一臺機器僅需要1 微秒時間就可以使內(nèi)部振蕩器全速工作。讓外部振蕩器穩(wěn)定的時間里,內(nèi)部振蕩器可以完成加電,執(zhí)行 1000 條指令,然后恢復斷電狀態(tài)。這一時間通常已足夠找到中斷地址,并恢復斷電狀態(tài)。那么,為什么要考慮使用外部振蕩器呢?外部振蕩器通常在整個工作溫度范圍內(nèi)更準確。事實上,在低功耗應用中,嵌入式程序裝置經(jīng)常習慣對照外部振蕩器校準內(nèi)部振蕩器。這是因為驅(qū)動外部振蕩器并使其達到速度所需的電路比內(nèi)部振蕩器消耗的功率更大。

選擇內(nèi)部振蕩器時應慎重。雖然某些內(nèi)部振蕩器可以在數(shù)微秒內(nèi)喚醒處理器,但是,必須在經(jīng)過數(shù)毫秒,當外部晶體達到穩(wěn)定之后, 才能以更高的速度運行,然后 CPU 時鐘才能切換到更高的頻率。例如,如果一個 100 MIP 的處理器有一個 20kHz 的內(nèi)部時鐘,該時鐘與外部振蕩器的 1 MHz 時鐘同時啟動,內(nèi)部振蕩器將仍然能夠執(zhí)行 999 條指令,而更高速度的處理器用同樣的時間只能執(zhí)行 20 條指令。

利用好定時器有助于在處理器保持待機狀態(tài)的情況下實現(xiàn)系統(tǒng)處理功能。由于定時器功耗非常小,因此這有助于大大降低功耗。應該使用實時時鐘模塊接受 32kHz 計時器定時器輸入和設置不同時間間隔的“警報”或中斷,在無需處理器干預的情況下,使計時器計數(shù)增加。同樣,應該使用影子寄存器更新和比較來自 ISR 的值。一旦寄存器讀到有效的預編程值,即觸發(fā) ISR,使處理器脫離休眠或待機狀態(tài),而不需要 CPU 尋找 ISR 地址、更新周期或比較值。

管理開銷

管理開銷系統(tǒng)監(jiān)視程序、監(jiān)管工作有助于防范不安全的狀況,有關器件包括電壓監(jiān)控器和看門狗定時器。由于數(shù)字電路依賴觸發(fā)器或從負到正(或相反亦然)狀態(tài)的轉(zhuǎn)換,因此,即使工作電壓有稍小的下降,也可能會意外觸發(fā) RESET 條件,從而造成系統(tǒng)無法工作。電力減弱保護作為電壓監(jiān)控的一部分,一般用于確保電壓瞬變不會強制處理器進入和退出RESET 狀態(tài)。

只要有可能,在電壓監(jiān)控解決方案中應采用不可屏蔽的中斷 (NMI) 來識別電壓瞬變。這種方法讓用戶能隨心所欲地設定電壓觸發(fā)的門限電平,無需系統(tǒng)復位條件,其功耗一般比模擬-數(shù)字轉(zhuǎn)換器 (ADC) 通道更低。

看門狗定時器監(jiān)視故障情況。雖然在典型的嵌入式應用中,內(nèi)嵌的系統(tǒng)程序器往往禁用看門狗定時器,但是在低功耗系統(tǒng)中,在電源電壓不穩(wěn)定的情況下,看門狗定時器是一種有用的工具。看門狗定時器會執(zhí)行預先設定功能,例如在符合某些條件時,比如電壓過低或有內(nèi)存問題時,向處理器發(fā)出 RESET 指令。所選擇的處理器應該能夠生成已知的 ISR,使處理器無需執(zhí)行 RESET 而恢復聯(lián)機狀態(tài);因為執(zhí)行 RESET,必須啟動外圍設備,因而會消耗更多的處理器功率。

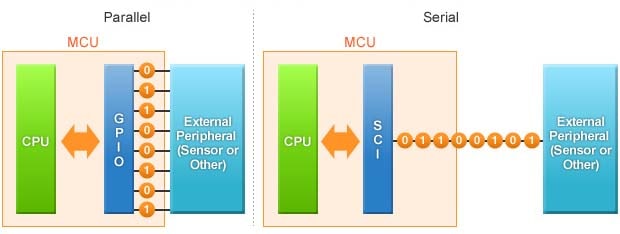

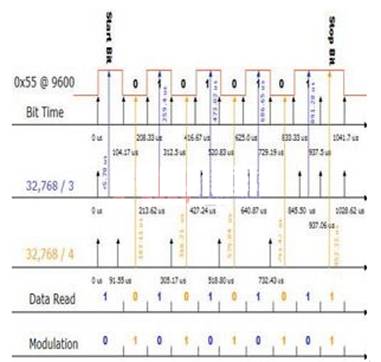

將一個數(shù)字時鐘與另一個數(shù)字時鐘精確到秒地同步是不可能的,因為每個時鐘均與其內(nèi)部晶體同步。在 MCU 驅(qū)動的系統(tǒng)中,低功耗模式下使用的 32kHz 實時時鐘晶體與用于生成UART 波特率的普通 38.4kHz 頻率之間會出現(xiàn)類似的同步問題。因為實時時鐘的 32,768 頻率使 15 位寄存器每秒溢出一次,所以非常適合時間保持(TIme-keeping) 應用。比較而言,在UART 中使用相同的頻率,則在典型的 10 位(起始位、8 位數(shù)據(jù)和 1 個奇偶校驗位)傳輸中保證至少有一位讀取不正確。這是由于 32,768Hz 時鐘必須除以 3.4,才能得到 9,600 波特率。由于沒有 3.4 這一選擇,因此必須選擇除以 3 或除以 4(參見圖2)。

將一個數(shù)字時鐘與另一個數(shù)字時鐘精確到秒地同步是不可能的,因為每個時鐘均與其內(nèi)部晶體同步。在 MCU 驅(qū)動的系統(tǒng)中,低功耗模式下使用的 32kHz 實時時鐘晶體與用于生成UART 波特率的普通 38.4kHz 頻率之間會出現(xiàn)類似的同步問題。因為實時時鐘的 32,768 頻率使 15 位寄存器每秒溢出一次,所以非常適合時間保持(time-keeping) 應用。比較而言,在UART 中使用相同的頻率,則在典型的 10 位(起始位、8 位數(shù)據(jù)和 1 個奇偶校驗位)傳輸中保證至少有一位讀取不正確。這是由于 32,768Hz 時鐘必須除以 3.4,才能得到 9,600 波特率。由于沒有 3.4 這一選擇,因此必須選擇除以 3 或除以 4(參見圖2)。

圖 2:9600 波特傳輸時 32Khz 驅(qū)動 UART Rx 錯誤

UART 數(shù)據(jù)用 10,922 波特或 8,192 波特的 UART 接收。由于 UART 在傳輸中間點對數(shù)據(jù)進行采樣以補償抖動,因此該點已經(jīng)被選擇為接收 UART 的采樣點。在沒有行抖動的理想情況下,10,922 波特 UART 對第三數(shù)據(jù)位的開始兩次讀數(shù)都會是錯誤的而8,192 波特的UART 由于會完全遺漏第三位,很快就將出錯。由于低功耗應用的理想時鐘是低功耗實時時鐘模式,這使得在低功耗環(huán)境中處理很困難。解決這一問題的最好辦法就是將 μC 與調(diào)制技術(shù)結(jié)合使用,用 32kHz 振蕩器提供非常精確的 2,400 波特,并完全能支持9,600 波特(參見圖 3)。

圖 3:在 9600 波特傳輸時采用時鐘調(diào)制的 32Khz 驅(qū)動 UART

通過混合兩個時鐘除數(shù)解決錯誤,總體積累的錯誤消失,數(shù)據(jù)接收正確。這種方法對于9,600 波特或以下的 UART 通信很有效。對于高速通信,幾個 μC 監(jiān)視 UART Rx 行的邊緣躍遷并觸發(fā) ISR 啟動內(nèi)部高速振蕩器,驅(qū)動 CPU 并處理中斷。這使 μC UART 能夠接收高速數(shù)據(jù),而不必在 UART 空閑期間保持一個啟動的高速時鐘。如果使用外部振蕩器或內(nèi)部振蕩器頻率太低,則由于啟動高速振蕩器需要一定的時間,第一次傳輸將失效。為克服這一限制和效率損失,設計人員應該考慮使用能夠喚醒并及時從 32kHz 或停機模式激活的處理器,從正在傳輸?shù)?UART 恢復首次傳輸?shù)臄?shù)據(jù)。例如,系統(tǒng)時鐘需要在 25μs 內(nèi)啟動,才能拾取起始位的中間點,從而正確接收 19,200 位的傳輸。

許多低功耗應用通過 UART 將 μC 連接到 RS-485 傳感器網(wǎng)絡。支持尋址和多處理器(9 位)模式的 UART 非常適合于這種網(wǎng)絡。當?shù)?9 位為 1(代表是一個地址)時,這些 UART 會生成一個 ISR,讓處理器能夠在其它傳感器通過系統(tǒng)發(fā)送數(shù)據(jù)時保持休眠狀態(tài)。某些 μC 會更進一步,在 UART 中加入地址匹配,僅在第 9 位是 1 且地址與在剩余 8 位中收到的數(shù)據(jù)匹配時才喚醒系統(tǒng)。

模擬器件

模擬器件模擬器件是最早的操作器件。模擬器件已經(jīng)發(fā)展數(shù)十年,它是穩(wěn)定電源、為高速晶體電路提供過濾和穩(wěn)定性的必要器件,對監(jiān)控來自自然界的輸入信號也必不可少。

模擬器件模擬器件是最早的操作器件。模擬器件已經(jīng)發(fā)展數(shù)十年,它是穩(wěn)定電源、為高速晶體電路提供過濾和穩(wěn)定性的必要器件,對監(jiān)控來自自然界的輸入信號也必不可少。

在待機模式下,模擬器件實際上不消耗功率。模擬-數(shù)字轉(zhuǎn)換器 (ADC) 斷電快,在待機模式下,甚至可以被視為一種低功耗應用。

一旦加電,缺點即暴露無遺。一般來說,模擬器件在工作時需要的電流很大。例如,ADC 工作時需要的電流達數(shù)百微安。另外,模擬器件(例如內(nèi)部基準時鐘)會使啟動時間增加幾毫秒,因為穩(wěn)定模擬器件需要相對較大的外部電容。另一種經(jīng)常被集成的器件-集成溫度傳感器-通常是隨溫度改變的二極管電路,也需要相當大的電流。

在低功耗應用中有幾個需要考慮的標準。如果 ADC 有內(nèi)部振蕩器,就沒有必要對其它系統(tǒng)振蕩器加電來進行轉(zhuǎn)換。在這種情況下,處理器保持斷電狀態(tài),只有轉(zhuǎn)換完成時起,才需要開始工作。像 CPU 一樣,我們可以通過縮短執(zhí)行時間來降低功耗。ADC 轉(zhuǎn)換的速度越快,器件進入待機模式的速度越快。對于內(nèi)部基準時鐘也是這樣。基準時鐘啟動和穩(wěn)定得越快,轉(zhuǎn)換完成和模擬系統(tǒng)斷電的速度也越快。如果只是偶爾使用 ADC,某些處理器允許采樣時鐘斷電,讓跟蹤電路保持加電。這樣 ADC 就能夠進入較淺的休眠模式。這種功能的負面影響是,在進行轉(zhuǎn)換前,需要花較長時間來讓采樣和保持電路達到穩(wěn)定。

轉(zhuǎn)換完成之后,有幾個 μC 集成了直接內(nèi)存訪問 (DMA) 或先入先出 (FIFO) 緩沖存儲器,能夠?qū)⒍鄠€轉(zhuǎn)換存儲在RAM 中,而無需喚醒處理器。在一定數(shù)量的轉(zhuǎn)換到達之前,處理器會保持待機狀態(tài),而不是在每個轉(zhuǎn)換后喚醒處理器來將數(shù)據(jù)移入 RAM,這樣就可以降低功耗。

許多低功耗 μC 內(nèi)置內(nèi)部模擬比較器,可以執(zhí)行簡單的模擬任務。有些制造商的比較器允許編程,可以通過延長響應時間降低功耗。

起始點

總之,μC 外圍設備的選擇是由終端應用最終決定的,因此我們應從全面評估系統(tǒng)功能及其功率要求著手。許多處理器制造商宣稱其器件具備低功耗工作能力,但是不同的應用對“低功耗”一詞有不同的定義。是需要大量集成的速度更高的處理器,還是需要具有極深度睡眠模式的速度更低的處理器,更多地取決于內(nèi)嵌系統(tǒng)的要求,而不是內(nèi)嵌處理器所謂的“低功耗”工作能力。

電子發(fā)燒友App

電子發(fā)燒友App

評論