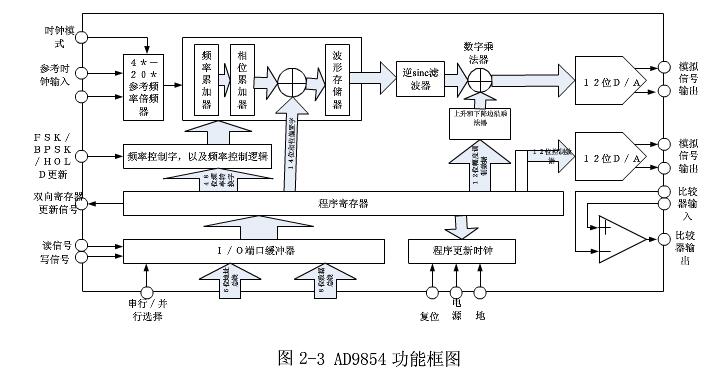

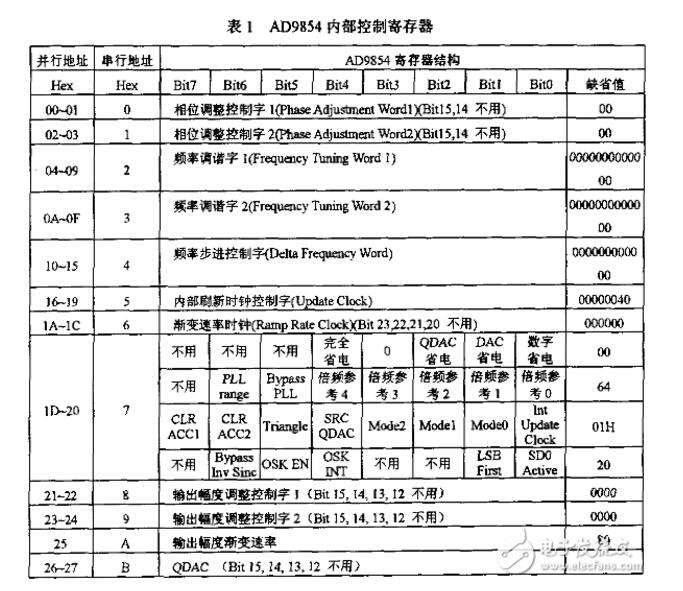

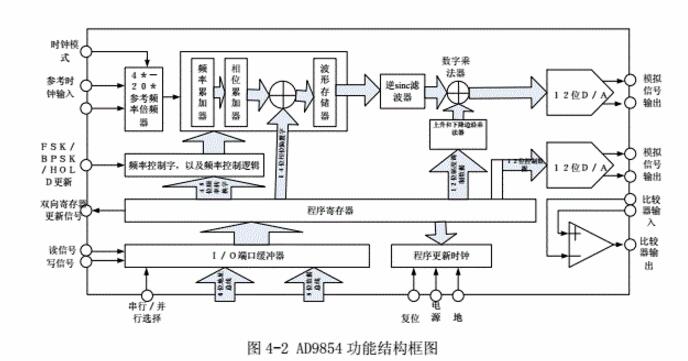

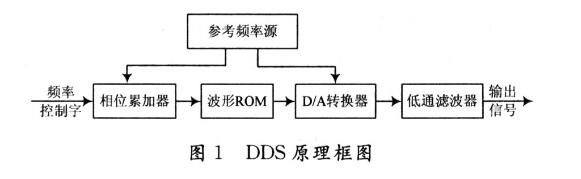

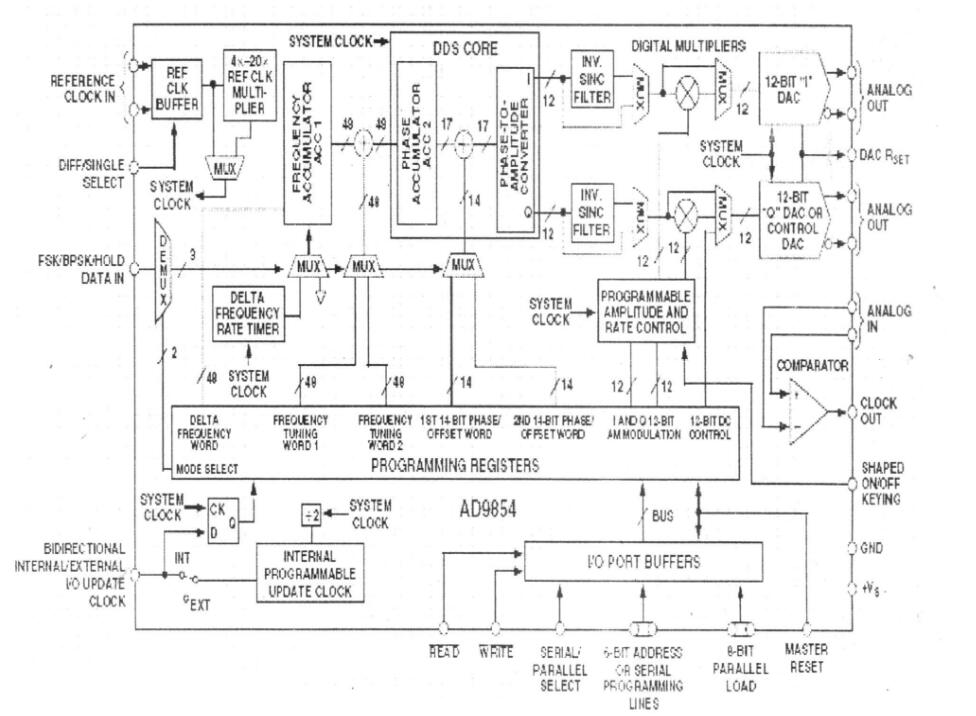

AD9854數字合成器是高集成度的器件,它采用先進的DDS技術,片內整合了兩路高速、高性能正交D/A轉換器通過數字化編程可以輸出I、Q兩路合成信號。在高穩定度時鐘的驅動下,AD9854將產生一高穩定的頻率、相位、幅度可編程的正弦和余弦信號,作為本振用于通信,雷達等方面。AD9854的DDS核具有48位的頻率分辨率(在300M系統時鐘下,頻率分辨率可達1uHZ)。輸出17位相位截斷保證了良好的無雜散動態范圍指標。AD9854允許輸出的信號頻率高達150MHZ,而數字調制輸出頻率可達100MHZ。通過內部高速比較器正弦波轉換為方波輸出,可用作方便的時鐘發生器。

AD9854數字合成器有兩個14位相位寄存器和一個用作BPSK操作的引腳。對于高階的PSK調制,可通過I/O接口改變相位控制字實現。具有改進DDS結構的12位I和Q通道D/A轉換器可以提供較大的帶寬并有較好的窄帶無雜散動態范圍(SFDR)。如果不使用Q通道的正交功能,它還可以通過配置,由用戶編程控制D/A轉換。當配置高速比較器時,12位D/A輸出的方波可以用來做時鐘發生器。它還有兩個12位數字正交可編程幅度調制器,和通斷整形鍵控功能,并有一個非常好的可控方波輸出。同時脈沖調制功能在寬帶掃頻中也有重要應用。AD9854的300M系統時鐘可以通過4X和20X可編程控制電路由較低的外部基準時鐘得到也可以通過單端或差分輸入。AD9854還有單腳輸入的常規FSK和改進的斜率FSK輸出。AD9854采用先進的0.35微米COMS工藝在3.3V單電源供電的情況下提供強大的功能。

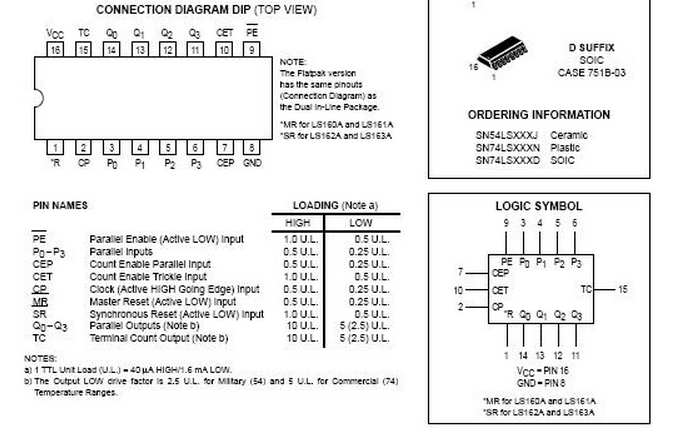

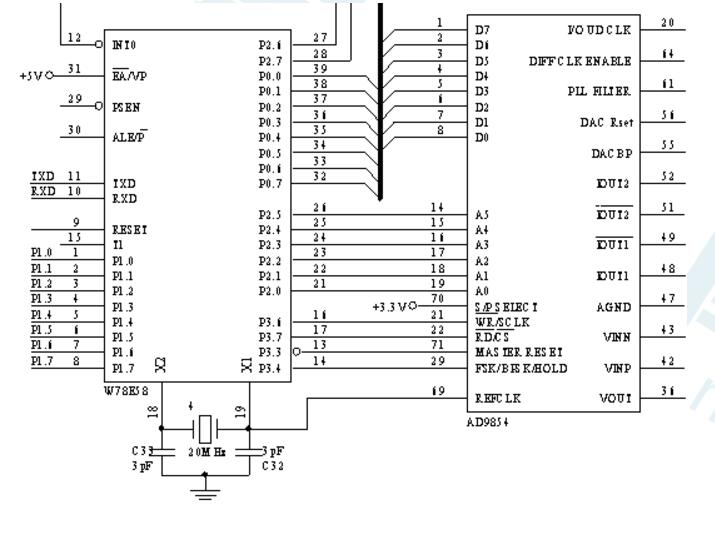

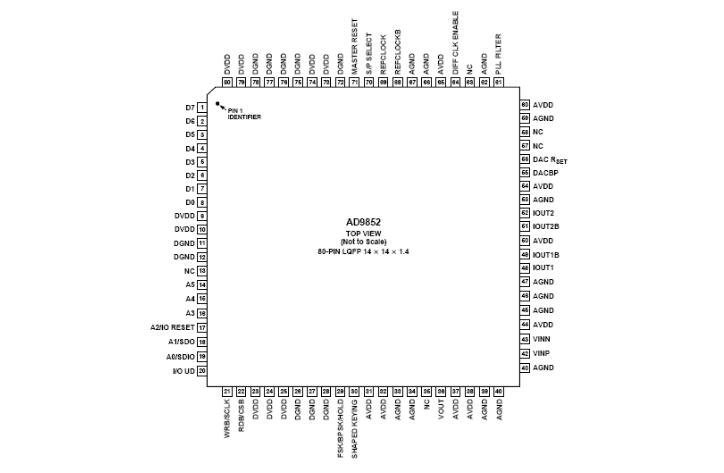

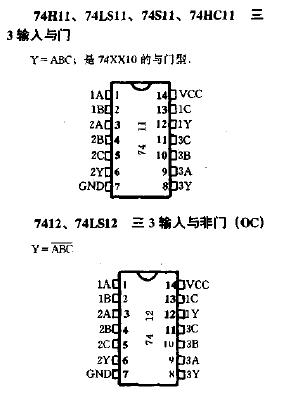

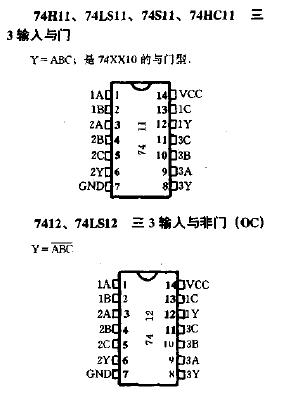

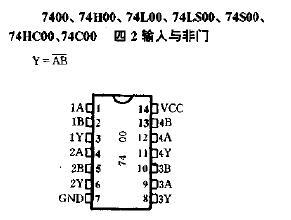

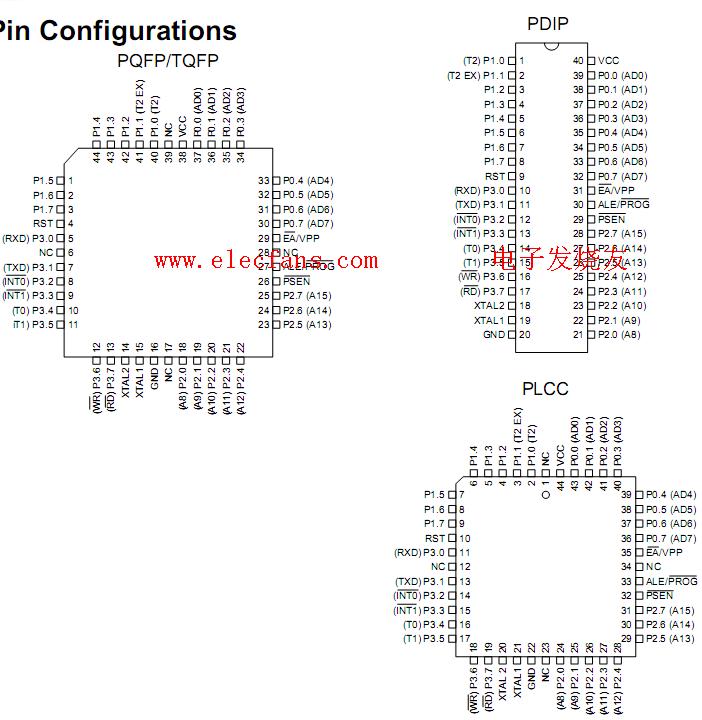

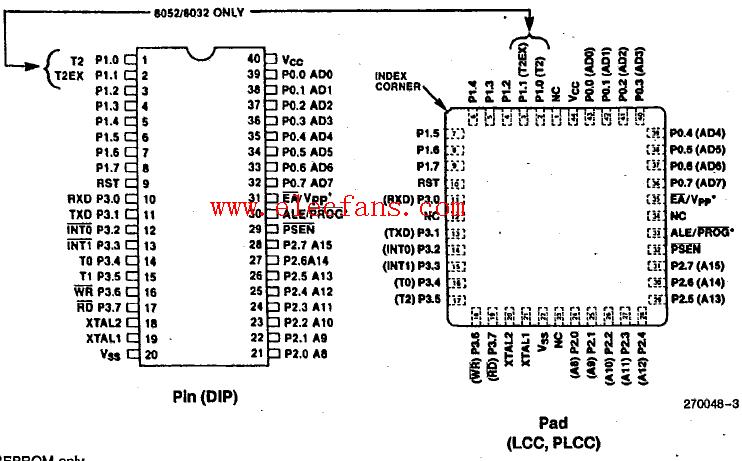

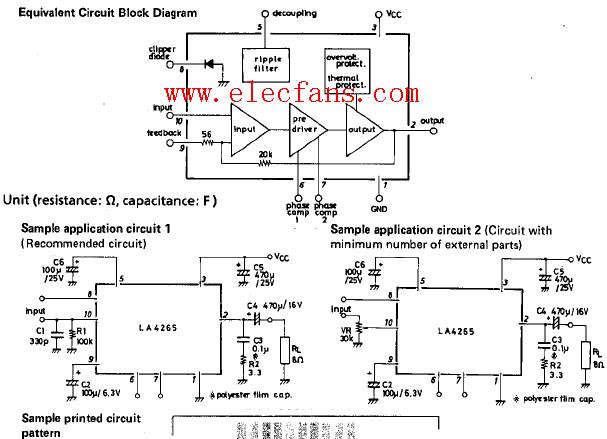

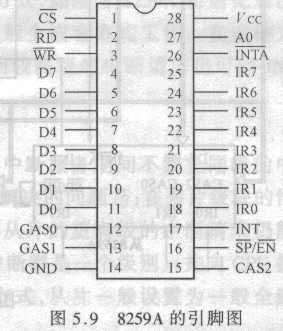

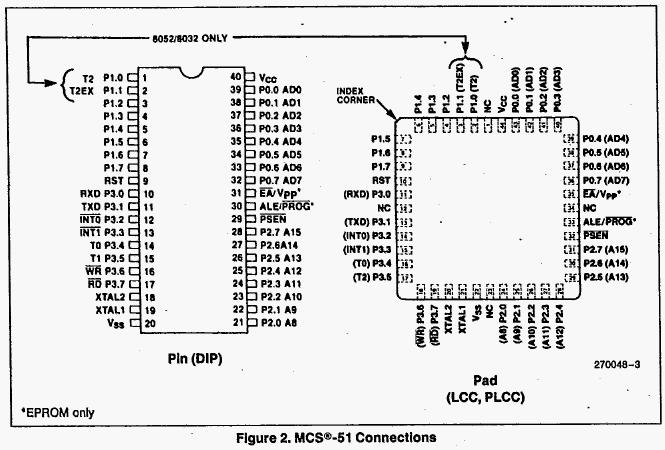

ad9854引腳圖:

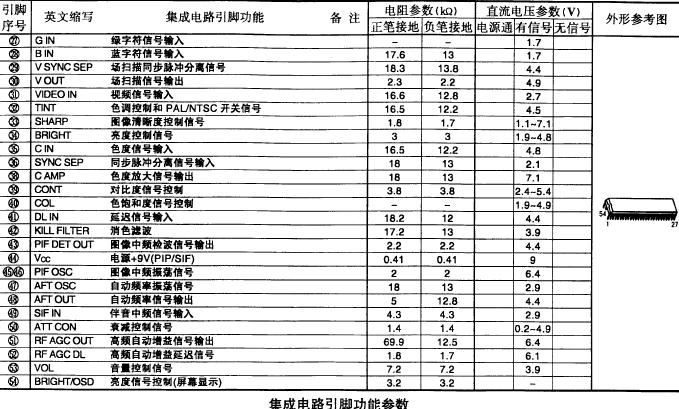

ad9854引腳功能:

? ? ?D7-D0 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?8 位雙向并行編程數據輸入。只用于并行編程模式。

? ? ?DVDD ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?連接到數字電路的供應電壓。通常為 3.3V。

? ? ?DGND ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?連接到數字電路的地。功能同 AGND。

? ? ?NC ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?無內部連接。

? ? ?A5-A0 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?編程寄存器的 6 位并行地址輸入。只用于并行編程模式。當使用串行編程模式時 A0,A1,A2 使用它們各自的另一個功能,如下介紹:

? ? ?A2/IO ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? RESET 串行通訊總線的 I/O 復位信號。由于不合適的編程協議而造成無應答就會產生此復位信號。用這種方式復位串行總線不會影響之前編好的程序,也不會喚醒 “默認”編程值。此腳工 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 作狀態為高。

? ? ?A1/SDO ? ? ? ? ? ? ? ? ? ? ? ? ?當使用 3 線串行通訊模式時的單向串行數據輸出。

? ? ?A0/SDIO ? ? ? ? ? ? ? ? ? ? ? ? ?當使用 2 線串行通訊模式時的雙向串行數據輸入/輸出。在設計中只用其并型模式。設計中將其與 MSP430F149 的 P4 口相連。

? ? ?I/O UD CLK ? ? ? ? ? ? ? ? ? ? ?雙向 I/O 刷新時鐘。用作控制寄存器選擇方向。若選擇作為輸入,則會在上升沿時把 I/O 端口緩沖器的內容傳送到程序寄存器。若作為輸出(默認),則在 8 個系統時鐘周期期間的輸出 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?脈沖(低到高)就表明一個內部頻率刷新已經發生了。

? ? ?WR/SCLK ? ? ? ? ? ? ? ? ? ? ? ?寫并行數據到 I/O 端口的緩沖器。復用功能為 SCLK,即串行程序總線的串行時鐘信號。數據在此時鐘信號的上升沿時被寄存。當使用并行模式時此引腳為WR。模式選擇是由引腳 70 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 來決定的。

? ? RD/CSB ? ? ? ? ? ? ? ? ? ? ? ? ? ?從程序寄存器讀并行數據。復用功能為 CSB,即串行程序總線的片選信號。激活狀態為低。當使用并行模式時此引腳為RD 。

? ? FSK/BPSK/HOLD ? ? ? ? ? ? 多用引腳,根據程序控制寄存器的運行模式選擇來使用。若在 FSK 模式,邏輯低選擇 F1,邏輯高選擇 F2。若在 BPSK 模式,邏輯低選擇相位 1,邏輯高選擇相位 2。 若為 Chirp 模 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?式,邏輯高表示 HOLD 功能,并使頻率計數器在其當前的位置暫停。為了恢復或者開始 Chirp 模式,應事先聲明邏輯低。

? ? ?SHAPED KEYING ? ? ? ? ? ? 此引腳首先必須被程序控制寄存器選擇好功能。邏輯高將使 I 和 Q DAC 的輸出在預編程下從 0 比例迅速到滿比例放大,邏輯低則相反。

? ? ?AVDD ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?模擬電路的電壓,通常為 3.3V。

? ? ?AGND ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?模擬電路的地,功能同 DGND。

? ? ?VOUT1 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?內部高速比較器的正相輸出引腳。設計驅動 10dBm、50 歐姆負載,以及標準 CMOS 邏輯值。

? ? ?VINP ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?電壓輸入正極。內部高速比較器的正向輸入。

? ? ?VINN ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?電壓輸入負極。內部高速比較器的反向輸入。

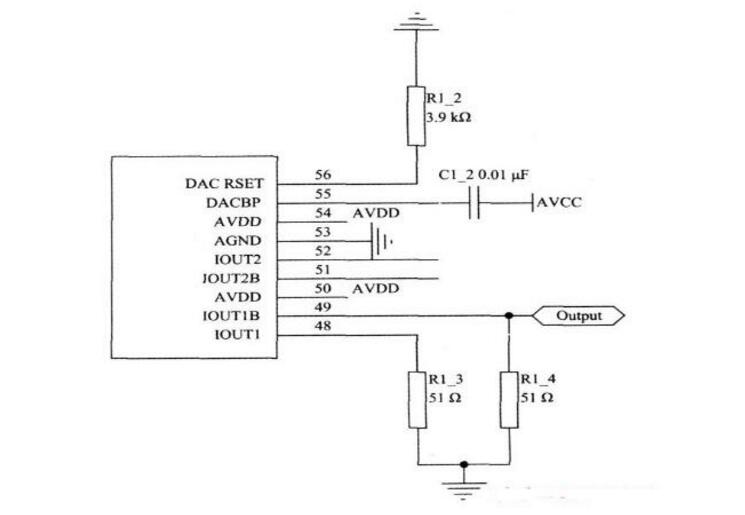

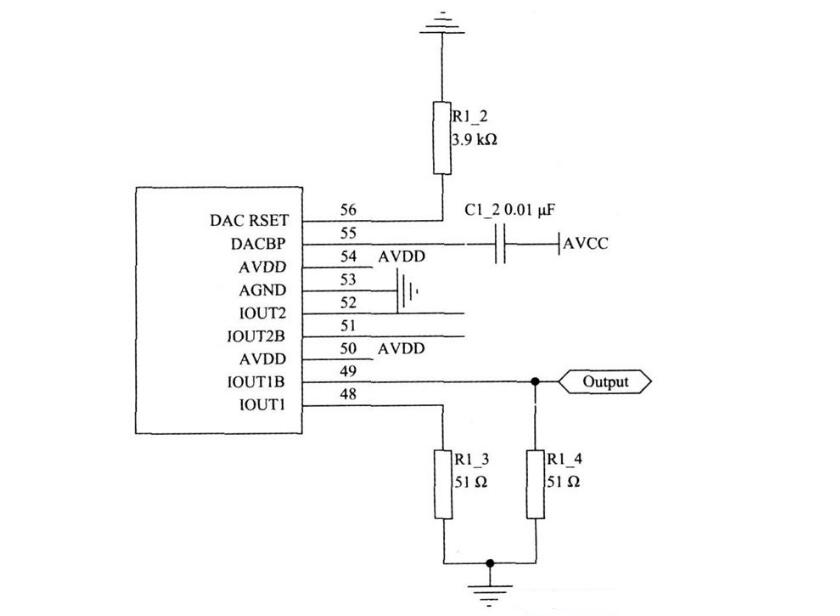

? ? ?IOUT1 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?I 或正弦 DAC 的單極電流輸出。

? ? ?IOUT1B ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?I 或正弦 DAC 的互補單極電流輸出。

? ? ?IOUT2 B ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? Q 或正弦 DAC 的互補單極電流輸出。

? ? ?IOUT2 ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? Q 或正弦 DAC 的單極電流輸出。此 DAC 可以被編程用來接收外部 12 位數據,并用此 12 位數據替代內部正弦數據。這樣 AD9854 就可以仿真 AD9852 的DAC 功能。

? ? ?DACBP ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? I 和 Q DACs 的通用旁路電容連接引腳。通常在此引腳和 AVDD 之間連接0.01UF 的電容,來改善非線性失真和 SFDR。如果不連接電容也是可以的,但是對于 SFDR 的效果要降低。

? ? ?DAC Rset ? ? ? ? ? ? ? ? ? ? ? ? ? ? I 和 Q DACs 的通用連接引腳。用來設置滿比例輸出電流。

? ? ?PLL FILTER ? ? ? ? ? ? ? ? ? ? ? ? 此引腳為 REFCLK Multiplier’s PLL 回路濾波器的外部零補償網絡提供連接。 DIFF CLK ENABLE 差分 REFCLK 使能。

? ? ?REFCLKB ? ? ? ? ? ? ? ? ? ? ? ? ? ?互補(180 度反相)差分時鐘信號。

? ? ?REFCLK ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? 單端(CMOS 邏輯電平要求)參考時鐘輸入或兩個差分時鐘中的一個信號。

? ? ?S/P SELECT ? ? ? ? ? ? ? ? ? ? ? ?串行編程模式(邏輯低)和并行編程模式(邏輯高)之間的選擇。

? ? ?MASTER RESET ? ? ? ? ? ? ? ?為用戶編程來初始化串行/并行編程總線,用表 IV 中的默認值來設置編程寄存器為“do-nothing”狀態。激活時為邏輯高。為了正確運行必須在啟動時就定義此引腳。

電子發燒友App

電子發燒友App

評論