信號完整性是指信號在傳輸路徑上的質量,由于路徑的特性對信號造成的失真。數字電路剛出現的時候,由于傳輸信號速率很低,在電路分析時采用低頻和直流的方法就可以。

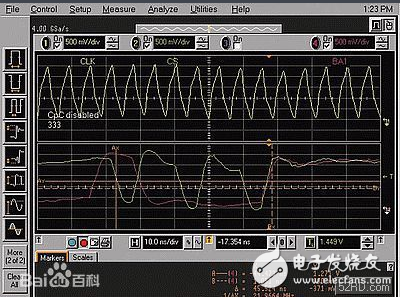

但是隨著數字信號頻率越來越高,電路的模擬特性越來越顯現出來,所以也有人說信號完整性是數字與模擬的橋梁。數字電路工程師已經需要大量的射頻和微波電路基礎理論來分析數字電路。高端的信號完整性試驗室都需要同時配備示波器和網絡分析儀。

傳輸路徑可以是普通的金屬線,可以是光學器件,也可以是其他媒質。信號具有良好的信號完整性是指當在需要的時候,具有所必需達到的電壓電平數值。差的信號完整性不是由某一單一因素導致的,而是系統設計中多種因素共同引起的。

不管是在系統中什么地方,隔離并排除信號完整性故障總是一項極具挑戰性的任務。您需要高帶寬而且省時的解決方案來正確解決高速信號偏差問題,信號完整性測試設備數字示波器、邏輯分析儀、實時頻譜分析儀、時域反射計解決方案、信號發生器、高保真探頭和分析軟件。

信號完整性分析概論

高速領域:時鐘頻率超過100MHz或者Tr小于1ns,信號完整性效應就變得重要。通常將這種情況稱之為高頻領域或高速領域。

體會:可作為經驗法則。大致判斷某塊電路是否需要進行計算或仿真。對于低于此頻率以下,Tr以上的,便可采用大致的經驗來設計。對于低頻唯一的要求就是聯通即可。高一點的要求便是美觀工整。按要求設計唄,不用考慮太多SI問題。做好PDS即可了。

信號完整性三種影響和后果:

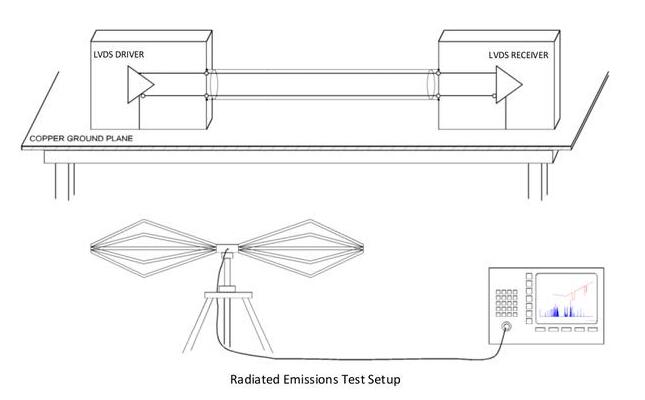

1.時序;2.噪聲;3.電磁干擾。

理解:具體產生以上問題還沒有細致研究過。待成為半神再來解釋

SI特定噪聲源:

1.單一網絡的信號完整性;在信號路徑或返回路徑上由于阻抗突變而引起的反射與失真

2.兩個或多個網絡間的串擾;和理想回路與非理想回路耦合的互容互感。

3.電源和地分配中的軌道塌陷;在電源、地網絡中的電壓變化!

4.來自整個系統的電磁干擾和輻射。

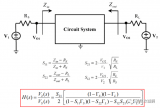

體會:單一網絡包括從源端,源內阻,傳輸線,接收端容抗,返回路徑。保持信號完整性,就需要盡可能將以上設計成相同阻抗。如果接收與發送不匹配就需要采用T型網絡或者π型網絡進行阻抗匹配。比如視頻信號采用的特殊阻抗為75歐姆,電路板采用的是50歐姆,其便可使用衰減電路來匹配特性阻抗。

任何改變橫截面或網絡幾何形狀的特性都會改變信號所受到的特性阻抗。使信號所感受到的阻抗突變如下:

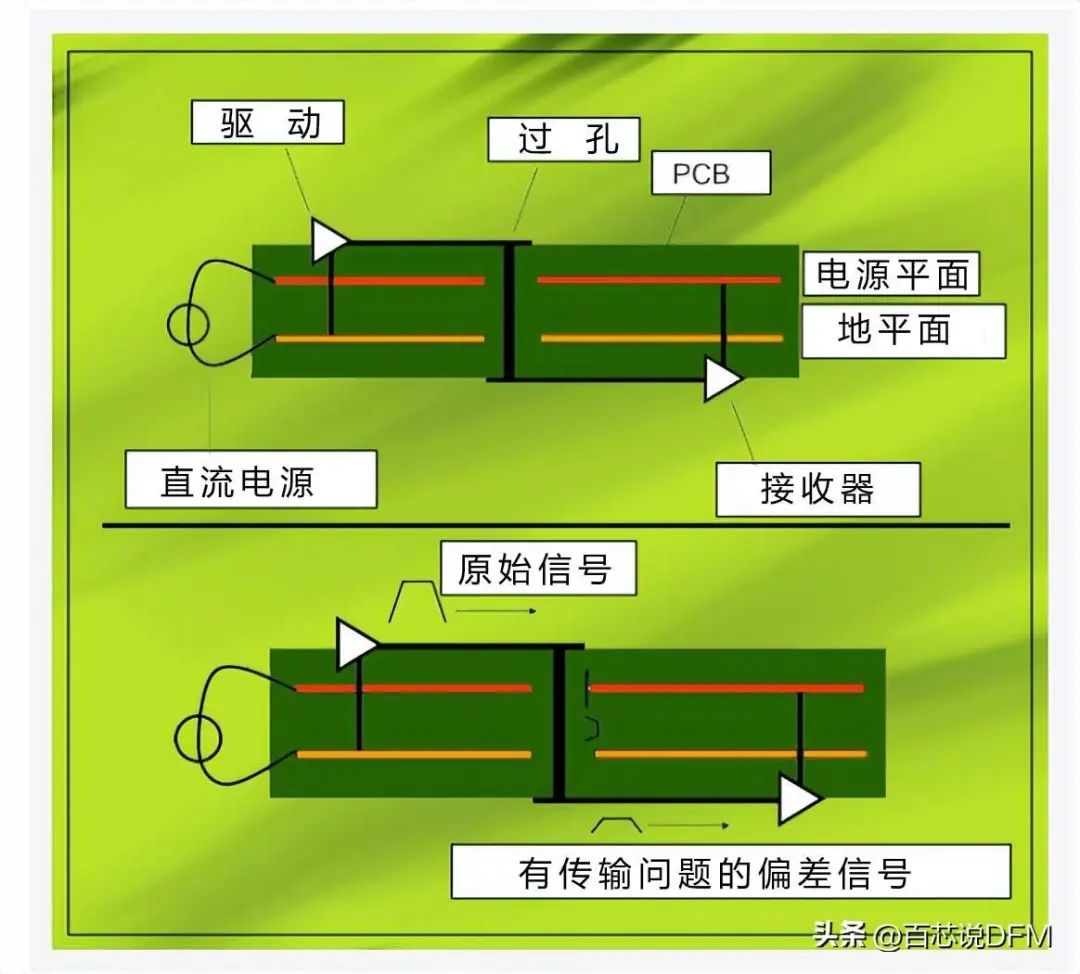

1.線寬的變化;2.層轉換;3、返回路徑平面上的間隙;4.接插件5.分支線,T型線或者樁線;6.網絡末端。

體會:需要注意的是網絡末端和接插件,網絡末端可以端接一個匹配同阻抗的電阻(引出問題為消耗額外功率,以及減少電流。電阻并接在網絡中,存在一個問題即電壓為源端電壓減去傳輸線分壓。電流為源電流減去各個分支電流。如果源端為電流驅動類型,則有可能導致接收端灌電流太小,驅動不了)接插件可以并接一個電容至地。)

定義:突變—令阻抗發生變化的所有特征稱之為突變。

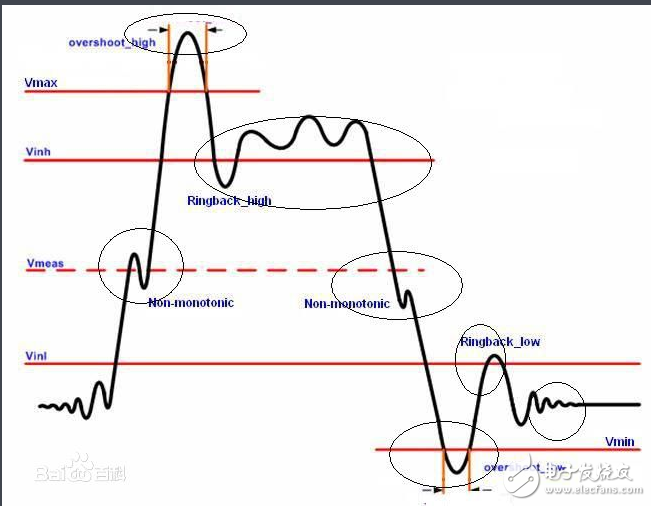

振鈴:通常認為是因為阻抗突變造成的反射引起的振鈴。

1. 如果把人比喻成信號,道路比喻成傳輸線,坑洼看做特征阻抗

---當人邁大步子(信號的上升時間》信號往返時間),道路上的的坑洼會被跳過,感覺不到,走的很順暢;當人邁著小碎步(信號的上升時間《信號往返時間),道路上的坑洼則不可避免的,這時走時會遇到很大阻力

---當不考慮外界干擾,如果道路保持一致(瞬態阻抗),人(信號)在道路上會保持恒定不變,如果道路出現坑洼(阻抗變化,中途遇到的電阻,電容,電感,過孔,PCB轉角,接插件),人(信號)在道路上速度就會發生改變(反射)

1.大多數高速數字系統中,信號上升時間約是時鐘周期的10%,即1/10x1/Fclock。例如100MHZ使中的上升時間大約是1NS.

2.在FR4板材上銅線條中信號速度為6in/ns(=15cm/ns)。

3.傳輸線的特征阻抗,只有當信號在走線上的往返時間大于信號的上升時間才考慮。

3.所有與信號完整性噪聲問題有關的效應都應與下面四類特定噪聲源中的一個:

(1)單一網絡的信號完整性;

在信號路徑或返回路徑上由于阻抗突變而引起的反射與失真。使信號感受到阻抗變化的情況。 例如振鈴問題就是由于信號傳輸過程中感受到阻抗的變化,發生的信號反射

(2)兩個或多個網絡間的串擾;

產生串擾的原因:正是網絡間的容性耦合和感性耦合,給有害噪聲從一個網絡到達另一個網絡提供了路徑

(3)電源和地分配中的軌道塌陷(旁路和去耦)---電感引起

當通過電源和地路徑的電流發生變化時,在電源路徑和地路徑間的阻抗上將產生一個壓降。這個壓降就意味著供給芯片的電壓減小了,可以看做是電源與地間的電壓減小或塌陷。這就是為啥要在芯片電源旁加個電容原因

電感--由于電流變化產生的感應電壓引起傳輸線效應,突變,串擾,開關噪聲,軌道塌陷,地彈和大大多數電磁干擾源(EMI)

(4)來自整個系統的電磁干擾和輻射。

電子發燒友App

電子發燒友App

評論