24c04的使用說明

1.引腳(見: 硬件接法)

讀寫命令

1 0 1 0 A2 A1 A0 R\w “1001”是AT24cxx 類型識別符(著種芯片的地址)

A2 A1 A0 掛在總線上不同芯片的地址(片選)W/R 0寫;1 讀2.

引腳說明:

A0~A2: 芯片的地址

SCL:時鐘信號線用于產(chǎn)生器件所有數(shù)據(jù)發(fā)送或接收的時鐘 在寫方式,SCL為高電平時, 數(shù)據(jù)必須保持穩(wěn)定。且下降沿送數(shù)。

SDA:數(shù)據(jù)信號線用于傳送地址和所有數(shù)據(jù)的發(fā)送和接受僅僅在SCL為低時數(shù)據(jù)才可以改變;

WP:寫保護接+5V時只能讀;接GND時即能寫也能讀;

3.時序

開始信號SCL為高電平時,SDA由高變底

停止信號SCL為高電平時,SDA由低變高

應(yīng)答信號接收數(shù)據(jù)的IC在接到第8BIT后(“寫”),發(fā)出特定的低電平脈沖,表示受到數(shù)據(jù)

操作步驟:

(1)”寫” 啟動總線(I方C)—發(fā)送器件尋址字節(jié)—應(yīng)答—發(fā)送數(shù)據(jù)尋址地址—回答—發(fā)送第一個數(shù)據(jù)—應(yīng)答--…………。發(fā)送第N個數(shù)據(jù)—應(yīng)答—停止總線; 寫地址可以指定第一個數(shù)據(jù)地址后連續(xù)送數(shù)。 “寫”分為字節(jié)寫和頁寫兩種方式。

(2)”讀”所有的操作幾乎一樣。只是在讀完8位數(shù)據(jù)以后,。從設(shè)備不是發(fā)出ACK(低電平),而是直接給SETB SDA ,然后發(fā)出停止總線信號即可結(jié)束本次讀。 讀也分為當前地址讀隨機讀和順序讀。

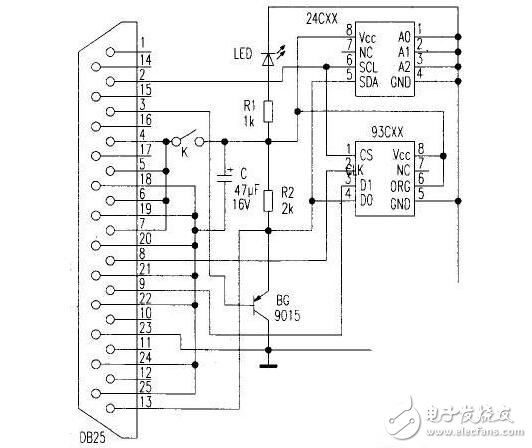

硬件接法

P1.0 接scl(6腳);

p1.1接sda(5腳);

4腳為GND; 8腳為VCC;

剩下的A2(3腳)A1(2腳) A0(1腳),T通過接VCC或GND以確定硬件的地址。 功能:顯示60H~63H中的數(shù)顯示24c04(60h~63h)讀到單片機60h~63h中顯示。

代碼

VSDA BIT P1.0

VSCL BIT P1.1

org 0000h

mov 60h,#00h

mov 61h,#00h

mov 62h,#00h

mov 63h,#00h

start: LCALL DISPLAY

LCALL DLE1

mov 60h,#01h

mov 61h,#02h

mov 62h,#03h

mov 63h,#04h

lcall write

lcall de

lcall read

lcall display

;############# 問題

asd: ajmp asd

;#############

ajmp start

STA: SETB VSDA

SETB VSCL

NOP

nop

nop

nop

CLR VSDA

NOP

clr vsda

nop

nop

nop

nop

CLR VSCL

RET

STOP: clr vsda

setb vscl

nop

nop

setb vsda

RET

WRBYT: MOV 17h,#08H;上升沿

WLP: RLC A

JC WR1

AJMP WR0

WLP1: DJNZ 17h,WLP

NOP

NOP

SETB VSCL

NN: MOV C,VSDA

JC NN

CLR VSCL

;call de

RET

WR1: setb vsda

setb vscl

NOP

NOP

nop

nop

clr VSCL

clr vsda

AJMP WLP1

WR0: CLR vsda

setb vscl

NOP

NOP

nop

nop

clr vscl

AJMP WLP1

rdbyt : mov 10h,#08h

rlp: setb vsda

setb vscl

mov c,vsda

rlc a

clr vscl

djnz 10h,rlp

nop

setb vsda

nop

nop

setb vscl

ret

WRITE: mov 15h,#4

mov 16h,#50h

mov r0,#60h

lcall sta

mov a,#0a0h

lcall wrbyt

mov a,16h

lcall wrbyt

wda: mov a,@r0

lcall wrbyt

;lcall de

inc r0

djnz 15h,wda

lcall stop

ret

read: mov 15h,#4

mov 16h,#50h

mov r0,#60h

ok: lcall sta

mov a,#0a0h

lcall wrbyt

mov a,16h

lcall wrbyt

lcall sta

mov a,#0a1h

lcall wrbyt

nop

lcall rdbyt

lcall stop

mov @r0,a

inc r0

inc 16h

djnz 15h,ok

ret mack: clr vsda

setb vscl

nop

nop

clr vscl

setb vsda

ret

mnack: setb vsda

setb vscl

nop

nop

clr vsda

clr vscl

ret

display:mov dptr,#tab1

mov a,60h;4

movc a,@a+dptr

mov 13h,a

mov dptr,#tab1

mov a,61h;3

movc a,@a+dptr

mov 12h,a

mov dptr,#tab1

mov a,62h;2

movc a,@a+dptr

mov 11h,a

mov dptr,#tab1

mov a,63h;高

movc a,@a+dptr

mov 10h,a

ACALL DISP RET

disp: clr p1.5

clr p1.4

MOV 16H,#4

mov r1,#13h

dir1x:acall shift;senddata

dec r1

djnz 16H,dir1x

setb p1.5;first finish

nop

NOP

clr p1.5

RET

shift: mov a,@r1;

mov 15H,#08h acall yw

RET

yw: RRC A

MOV P1.3,C

SETB P1.4

NOP

NOP

NOP

CLR P1.4

DJNZ 15H,yw

MOV 15H,#08H

RET

tab1: db 0fch,60h,0dah,0f2h,66h,0b6h,0beh,0e0h,0feh,0f6h

DE: MOV 40H,#08H

DE3: MOV 41H,#0a0H

DE2: MOV 42H,#01H

DE1: DJNZ 42H,DE1

DJNZ 41H,DE2

dJNZ 40H,DE3

RET

DLE1: MOV 40H,#08H

DE31: MOV 41H,#0FFH

DE21: MOV 42H,#0FFH

DE11: DJNZ 42H,DE11

DJNZ 41H,DE21

dJNZ 40H,DE31

RET

END

電子發(fā)燒友App

電子發(fā)燒友App

評論