隨著數字技術的飛速發展, 用數字控制方法從一個參考頻率源產生多種頻率的技術, 即直 接數字頻率合成(DDS) 技術異軍突起。美國AD 公司推出的高集成度頻率合成器AD9850便 是采用DDS 技術的典型產品之一。

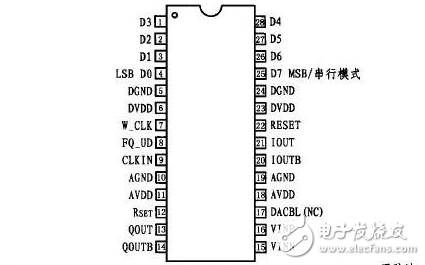

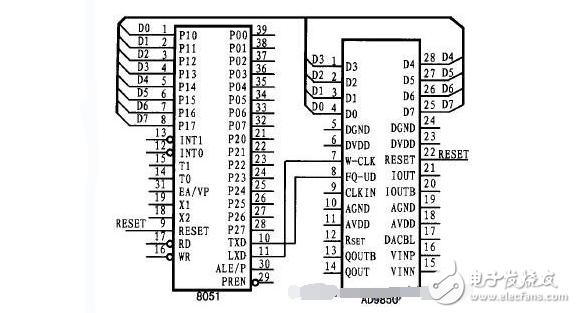

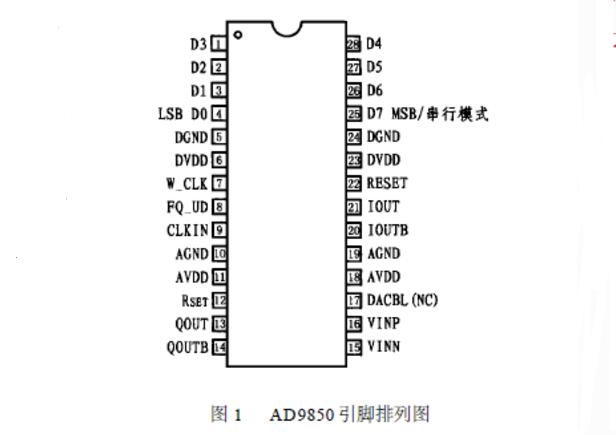

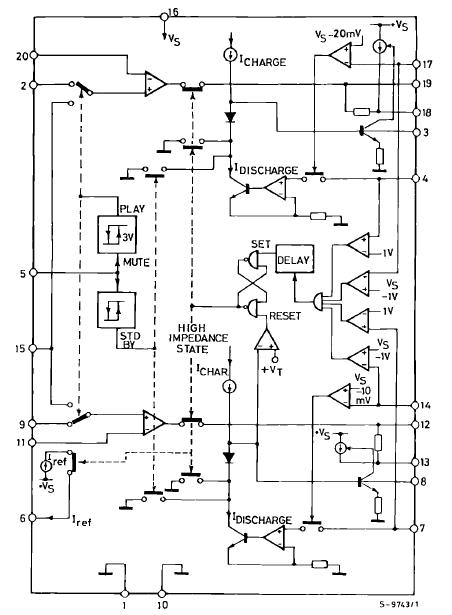

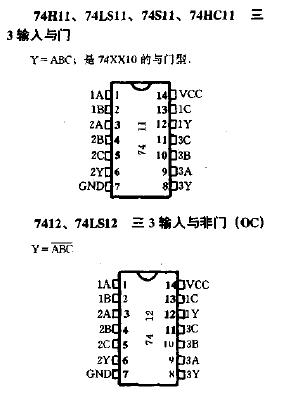

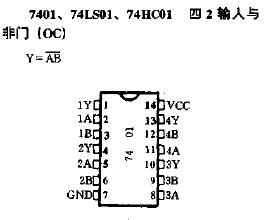

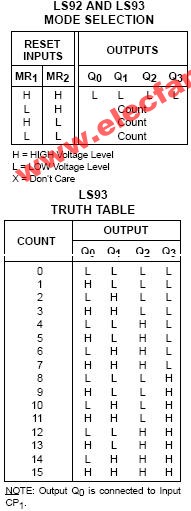

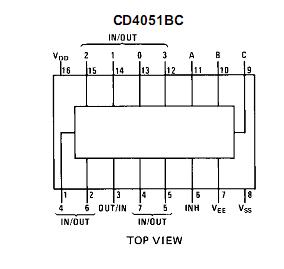

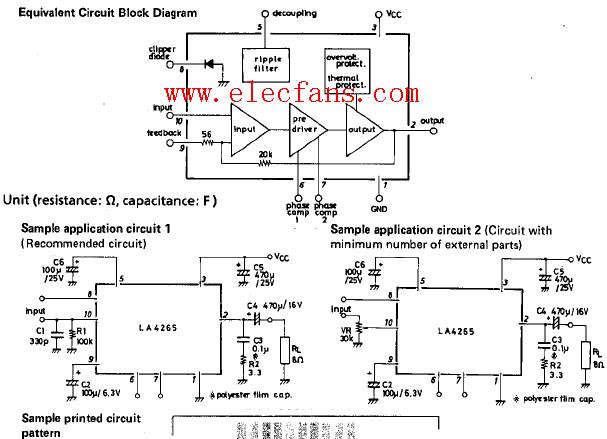

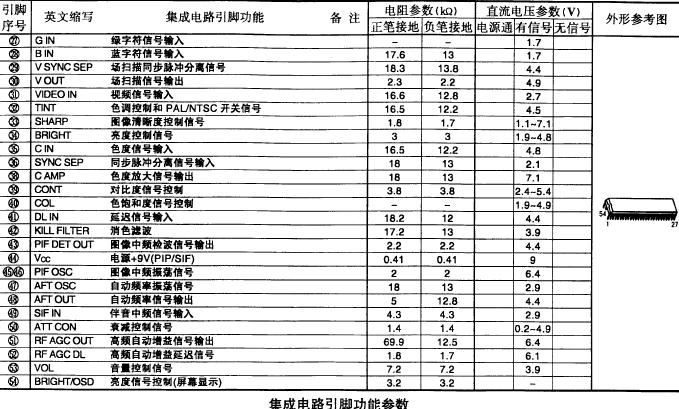

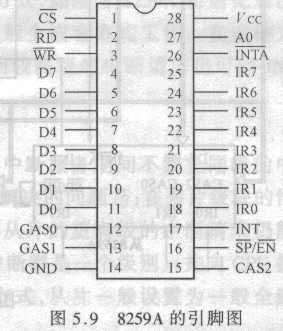

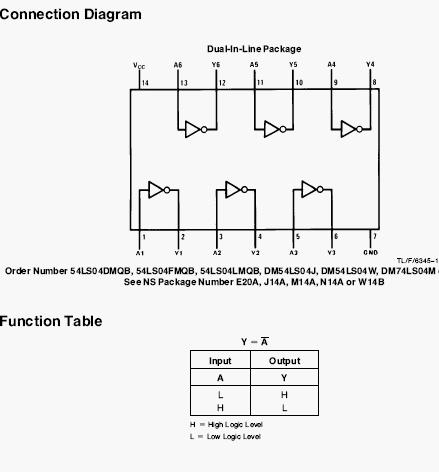

AD9850采用先進的CMOS工藝, 其功耗在3.3V 供電時僅為155mW,擴展工業級溫度范圍 為- 40~ 80 ℃, 采用28腳SSOP表面封裝形式。AD9850的引腳排列及組成框圖如圖1所示。圖1 中層虛線內是一個完整的可編程DDS 系統,外層虛線內包含了AD9850 的主要組成部分。

圖1 AD9850引腳圖

AD9850 內含可編程DDS 系統和高速比較器,能實現全數字編程控制的頻率合成。可編程 DDS 系統的核心是相位累加器, 它由一個加法器和一個N位相位寄存器組成, N 一般為24 ~32。每來一個外部參考時鐘,相位寄存器便以步長M 遞加。相位寄存器的輸出與相位控 制字相加后可輸入到正弦查詢表地址上。正弦查詢表包含一個正弦波周期的數字幅度信息 , 每一個地址對應正弦波中0°~360°范圍的一個相位點。查詢表把輸入地址的相位信息 映射成正弦波幅度信號, 然后驅動DAC 以輸出模擬量。

相位寄存器每過2N/ M 個外部參考時鐘后返回到初始狀態一次, 相應地正弦查詢表每經過 一個循環也回到初始位置, 從而使整個DDS 系統輸出一個正弦波。輸出的正弦波周期TO = Tc2N/ M , 頻率fout = Mfc/ 2N ,Tc 、fc 分別為外部參考時鐘的周期和頻率。

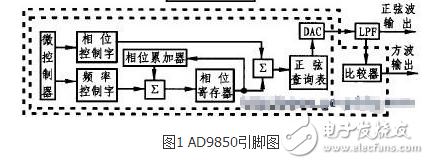

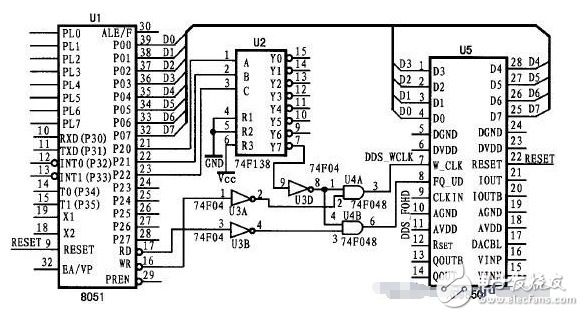

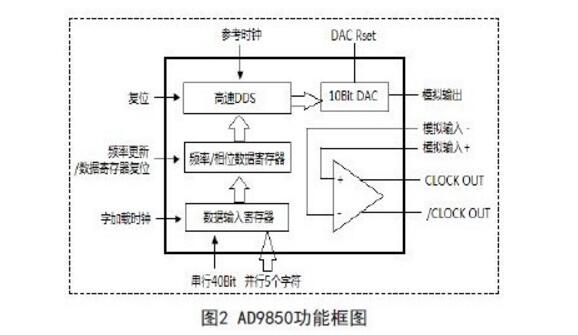

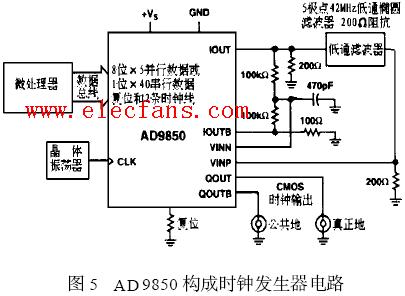

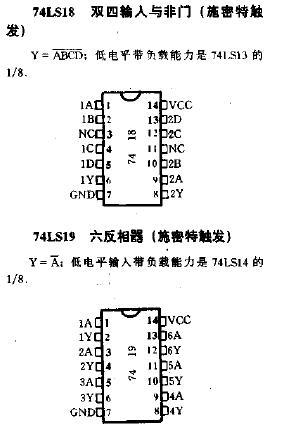

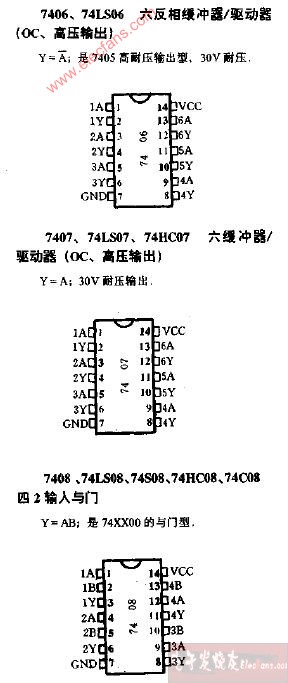

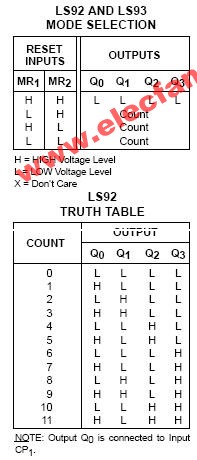

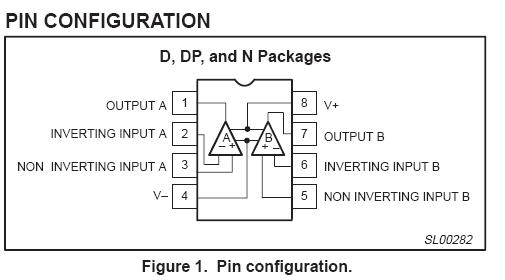

AD9850 采用32 位的相位累加器將信號截斷成14 位輸入到正弦查詢表,查詢表的輸出再被 截斷成10 位后輸入到DAC , DAC 再輸出兩個互補的電流。DAC 滿量程輸出電流通過一個 外接電阻RSET調節, 調節關系為ISET = 32 (1. 248V/ RSET) , RSET的典型值是3. 9kΩ 。將DAC 的輸出經低通濾波后接到AD9850 內部的高速比較器上即可直接輸出一個抖動很 小的方波。其系統功能如圖2所示。

圖2 AD9850 的系統功能框圖

AD9850 在接上精密時鐘源和寫入頻率相位控制字之后就可產生一個頻率和相位都可編程 控制的模擬正弦波輸出, 此正弦波可直接用作頻率信號源或經內部的高速比較器轉換為方 波輸出。在125MHz 的時鐘下, 32 位的頻率控制字可使AD9850 的輸出頻率分辨率達0. 0291Hz ; 并具有5位相位控制位,而且允許相位按增量180°、90°、45°、22. 5°、11. 25°或這些值的組合進行調整。

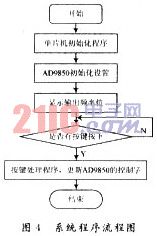

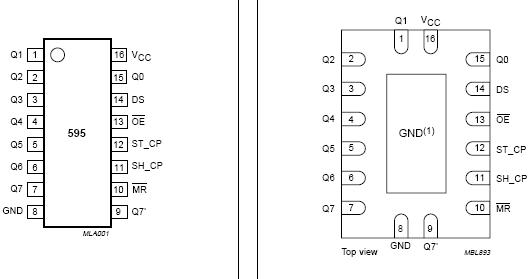

2、AD9850 的控制字與控制時序

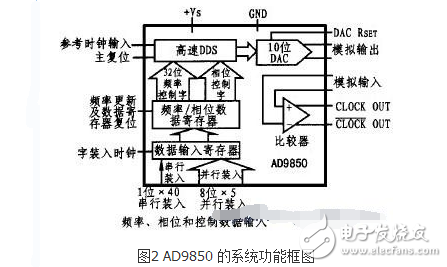

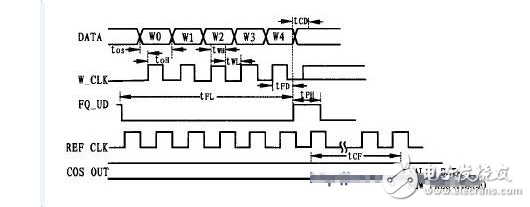

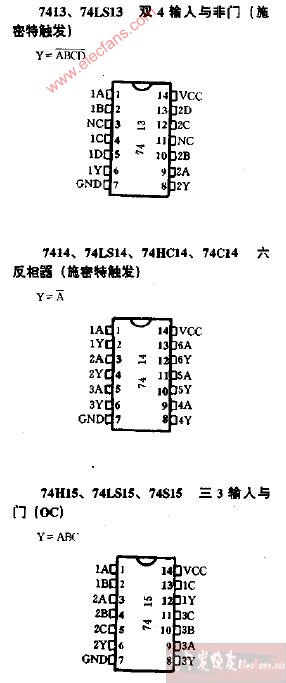

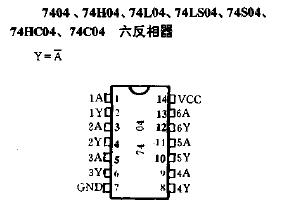

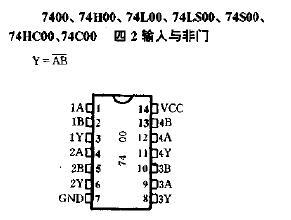

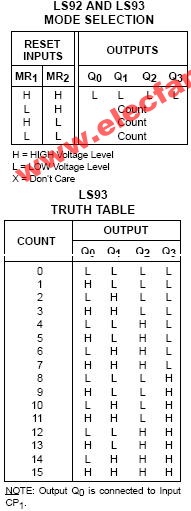

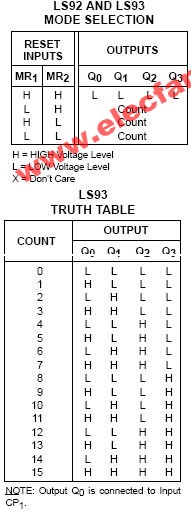

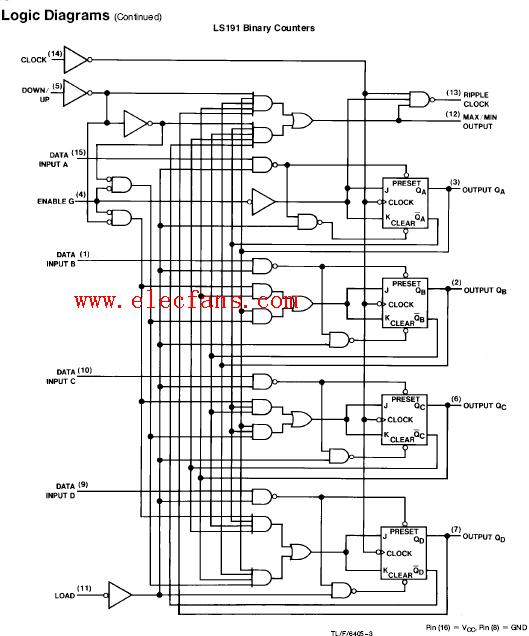

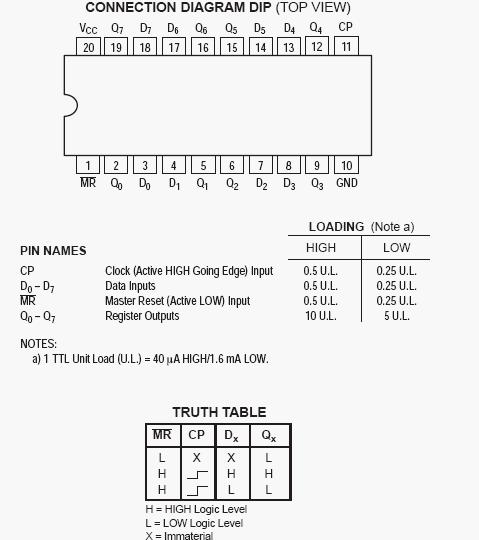

AD9850 有40 位控制字, 32 位用于頻率控制,5 位用于相位控制, 1 位用于電源休眠( Power down) 控制, 2 位用于選擇工作方式。這40 位控制字可通過并行方式或串行方式 輸入到AD9850 ,圖3是控制字并行輸入的控制時序圖, 在并行裝入方式中,通過8 位總線D0 ……D7 將可數據輸入到寄存器,在重復5 次之后再在FQ – UD 上升沿把40 位數據從輸入 寄存器裝入到頻率/ 相位數據寄存器(更新DDS 輸出頻率和相位) , 同時把地址指針復位 到第一個輸入寄存器。接著在W – CL K 的上升沿裝入8位數據,并把指針指向下一個輸入 寄存器,連續5 個W – CL K 上升沿后, W – CL K 的邊沿就不再起作用,直到復位信號或FQ - UD 上升沿把地址指針復位到第一個寄存器。在串行輸入方式, W – CL K 上升沿把25 引腳的一位數據串行移入, 當移動40 位后, 用一個FQ-UD 脈沖即可更新輸出頻率和相位 。圖4 是相應的控制字串行輸入的控制時序圖。

圖3 AD9850控制字并行輸入的時序圖

圖4 AD9850控制字串行輸入的時序圖

AD9850 的復位(RESET) 信號為高電平有效,且脈沖寬度不小于5 個參考時鐘周期。AD9850 的參考時鐘頻率一般遠高于單片機的時鐘頻率, 因此AD9850 的復位(RESET) 端可與單片 機的復位端直接相連。

值得一提的是: 用于選擇工作方式的兩個控制位,無論并行還是串行最好都寫成00 ,并行 時的10、01 和串行時的10、01、11 都是工廠測試用的保留控制字,不慎使用可能導致難 以預料的后果。

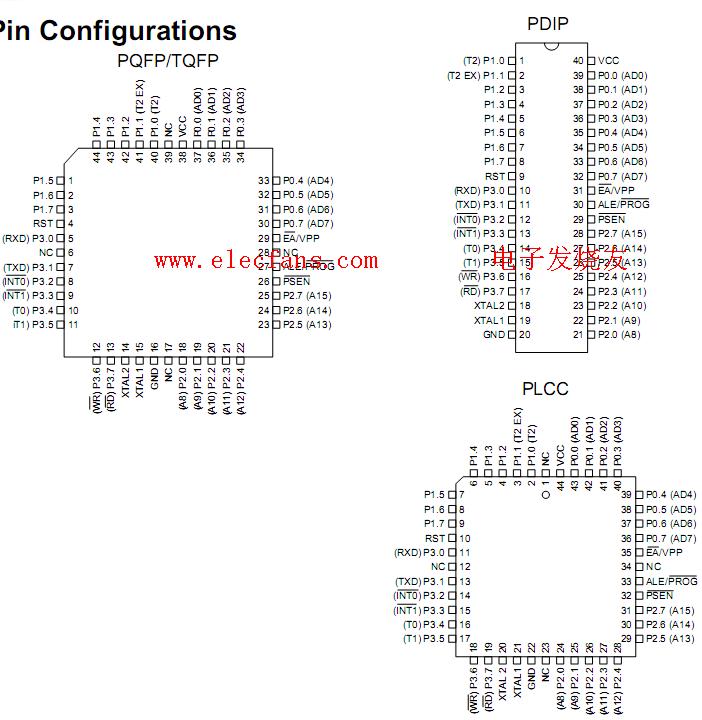

3、單片機與AD9850 的接口

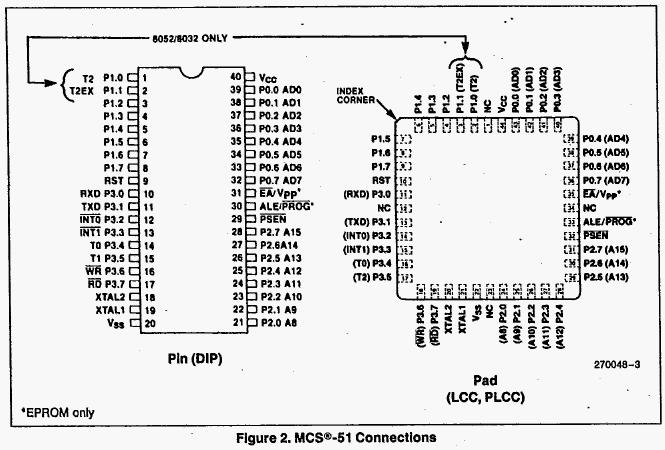

AD9850 有兩種與微機并行打印口相連的評估版, 并配有Windows 下運行的軟件, 可以作 為應用參考,但運用單片機實現對DDS 的控制與微機實現的控制相比,具有編程控制簡便、 接口簡單、成本低,容易實現系統的小型化等優點, 因此普遍采用MCS51 單片機作為控制 核心來向AD9850 發送控制字。

單片機與AD9850 的接口既可采用并行方式,也可采用串行方式, 但為了充分發揮芯片的高 速性能, 應在單片機資源允許的情況下盡可能選擇并行方式,本文重點介紹其并行方式的 接口。

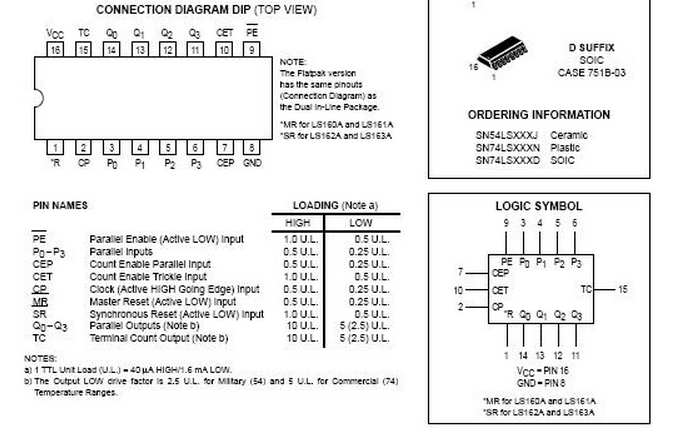

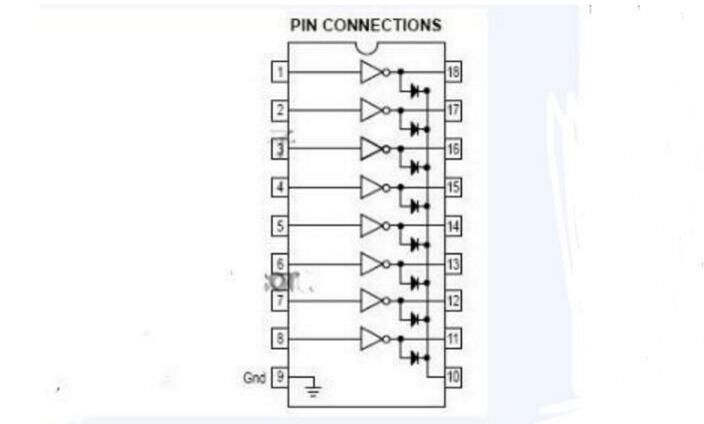

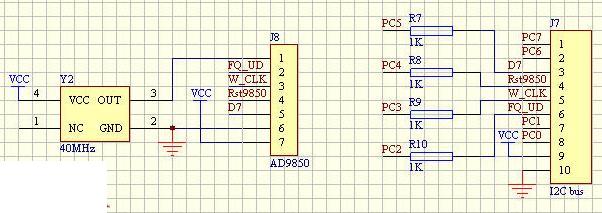

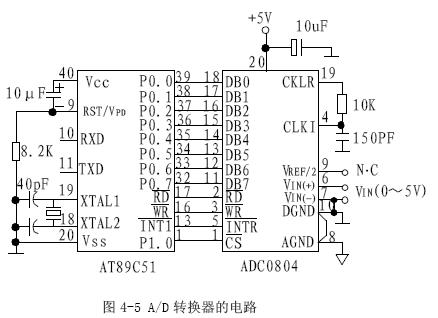

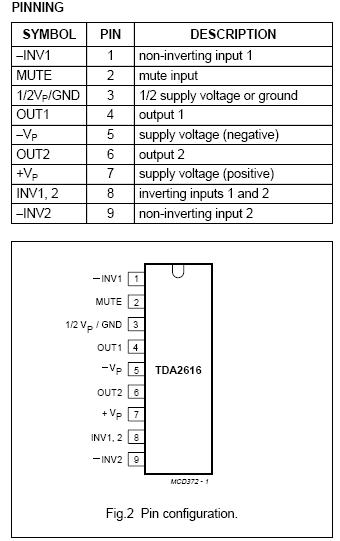

3. 1 I/ O 方式并行接口

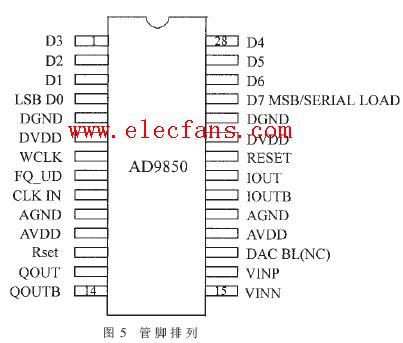

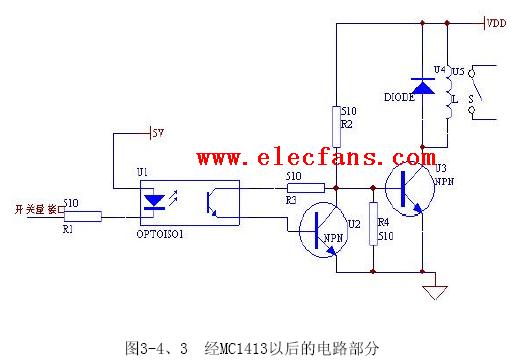

I/ O 方式的并行接口電路比較簡單, 但占用單片機資源相對較多, 圖5 是I/ O 方式并行 接口的電路圖,AD9850 的數據線D0~D7 與P1 口相連, FQ-UD和W-CL K 分別與P3. 0 (10 引腳) 和P3. 1 (11 引腳) 相連, 所有的時序關系均可通過軟件控制實現。

圖5 AD9850與單片機并行I/ O 方式接口電路圖

將DDS 控制字從高至低存放于30H 至34H 中,發送控制字的程序清單如下:

MOV R0 , # 05H

MOV R1 , # 30H

DD : MOV P1 , @R1

SETB P3. 1

CLR P3. 1

INC R1

DJNZ R0 ,DD

SETB P3. 0

CLR P3. 0

END

在程序中, 每將一字節的數據送到P1 口后, 必須將P3. 1 (W-CL K) 置高。在其上升 沿,AD9850 接收與P1 口相連的數據線上的數據, 然后將P3. 1 置低, 并準備下一字節的 發送, 連續發送5 個字節后,須將P3. 0 ( FQ-UD) 再次置高, 以使AD9850 根據剛輸入的 控制字更改頻率和相位輸出, 隨后再置P3. 0 為低,準備下一組發送。單片機的P3. 0、 P3. 1引腳為串行口, 當被占用時, W-CL K 和FQ-UD 引腳也可與其它I/ O 腳相連, 這時需要修改相應的發送程序。

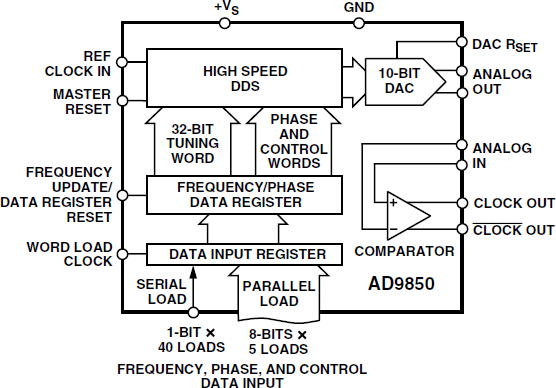

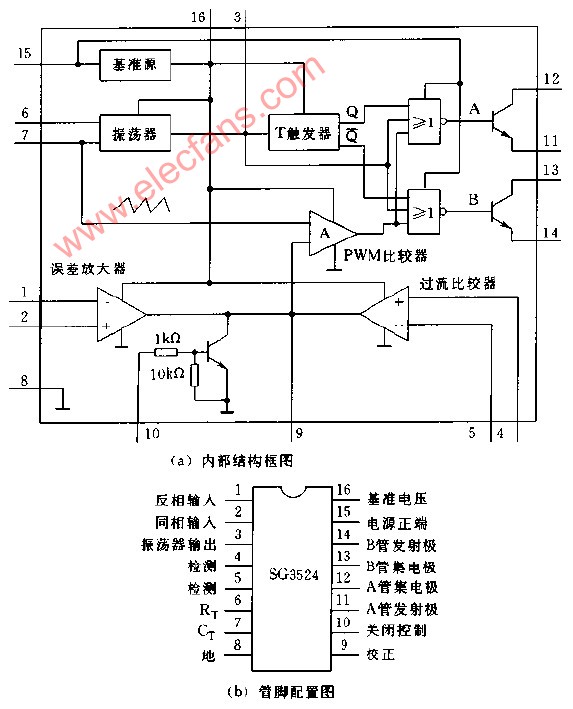

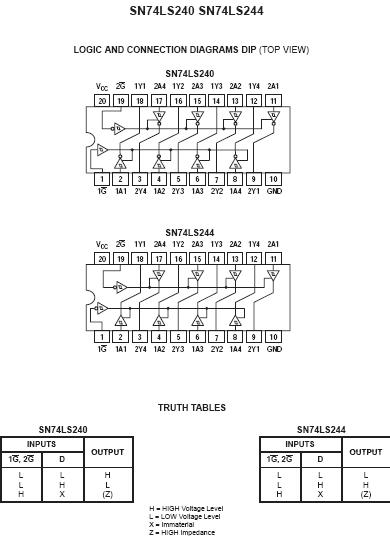

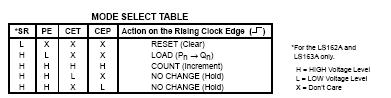

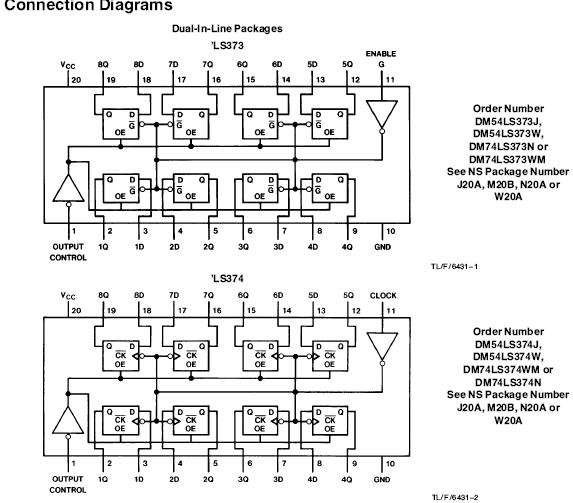

3. 2 總線方式并行接口

總線方式并行接口占用的單片機資源較少, 在這種方式下, AD9850 僅作為一擴展芯片而 占用外部RAM 的一段地址, 必要時也可以只占用一個地址。圖6 是總線方式并行接口的電 路原理圖。同樣將DDS 控制字從高至低存放于30H 至34H 中, 發送控制字的程序清單如下:

圖6 AD9850總線方式并行方式接口的電路原理圖

MOV R0 , # 05H

MOV R1 , # 30H

MOV DPTR , #0700H

DD : MOV A , @R1

MOVX @DPTR ,A

INC R1

DJNZ R0 ,DD

MOVX A , @DPTR

END

AD9850 的W-CL K 和FQ-UD 信號都是上升沿有效, 用MOVX @DPTR , A 指令向AD9850 傳送控制字時, 由74F138 將高八位地址的低三位譯碼, 其輸出經反相并與反相后的信號相 與得到一上升沿送至AD9850 的W-CL K 腳, 此時已送到總線上的數據將被AD9850 接收,連 續五次將40 位的控制字全部發送以后,用MOVX A , @DPTR 指令產生FQ-UD 信號, 使 AD9850 更改輸出頻率和相位,此時讀入到單片機內的數據實際上無任何意義。圖6中 AD9850 的地址為0700H。

上述兩種接口方式經實際應用證明:工作可靠,效果良好。單片機與AD9850 的串行接口可 參照有關資料進行設計。上述接口電路和程序也適用于與AD9850 腳對腳兼容的AD9851 , 值得注意的是:AD9851 的控制字與AD9850 控制字中個別位的定義稍有區別,編程時應予以 注意。

電子發燒友App

電子發燒友App

評論